本篇注释比较详细,由《Moselsim 第一个仿真程序 四位加法器》修改而来

原博客:https://blog.youkuaiyun.com/sinat_42483341/article/details/88970852

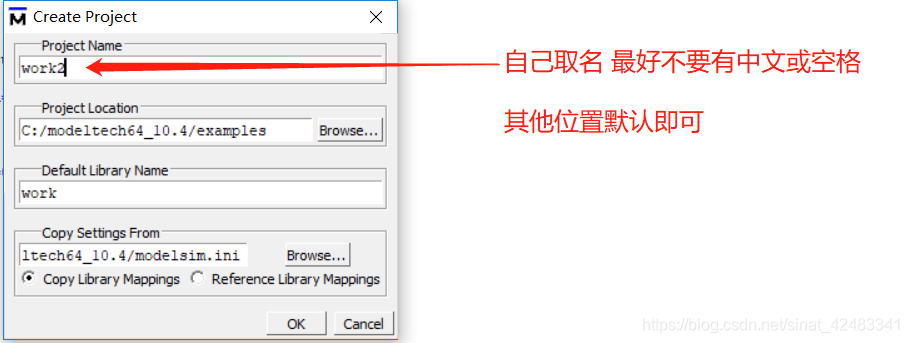

新建项目步骤:

1、File->New->Project

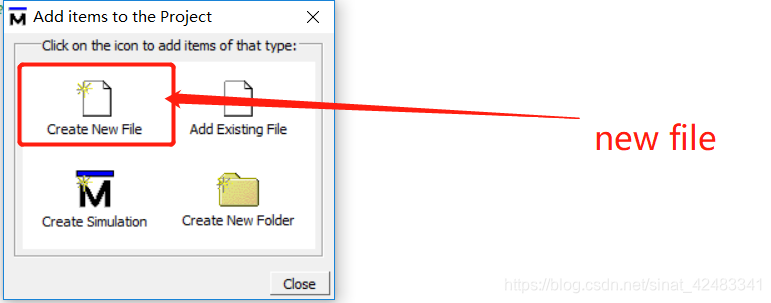

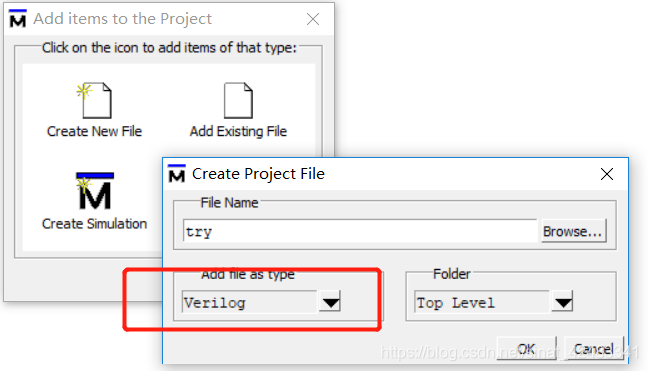

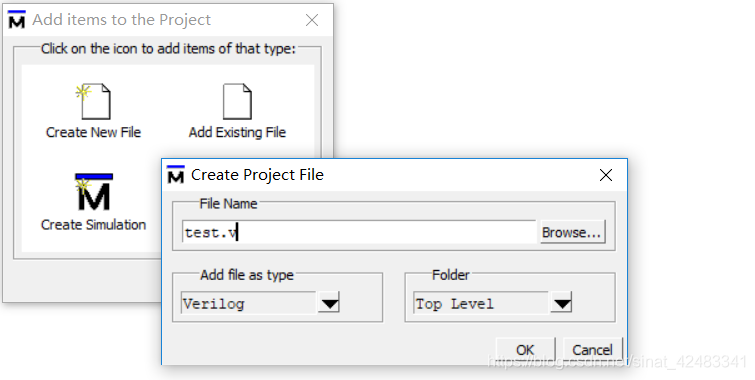

分别创建两个verilog文件

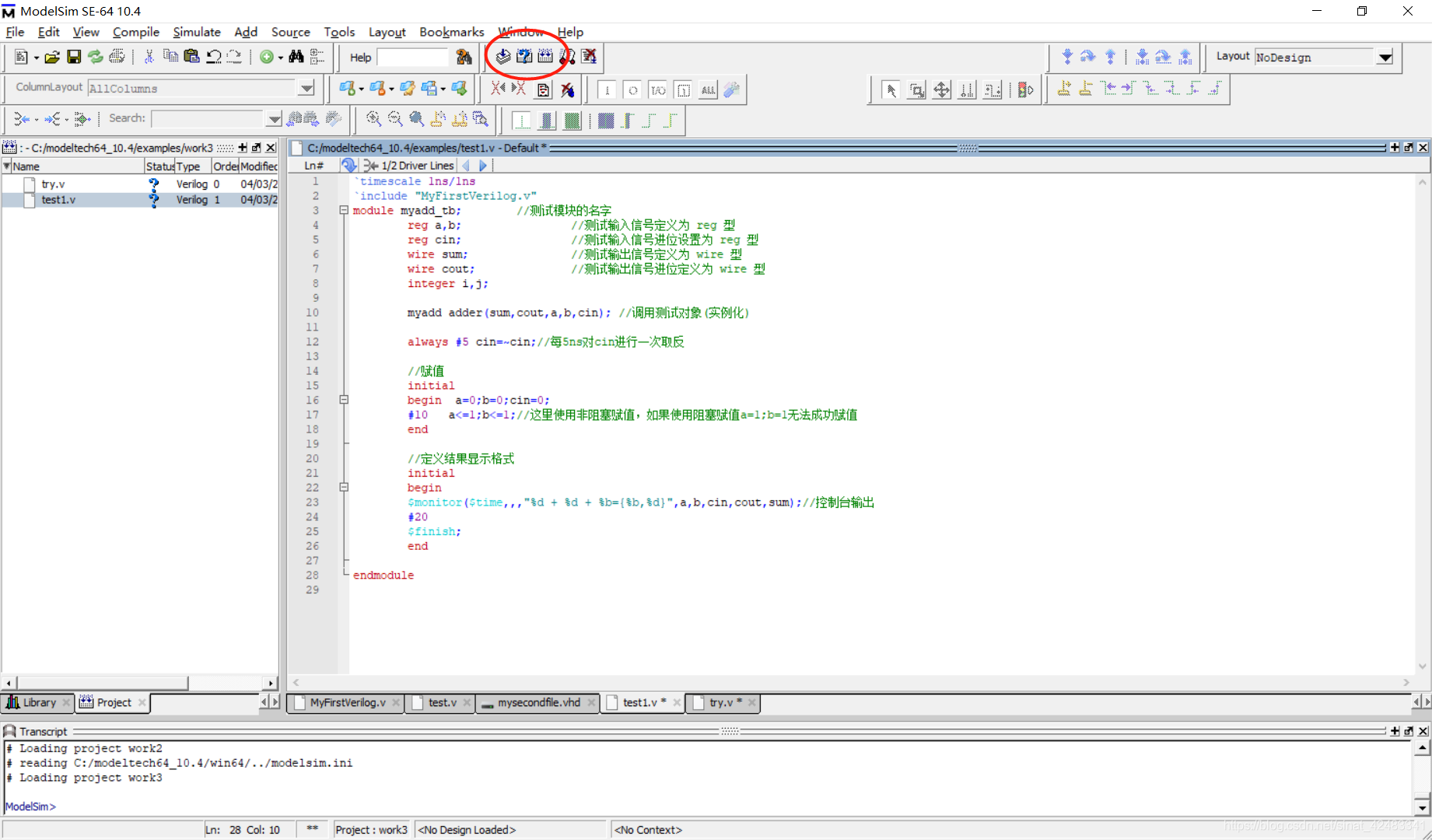

填写代码(可以复制这篇下面的源程序),保存后编译全部

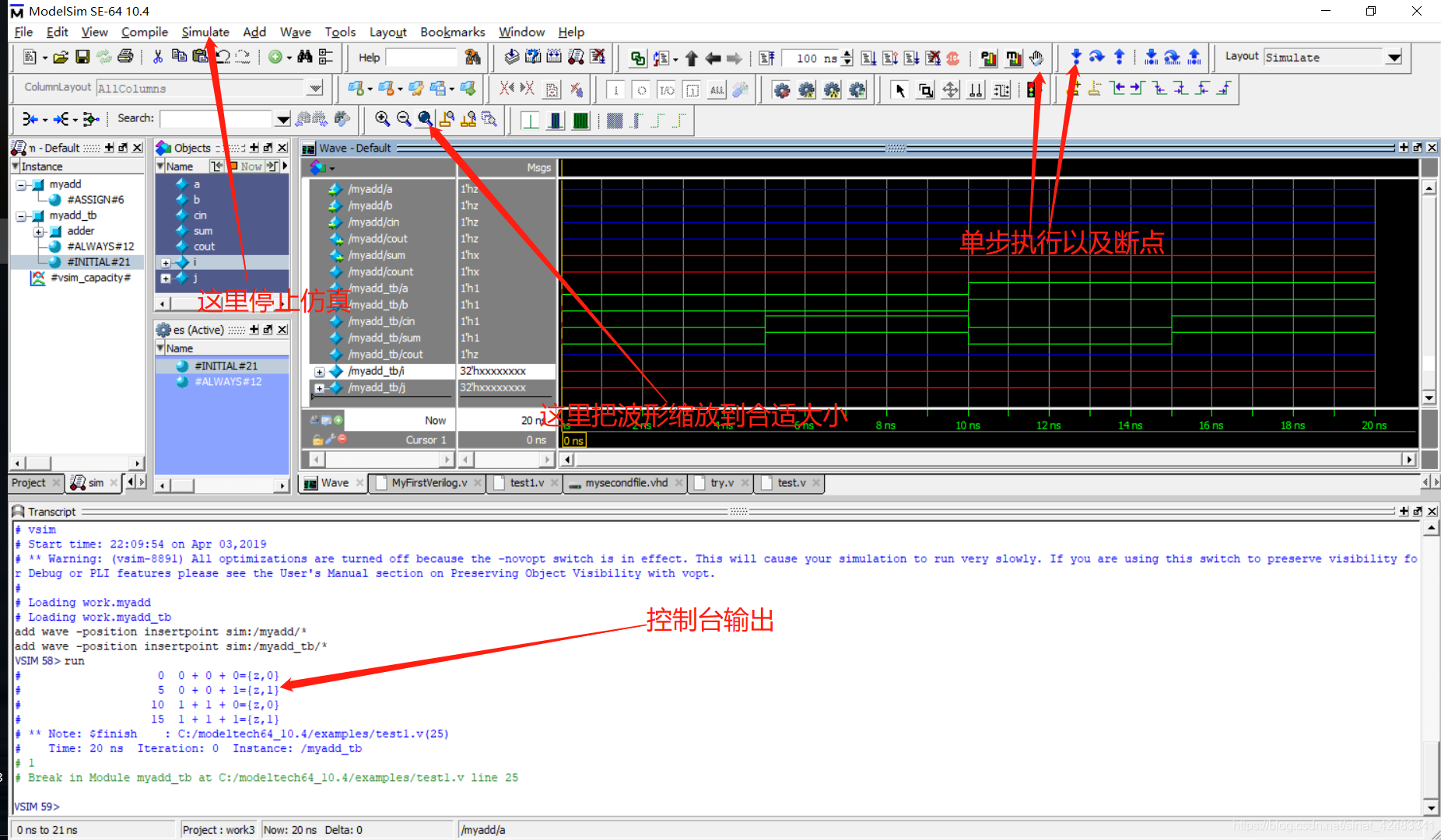

下面这个控制台输出说明没有bug,如果有bug,双击错误信息,会定位到错误所在行

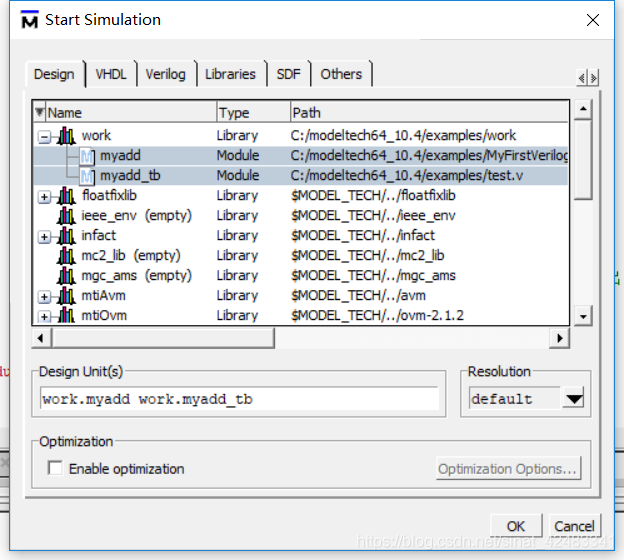

simulate->start simulation,在work下选择刚写的两个文件

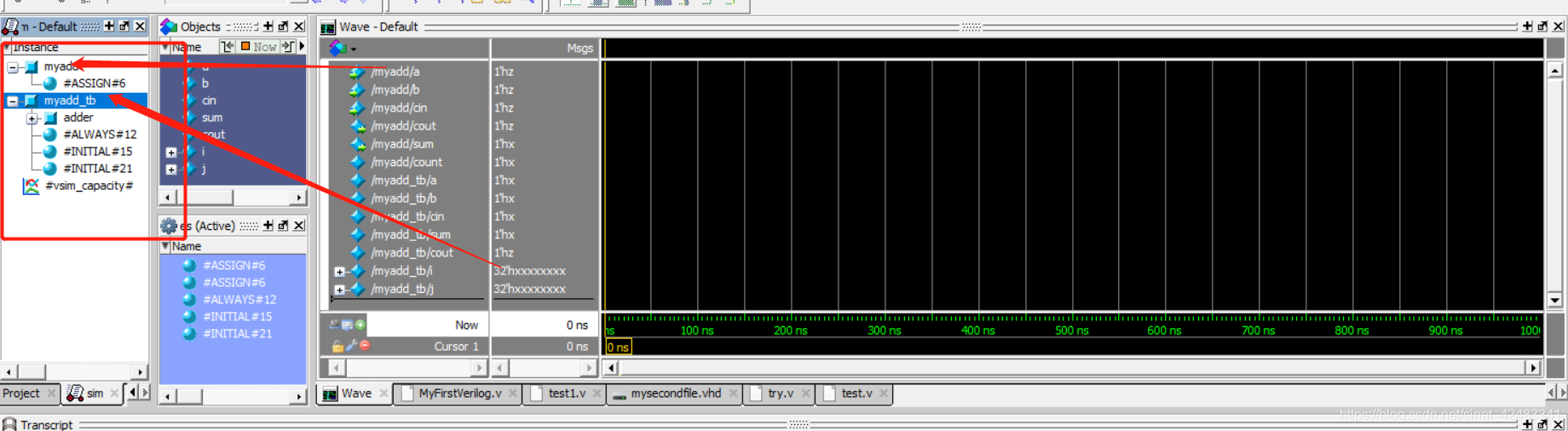

右键单击这两个,分别“add wave”

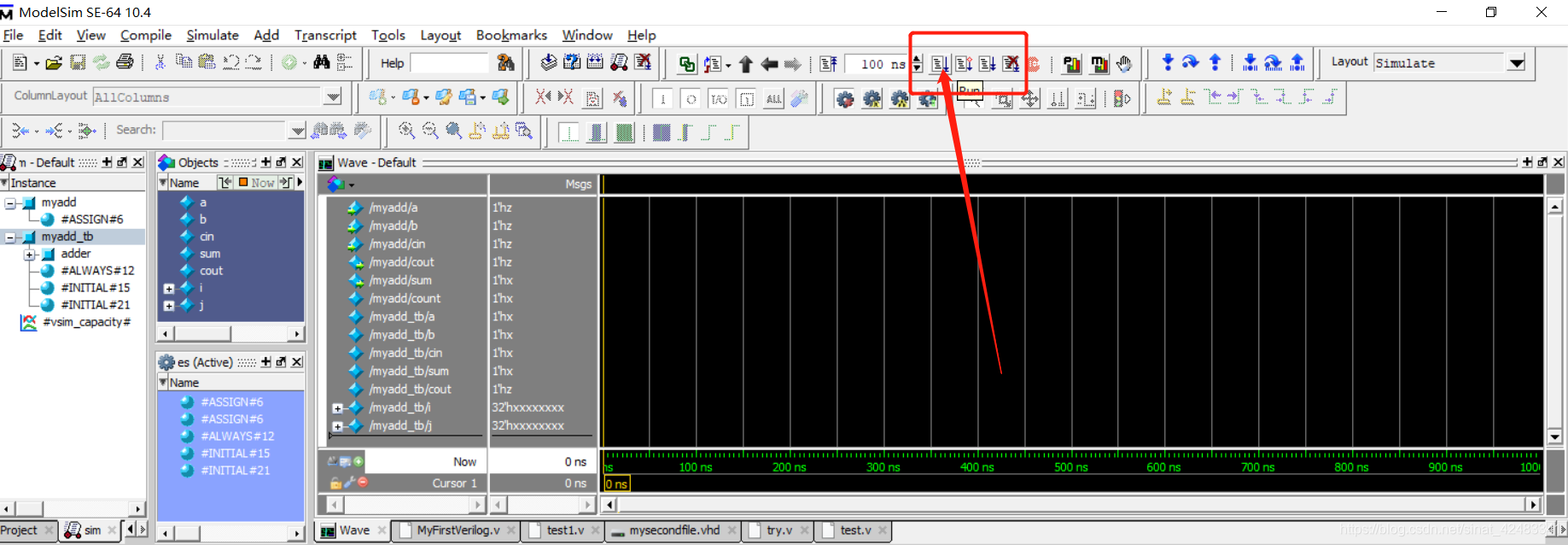

点这个run

箭头中标注了一些常用的功能,至此,仿真教程结束。

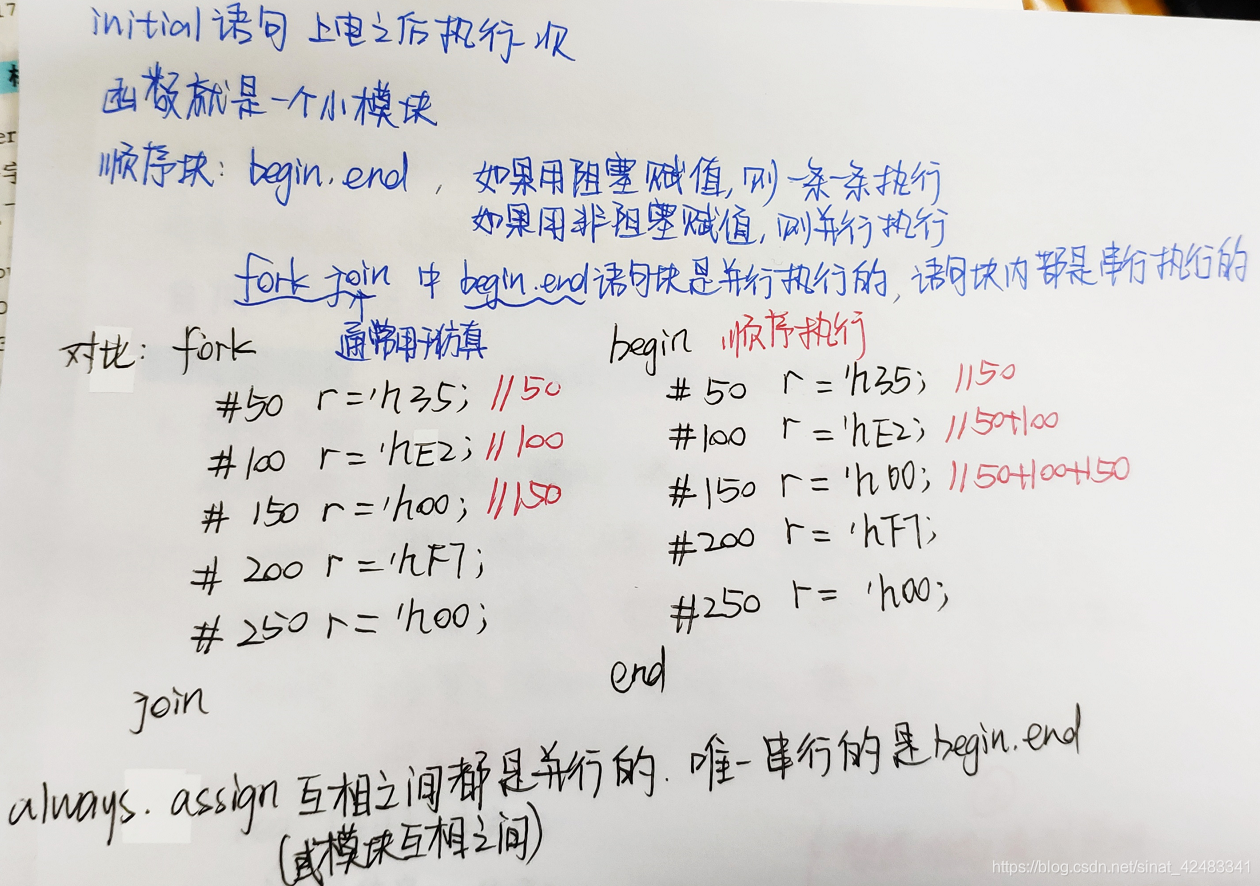

关于begin end 串行并行的易错点

代码一

源程序

//source program

module myadd(sum,cout<

本文详细介绍如何使用Verilog实现一位加法器,并通过两个不同的仿真程序验证其正确性。文章提供了完整的代码示例,包括模块定义、仿真测试、波形观察及控制台输出结果。

本文详细介绍如何使用Verilog实现一位加法器,并通过两个不同的仿真程序验证其正确性。文章提供了完整的代码示例,包括模块定义、仿真测试、波形观察及控制台输出结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?