,以单道批处理方式运行;按短作业优先算法调度;计算作业的平均周转时间和带权平均周转时间

分析:

作业 进入时间 运行时间 开始时间 完成时间 周转时间 带权周转时间

job1 8.0 2.0 10.0 12. 0 4.0 2

job2 8.0 1.0 8.0 9.0 1.0 1

job3 8.4 0.7 9.0 9.7 1.3 1.86

job4 9.2 0.3 9.7 10.0 0.8 2.67

平均周转时间=(4.0+1.0+1.3+0.8)/4=1.775

带权平均周转时间=(2+1+1.86+2.67)/4=1.88

注:周转时间=完成时间-进入时间

带权周转时间=周转时间/运行时间

2.

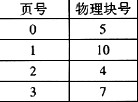

某虚拟存储器的用户编程空间共32个页面,每页为1KB,内存为16KB。假定某时刻一用户页表中已调入内存的页面的页号和物理块号的对照表如下:

则逻辑地OA5C(H)所对应的物理地址是(23)。

A.125C(H)

B.135 C(H)

C.127 C(H)

D.120 C(H)

分析:共2^5*2^10=2^15 有15位地址位则 页号:00010 = 2---物理块4----00100

实际地址----001001001011100--125C

3.段页式地址转换

4.3. 地址映射(逻辑地址--->物理地址)

³ 逻辑地址----- >段号、段内页号、业内地址

³ 段表寄存器--- >段表始址

³ 段号+段表始址---- >页表始址

³ 页表始址+段内页号----->存储块号

³ 块号+页内地址------>物理地址

段页式管理每一次数据要访问几次内存?

一般需要访问三次以上的内存: 第一次是由段表地址寄存器得段表始址后访问段表,由此取出对应段的页表在内存中的地址。 第二次则是访问页表得到所要访问的物理地址。 第三次才能访问真正需要访问的物理单元。(3) 逻辑地址结构。一个逻辑地址用三个参数表示:段号S;页号P;页内地址d。

逻辑地址结构

5.

SPOOLing技术

6.一个计算机系统的虚拟存储器的最大容量是由 (1)确定的,其实际容量还要受到 (2)的影响。

A.CPU地址长度

B.内存容量

C.硬盘容量

D.内存和硬盘容量之和

最大容量=地址位数决定

7.

在操作系统中什么情况下引发进程调度

-

正在执行的程序执行完毕,或因某种事件而不能再继续执行

-

执行的进程因提出I/O请求而暂停执行

-

在进程通行或同步过程中执行了某种原语操作,如P操作,block原语,wakeup原语。

物理块中,相对地址2500处有一条指令Store 1,4500 , 请给出该作业的页表,该指令的物理单元和数据存

放的物理单元.

分析:

页表

虚页号 物理块号

0 2

1 3

2 6

该指令的物理单元(实际上就是求2500这个相对地址对应的绝对地址 这其中要用到上面的页表)

19C4H-->6596(十进制)

数据存放的物理单元(就是4500对应的绝对地址)

3194H-->12692(十进制)

方法2:2500/(1024*2) = 1........452

1----3 ,则 3*1024*2 + 452 = 6596

9.

在DMA方式下,CPU与总线的关系是__

2.只能控制地址总线

3.成隔离状态

4.成段接状态

分析:DMA 是所有现代电脑的重要特色,他允许不同速度的硬件装置来沟通,而不需要依于 CPU 的大量 中断 负载。否则,CPU 需要从 来源 把每一片段的资料复制到暂存器,然后把他们再次写回到新的地方。在这个时间中,CPU 对于其他的工作来说就无法使用。

DMA 传输将一个内存区从一个装置复制到另外一个, CPU 初始化这个传输动作,传输动作本身是由 DMA控制器来实行和完成。典型的例子就是移动一个外部内存的区块到芯片内部更快的内存去。像是这样的操作并没有让处理器工作拖延,反而可以被重新排程去处理其他的工作。DMA 传输对于高效能嵌入式系统算法和网络是很重要的。

举个例子,PC ISA DMA控制器拥有 8 个 DMA 通道,其中的 7 个通道是可以让 PC 的 CPU 所利用。每一个 DMA 通道有一个 16位元 位址暂存器和一个 16 位元计数暂存器。要初始化资料传输时,装置驱动程式一起设定 DMA 通道的位址和计数暂存器,以及资料传输的方向,读取或写入。然后指示 DMA 硬件开始这个传输动作。当传输结束的时候,装置就会以中断的方式通知 CPU。

但是,DMA传输方式只是减轻了CPU的工作负担;系统总线仍然被占用。特别是在传输大容量文件时,CPU的占用率可能不到10%,但是用户会觉得运行部分程序时系统变得相当的缓慢。主要原因就是在运行这些应用程序(特别是一些大型软件),操作系统也需要从系统总线传输大量数据;故造成过长的等待时间。

数据传输路径为; 外设--总线--dmac--主存

10.

risc一定是指令流水。

分析:加强了处理器并行能力:RISC指令集能够非常有效地适合于采用流水线、超流水线和超标量技术,从而实现指令级并行操作,提高处理器的性能。

RISC,精简指令集计算机,相较于CISC(复杂指令集计算机),由于精简掉80%左右的复杂指令,流水线短,并发行更强,效率更高11.

时钟周期

时钟周期也称为振荡周期,定义为时钟脉冲的倒数(时钟周期就是单片机外接晶振的倒数,例如12M的晶振,它的时钟周期就是1/12us),是计算机中的最基本的、最小的时间单位。

在一个时钟周期内,CPU仅完成一个最基本的动作。时钟脉冲是计算机的基本工作脉冲,控制着计算机的工作节奏。时钟频率越高,工作速度就越快。

8051单片机把一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。

机器周期

计算机中,常把一条指令的执行过程划分为若干个阶段,每一个阶段完成一项工作。每一项工作称为一个基本操作,完成一条指令的基本操作所需要的时间称为机器周期。8051系列单片机的一个机器周期由6个S周期(状态周期)组成。 一个S周期=2个节拍(P),所以8051单片机的一个机器周期=6个状态周期=12个时钟周期。

例如外接24M晶振的单片机,他的一个机器周期=12/24M 秒;

指令周期

执行一条指令所需要的时间,一般由若干个机器周期组成。指令不同,所需的机器周期也不同。

补充其他几个周期:

时钟周期:处理操作的最基本单位。(CPU的主频)

存储周期:也就是一个访存指令周期。

指令周期、机器周期和时钟周期之间的关系:指令周期通常用若干个机器周期表示,而机器周期时间又包含有若干个时钟周期。

以51为例,晶振22.1184M,时钟周期(晶振周期)就是(1/22.1184)μs,一个机器周期包含12个时钟周期,一个机器周期就是0.5425μs。一个机器周期一般是一条指令花费的时间,也有些是2个机器周期的指令,DJNZ,就是双周期指令,所以指令周期为0.5425μs但不是所有机器周期都等于12个时钟周期的。

PIC单片机的时钟经过内部分频,实际的工作频率为晶振频率的四分之一,同时指令的执行采用流水线方式,大部分的指令的执行时间是一个周期,所以在用4MHz的晶振时,指令执行的最大速度为1MIPS,即指令周期为1微秒。

12.

奇偶校验:为了使一个系统能检查和纠正一个差错,码间最小距离必须至少是“3”。最小距离为3时,或能纠正一个错,或能检二个错,但不能同时纠一个错和检二个错。编码信息纠错和检错能力的进一步提高需要进一步增加码字间的最小距离。码距越大,纠错能力越强,但数据冗余也越大,即编码效率低了。

13.

RISC技术。CPU执行运算速度受三个因素的影响:

基本要素:

1.一个有限的简单的指令集

2.大量的通用寄存器

3.强调对指令流水线的优化

14.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?