使用集成低压降电压稳压器减少加密引擎的侧信道泄漏

1 引言

消费电子行业正在快速发展,物联网(IoT)和万物互联(IoE)设备通过在所有这些设备之间提供连接,正在改变人类的生活方式。然而,由于物联网设备可以存储重要信息且易于访问,近年来针对金融机构以及政府组织的多次黑客攻击事件表明,人们对保护这些设备免受恶意攻击者侵害的需求日益增长( https://www.wired.com/story/2017-biggest-hacks-so-far/)。

为了通过加密来保护秘密数据,可以在物联网设备上集成高级加密标准(AES)、三重数据加密标准( 3DES)等安全原语。然而,过去二十年的研究表明,这些安全原语的硬件实现会在加密过程中泄露物理信息,这些信息可被测量并进行统计分析,从而揭示出密钥因此导致全部加密数据泄露。会泄露信息的物理信道示例包括计算时间、功耗、电磁辐射(EM)和声波。基于功耗的侧信道分析(PSCA)利用在加密电路电源输入端测量到的电流/功耗中存在的任何泄漏。由数字门构成的任何数字电路的功耗取决于其内部节点的开关活动,而开关活动是密钥和输入测试向量(明文)的函数。

功耗攻击相对成本较低且易于实施,因此对加密电路的侧信道安全构成重大威胁,特别是对于物联网等资源受限设备,因为它们没有足够的资源来实施昂贵的对抗措施。此外,这些对抗措施中的大多数需要对底层加密电路进行完全或部分重新设计,从而增加设计成本。这促使人们需要低成本的通用对抗措施,能够轻松集成到任何安全电路中,以保护其免受此类物理攻击。

最近,研究人员提出了多种对抗措施以阻止 PSCA攻击。这些对抗措施可分为基于架构、逻辑或物理设计的对抗措施。如表1所示,大多数这些对抗措施会带来显著的功率、面积和/或性能开销[2–10]。

此外,它们还需要对底层数字电路进行重大修改。例如,一些最流行且商业上可获得的对抗措施基于差分动态逻辑(DDL)家族,以使功耗不受输入向量的影响;然而,差分逻辑至少会使面积或功耗增加一倍,无法随活动因子进行扩展,并且其定制设计使其难以与数字工艺技术同步发展。此外,已有高阶侧信道分析利用早期传播来攻破这些对抗措施[11]。

近年来,人们越来越关注利用电源传输网络( PDN)以及片上集成电压调节器(IVR)模块来调制设备在执行加密时产生的电流特征。然而,以往基于 IVR的研究主要集中在基于电感或电容的开关稳压器,以实现功耗攻击防护[12–17]。这些方案需要使用难以/昂贵与数字电路集成的无源元件。文献[18]中的作者利用IVR的快速环路响应来随机化工作电压和瞬时频率,从而提供PSCA抗性。

本文重点研究基于低压降(LDO)的片上电压调节器[19–21]通过引入电流变换来提供侧信道攻击防护。通过将电压调节器集成在芯片上,功耗攻击点从高级加密标准(AES)的供电节点(VIN,LDO)转移至电压调节器的输入电源(VAES)(图1)。与开关IVR不同, LDO无需任何嵌入式无源器件。它们在现代数字电路中已广泛使用,以实现高效的电源管理,降低电源噪声,从而提升性能[22]。例如,基于PowerPC的核架构采用每核LDO来实现细粒度电源管理[23]。

根据设计选择,LDO分为两种类型:(1)模拟LDO (ALDO)和(2)全数字LDO(ADLDO)。在模拟LDO中,反馈环路使用模拟电路以连续时间实现;而在全数字LDO中,反馈环路使用全数字电路以离散时间实现。模拟低压差稳压器具有更高的带宽,因此可提供快速响应,适用于高性能系统;但由于其控制器中的模拟模块消耗较高的偏置电流,因而不太适合低功耗系统。此外,由于设计复杂性较高,模拟LDO较难与数字处理器集成。而全数字LDO则具有设计更简单、更容易与数字模块集成以及更好的工艺技术可扩展性等优势,为能够容忍一定电源纹波且不需要极快响应的现代架构提供了更优的选择[22–26]。此外,全数字低压差稳压器在轻负载条件下效率很高,因此非常适合低功耗系统[26]。全数字低压差稳压器面临的主要挑战在于需要设计离散时间、潜在非线性反馈控制。近年来的多项研究已证明了全数字低压差稳压器的可行性[22, 26]。

本文中,我们将[19, 20]中的工作进一步扩展,以研究ALDO和ADLDO在功耗攻击防护中的作用。我们证明了ALDO和ADLDO均可提高加密引擎的功耗攻击抗性。我们探讨了ALDOs和ADLDOs中的信息丢失机制,并证明由于多种机制导致的信息丢失增加, ADLDO相比模拟LDO具有更高的PSCA抗性。通过对高级加密标准(AES)加密引擎的仿真和测量波形,我们表明,具备安全意识的集成低压差稳压器能够显著提升PSCA抗性,相关评估基于相关功耗分析(CPA)、信噪比(SNR)以及测试向量泄漏评估(TVLA)等侧信道分析(SCA)指标。

本文的其余部分组织如下:第2节介绍相关工作;第3节介绍仿真框架;第4节讨论集成LDO(包括 ALDO和ADLDO)的建模,以仿真其对AES负载电流的影响;第5节展示模拟的AES负载电流的相关功耗分析和信噪比结果;第6节讨论测量的AES负载电流的 TVLA和相关功耗分析结果;第7节针对低功耗以及高性能系统的安全感知集成低压差稳压器设计进行案例研究;第8节总结全文。

2 相关工作

最近的研究中,利用集成电压调节器(IVRs)实现功耗攻击防护的趋势日益增长(见表2)。这些研究大多采用需要嵌入式无源器件(电容和电感)的开关电容或开关电感型电压调节器。Telandro等人提出了一种开关电容转换器(SCC),用于保护智能卡免受PSCA [12]攻击。该SCC通过将智能卡电流特征中的峰值在时间上分散开来,从而扩散信息内容,据称可提供 PSCA防护。然而,作者并未提供统计分析来评估其对相关功耗分析(CPA)等统计攻击模型抵抗能力的改进。Ozun等人提出了多相开关电容转换器(SCC)的随机转换器门控技术以增强安全性[13, 14]。根据工作负载需求,随机选择或重排相位,从而对外部电源端观测到的电流进行随机化。然而,作者仅展示了功耗轨迹熵的改善,这可能无法有效提升对功耗轨迹进行统计分析的抵抗能力。Kar等人表明,全集成电感式电压调节器(FIVR)可以降低输入电流与负载电流之间的时间和频率相关性,并且他们还证明,结合一定的控制环路随机化技术,可使128位AES免受PSCA[15–17]攻击。

然而,尽管FIVR在移动SoC中前景广阔,但其设计复杂,且需集成片上或封装内电感器。Singh等人开展了使用集成模拟和数字LDO提升128位AES引擎PSCA抗性的案例研究[19, 20]。在[21],中,作者展示了利用混合模式LDO系统在衰减特征域中提高了侧信道攻击免疫能力。本文将进一步拓展[19, 20]的工作,证明 ADLDO相较于模拟LDO,可在多种AES架构下的仿真和测量电流中均提升PSCA抗性,同时还能提供与安全原语的良好集成性以及工艺可扩展性。

本文的贡献

与先前的研究相比,本文做出了以下独特的贡献:

& 我们开发了一种混合模式系统建模框架,将ALDO 和ADLDO模型与多个全芯片AES设计集成在一起。

& 我们研究了ALDO和ADLDO在模拟的AES负载电流下使用CPA和SNR的有效性。& 我们通过CPA和 TVLA研究了ALDO和ADLDO对实测AES负载电流的影响。& 我们证明了片上ADLDO可以提高PSCA抗性,并且比模拟LDO更有效。& 我们研究了针对高性能和低功耗负载的性能与安全性的集成LDO设计权衡。本文提出了适用于低功耗负载的ALDO和ADLDO设计,并表明其可改善PSCA抗性。

3 仿真框架

仿真框架(图2)包括对高级加密标准设计进行仿真以计算功耗,以及对低压差稳压器和全数字低压差稳压器的建模(图3)。在接下来的小节中将详细讨论。

3.1 AES加密引擎的设计

高级加密标准算法由128位明文和可变长度密钥( 128/192/256位)组成。密文输出为128位。它包含10轮加密,每轮包括四个轮操作:轮密钥加(ARK)、字节代换(SB)、行移位(SR)和列混淆(MC)。字节代换是一种非线性替换操作,根据密钥将8位输入数据映射为8位输出数据。

选择了两种不同的AES算法硬件架构来研究串行化对功耗攻击脆弱性的影响。我们实现了两种不同的 AES数据路径:(1)高性能AES(HP‐AES),也称为并行AES,包含128位数据路径,执行一次加密需要10个周期;(2)紧凑型AES(C‐AES),具有低面积和低功耗特性,也称为串行AES,针对逻辑密集型的S盒操作实现8位数据路径,完成单次加密需要500个周期(图 4)(http://opencores.org)。在使用模拟负载电流进行攻击时,我们的目标是第一轮S盒操作。由于其非线性变换特性,非常适合进行功耗分析攻击。

3.2 用于估计功耗攻击抗性的模型

我们使用了以下模型来评估集成低压差稳压器对功耗攻击的抵抗能力:

3.2.1 相关功耗分析

在基于[27]的相关功耗分析攻击中,攻击者加密多个明文并测量加密过程中的功耗。然后,他通过使用明文和对目标密钥字节的猜测,基于中间状态的汉明重量(HW)或汉明距离(HD)构建功耗模型。将测量的功耗轨迹与该功耗模型进行相关性分析,相关性最高的结果揭示出秘密密钥字节。1定义了在某一特定时间点ti以及对猜测密钥kj的相关系数(ρ):

ρ ti; kj ¼ E P−P PM −PM σ ðP Þσ PM ð Þ ð1Þ

其中P是模拟功率,PM是基于汉明重量/汉明距离的功耗模型, σ是标准差,E是期望值。在功耗分析攻击中,每次针对一个字节的密钥进行攻击,重复该过程 16次即可恢复完整的128位秘密密钥。在相关性随时间变化图中,正确猜测的字节将具有最高的相关性峰值。在我们的实验中,针对最后一轮的基于汉明距离的功耗模型对高性能AES给出了最佳结果,而针对第一轮S 盒的汉明重量功耗模型对C‐AES给出了最佳攻击结果。

3.2.2 信噪比估计

信噪比通过将泄露L建模如下进行计算:

L ðx Þ ¼ ε ϕð x Þ j jþ L0 þ Ν 0; σ2 ð2Þ

其中, ε 是由单个比特翻转所传递的泄露,称为信号, ϕ(x)是与明文和密钥(记为x)相关的泄露模型,L0 是由于设计中其他部分活动引起的电路功耗,N(0, σ2) 是加性白高斯噪声(AWGN)。该泄露模型下的信噪比SNR由[28]给出:

SNR ¼ ε=σ ð3Þ

3.2.3 测试向量泄露评估

TVLA是一种用于检测信息泄露存在的测试方法(https://csrc.nist.gov/csrc/media/events/non-invasive-attack-testing-workshop/documents/08_goodwill.pdf)。它不会揭示密钥,且与相关功耗分析中密钥为保密信息不同,在TVLA中, 密钥由测试者选择。测试者构建一个由统计随机明文集和特殊明文集组成的明文列表。选择特殊明文集,使得测量的功耗轨迹与第一组在统计上可区分。对测量的功耗轨迹执行Welch’s t检验, 当t统计量大于4.5时,表示存在信息泄露,置信度为 99.999%。使用方程4计算t统计量:

t ¼ x1−x2 ffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffiffi s12 n1 þ s22 n2 r ð4Þ

其中,t是t统计量或t得分,x1是第一样本集的均值, x2是第二样本集的均值,s1是第一样本集的标准差, s2是第二样本集的标准差,n1和n2分别是第一和第二样本集的大小。在我们的实验中,n1= n2= 2500, 并且同一实验进行了两次,以确保多次实验间泄漏的一致性,因此TVLA实验总共需要10,000次测量。

4 集成低压差稳压器对AES负载电流的影响

4.1 集成LDO建模

当低压差稳压器集成在片上时,试图实施功耗攻击的攻击者无法再访问负载电路(高级加密标准)的内部供电节点。攻击者唯一可见的节点是集成低压差稳压器的输入节点,VIN,LDO(图1)。负载电流受到集成低压差稳压器传递函数特性的影响。本节研究集成模拟和数字LDO对负载电流的影响。

4.1.1 集成模拟LDO建模

片上模拟LDO包含一个由大尺寸功率场效应管( PMOS/NMOS)、误差放大器(EA)和输出负载组件(负载建模为RL与CL并联)组成的功率级,如图3 a 所示。运算放大器作为误差放大器,将参考电压(V REF)与输出电压(VOUT)之间的误差信号放大后反馈至功率级的输入端。R1和R2决定反馈系数(在本模型中取为0.5)。由于误差放大器(EA)具有很高的输出阻抗以及功率场效应管具有较高的输入电容,反馈系统的主导极点位于误差放大器(EA)的输出端。该主导极点在决定闭环系统响应(如带宽和稳定性)方面起着关键作用。系统的第二极点位于输出端,由输出电容(CL,通常在集成LDO设计中远小于功率场效应管的输入电容)和输出负载电阻(RL)共同形成。CL由电源网络的寄生电容以及为减小大负载变化时的初始压降而在设计中加入的去耦电容共同决定。模拟LDO系统的小信号开环传递函数可描述如下:

H op en ðs Þ ¼ gmAoroRL 1 þ sCeq Ro ro þ RL þ sCLroRL ð Þ ð5Þ

其中,gm=为通路晶体管的跨导,Ao=为误差放大器的直流增益,ro=为通路晶体管的沟道电阻,RL=为负载电阻= Vout/IL在直流条件下,Ce q =为内部节点总电容= C g s +Cdb + Cg d(1+ Ap),Ap =为通路晶体管增益= gm(ro-∣ ∣RL),Ro =为误差放大器的输出电阻,CL =为负载电容。

这两个极点分别位于1/Ce qRo和1/CL(ro | |R L)。模型中使用的典型值为I REF = 50 mA,V dro p out = 0.1V,A 0 = 74 dB,R o = 250 kΩ,r o = 2 kΩ,V out = 1.0V,V in = 1.2 V,CL = 30皮法,Ceq= 6 pF,宽长比= 5000。通过改变CL 获得窄范围带宽变化所需的带宽,而通过改变Ceq 实现宽范围带宽变化。

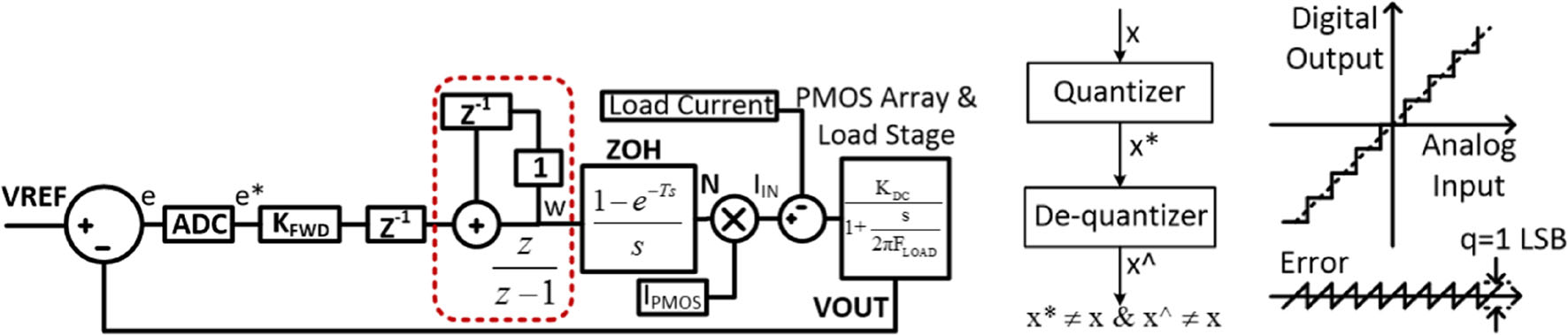

4.1.2 集成全数字LDO建模

片上ADLDO由基于PMOS的功率场效应管阵列组成, 用于提供所需的负载电流,以及一个多比特模数转换器(ADC),用于检测参考电压(VREF)与输出电压(VOUT)之间的误差,并将该误差转换为离散值。这些离散值随后用于补偿增益,以开启/关闭PMOS器件,从而调节PMOS网络的有效电阻。图3b展示了一个 ADLDO及其加载阶段(建模为RL和CL并联)。负载电流的任何瞬时变化都会导致VOUT下降。该VOUT随后与 VREF进行比较(假设VOUT和VREF具有相同的稳态值),误差在采样频率(f S)下被采样并离散化。对于线性反馈环路,ADC的输出直接用于开启/关闭部分PMOS器件;而对于非线性反馈环路,误差可结合非线性增益来控制启用/禁用的PMOS器件数量。

图5a显示了全数字低压差稳压器的控制环路。全数字低压差稳压器在z域中的离散控制环路模型可推导为:

e* ð nTÞ ¼ VREF ð nTÞ−VOUT ð nTÞ ð6Þ

wð nTÞ ¼ w n−1 ð ÞT Þ þ KFWDe* ð nTÞ ð7Þ

其中,w是数字字,KFWD 是数字控制环路的总增益。可通过非线性增益实现快速环路响应。由式(7)可得z域中的传递函数为:

W ðz Þ ¼ KFWD z z−1 E ð zÞ ð8Þ

数字字W控制着导通的PMOS器件的数量,从而与连续时间进行接口系统。这可以建模为一个零阶保持电路(ZOH)后接 PMOS阵列和负载级。负载电容(包括PMOS阵列的寄生电容以及加密核心电源网络上的总电容)和输出节点处的有效电阻决定了连续时间传递函数中的极点。

流经外部电源的电流IIN等于N与单个PMOS器件提供的电流(IPMOS)的乘积。连续时间系统的总体传递函数如下所示:

Cð s Þ ¼ 1−e−Ts s IPMOS KDC 1 þ s 2πFLOAD ð9Þ

C(s)在z域[C(z)]中可以表示为:

Cð z Þ ¼ 1−e−ωLOADT ωLOAD KDC z−e−ωLOADT IPMOS ð10Þ

其中,KD C 是连续时间传递函数的直流增益,且휔 LOAD= 2πFLOAD。开环系统在z域中的总体传递函数V(z)可表示为:

V ðz Þ ¼ KFWD z z−1 1−e−ωLOADT ωLOAD KDC z−e−ωLOADT IPMOS ð11Þ

系统的闭环传递函数H(z)可表示为:

H ðz Þ ¼ V ðz Þ 1 þ V ðz Þ ð12Þ

4.2 集成低压差稳压器的信息丢失机制

4.2.1 模拟LDO引起的信息丢失可能性

模拟LDO的输入电流对负载电流的依赖性可以使用下方所述方程进行建模:

iin iL ¼ roRLCLs 1 þ sCeqRo roRL þ s ro þ RL þ gmAoroRL ð ÞCL þ roRLRoCeq þ s2 ro þ RL ð ÞRoCeqCL

闭环传递函数中有两个零点和两个极点。频率相关的非线性传递函数会转换负载电流iL中的小信号变化。因此,通过调节传递函数的频域特性,例如反馈误差放大器的增益和频率响应、输出负载电容、功率场效应管尺寸以及增益,可以抑制通过低压差稳压器泄漏的信息。

积分效应 输出去耦电容(CL)用于在负载突变时减小输出电压下垂。它起到低通滤波器(积分器)的作用,平滑输出电流模式,并将信息含量扩散到一段时间持续内(从而降低低压差稳压器输入端的信噪比,SNR)。反馈环路也起到积分器的作用(一阶或更高阶,取决于所使用的补偿电路)。

ALDO系统的带宽 LDO系统的环路带宽决定了其闭环响应。带宽越高,系统对快速负载瞬态(高频变化)的响应越好。因此,如果LDO带宽较高,大多数小信号变化将被通过。然而,对于带宽较小的LDO,高频信号会被大幅衰减。因此,如果信息通过高级加密标准负载电流中的高频变化泄露,则在经过集成模拟低压差稳压器调制时应被强烈抑制。

4.2.2 由于全数字LDO导致的潜在信息损失

ADLDO输入端的电流(IIN)确定为:

IIN ¼ N IPMOS ð13Þ

其中N为导通的PMOS器件数量。N的值由ADLDO的反馈环路决定,该环路会根据负载电流的变化调整N。当负载电流通过ADLDO时,存在三种信息丢失机制: (1)积分效应,包括来自输出节点的负载电容以及环路中补偿器的积分效应;(2)来自模数转换器的量化损耗;(3)输出电压的有限采样。

积分效应 与模拟LDO类似,ADLDO输出端的负载电容用于提供负载电流中高频变化所需的电流,其作用相当于一个低通滤波器(即积分器),可平滑电流波形,从而将信号在一段时间持续上展开(同时扩散),该时间持续取决于低通滤波器的带宽。为确保 ADLDO稳定性而采用的补偿方案也会改变电流波形中的信息含量。一种常见的方案是基于移位器的积分器,它在ADLDO中的作用类似于负载电容,会将信息在时间上展开并扩散。然而,随着积分过程的发生,信息仅被扩散而不会丢失,这一点将在模拟LDO的情况中看到。因此,根据负载电流的模式不同,攻击点处的信噪比可能显著下降,也可能不会显著下降。

通过ADC的量化损耗 模数转换器(ADC)是数字系统中的重要组件之一实现控制环路。模数转换器在控制环路中的作用是对采样输出电压(VOUT)与参考电压(VREF)之间的误差进行数字化。模数转换器的数字输出被用作阵列中PMOS元件的使能信号。图5b、c显示了使用模数转换器采样的输入信号。同时还绘制了实际输入与采样输出信号之间的误差。该误差称为量化误差/噪声,其均方根值可计算为[29]:

enjRMS ¼ qffiffiffiffiffi 12 p ; q ¼ VREF 2N ð14Þ

其中,Bq^为量化步长,N为ADC位数。N值越高,精度越好。然而,更高的精度也需要更多的ADC功耗。

输出电压的有限采样 当从设计中抽取的电流出现突然尖峰时,输出电压会下降。输出下降取决于输出电容(作为积分器)和ADLDO响应。输出以采样频率(fS)进行采样,根据奈奎斯特采样定理,电压压降或抽取电流中频率高于>fS/2的成分将丢失,从而导致信息损失。

4.3 集成低压差稳压器对高级加密标准负载电流的影响

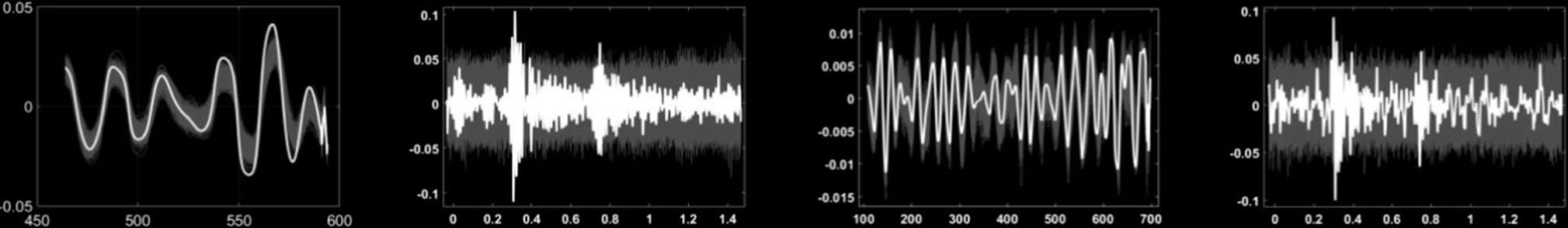

在图6a中,绘制了负载电流及其快速傅里叶变换(左侧)。在200兆赫及其谐波处存在峰值,与设计频率相匹配。此外,在100兆赫至10吉赫之间还有许多其他峰值,代表由于设计中的开关活动导致的电流变化中存在的频谱成分。图6a还显示了带宽为376兆赫和446兆赫时LDO输入电流。输入电流中的频谱成分在高于LDO的3分贝频率时被衰减,仅能看到少数小的峰值。因此,高频电流变化被大大衰减。

图7a显示了2000条功率迹数下LDO负载电流与输入电流之间的相关性分布。时域相关性非常差(< 0.05),这是预料之中的,因为LDO在负载电流中引入了与频率相关的相位偏移。在频域中,我们看到更大的相关性,范围为0.25–0.35。因此,信息在频域中得到了更好的保留。

图6b展示了在两种不同采样速率和ADC量化间隔下,并行AES负载与ADLDO输入电流的波形。从这些波形中可以明显看出,较低的采样速度和更粗略的模数转换器分辨率的影响(当fS=10吉赫、模数转换器分辨率= 10b时,相比fS= 1吉赫和模数转换器分辨率= 7 b,小信号变化更容易传播)。图7b显示了相对于 ADLDO的输入电流和负载电流之间的相关性。与 ALDO类似,在频域中保留了更多的信息。此外,即使在频域中,在较低的采样频率和ADC分辨率下,负载电流与输入电流之间的相关性也非常差,表明 ADLDO相比ALDO可能提供更好的PSCA防护。

5 基于集成低压差稳压器的功耗攻击防护用于模拟的 AES负载电流

5.1 基于集成LDO的功耗攻击防护

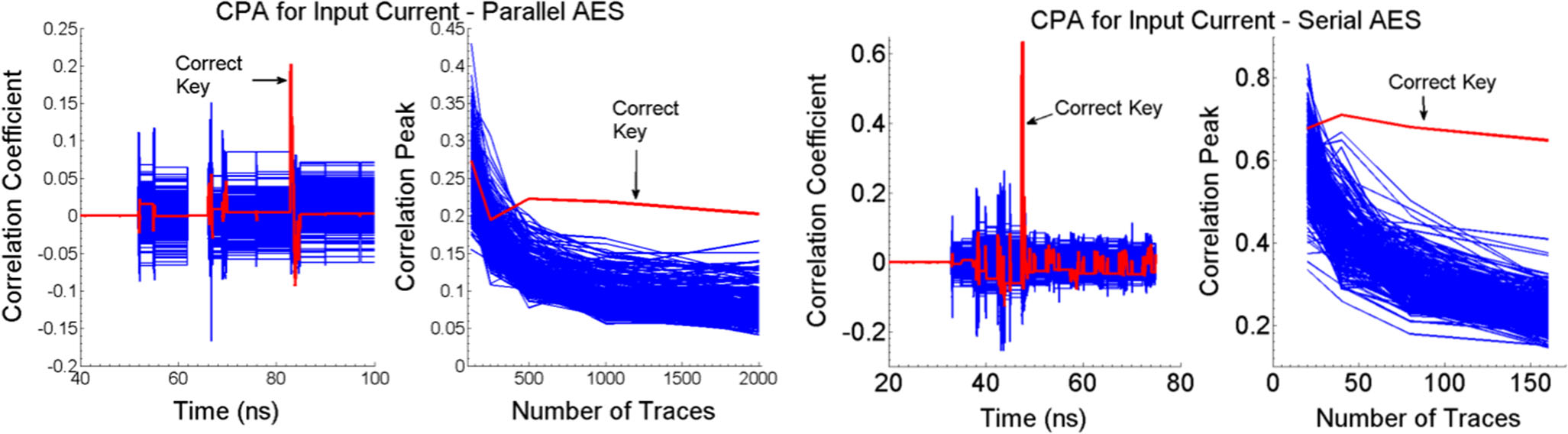

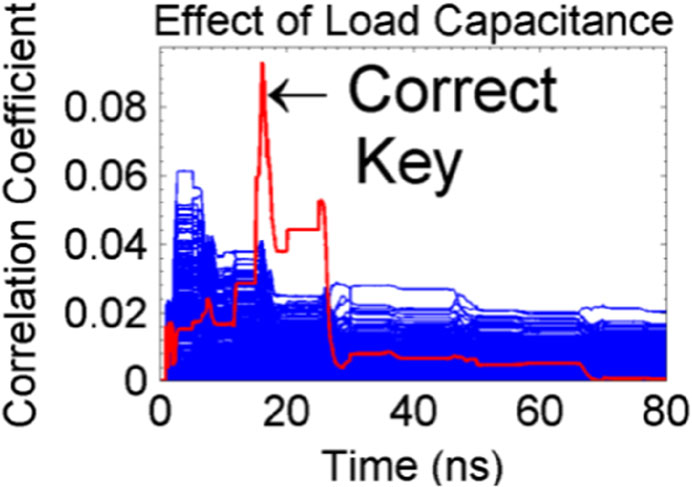

我们使用ASU45纳米预测技术模型(PTM45)库对综合后的C‐AES设计进行PSCA攻击。我们通过调整极点位置来设计具有可变带宽的低压差稳压器。图8显示了高性能AES和C‐AES的数字核输入电流的相关性随时间变化图。这些设计在AES输入处的MTD分别为500和 25,正确密钥字节的相关峰值分别为0.2和0.6。

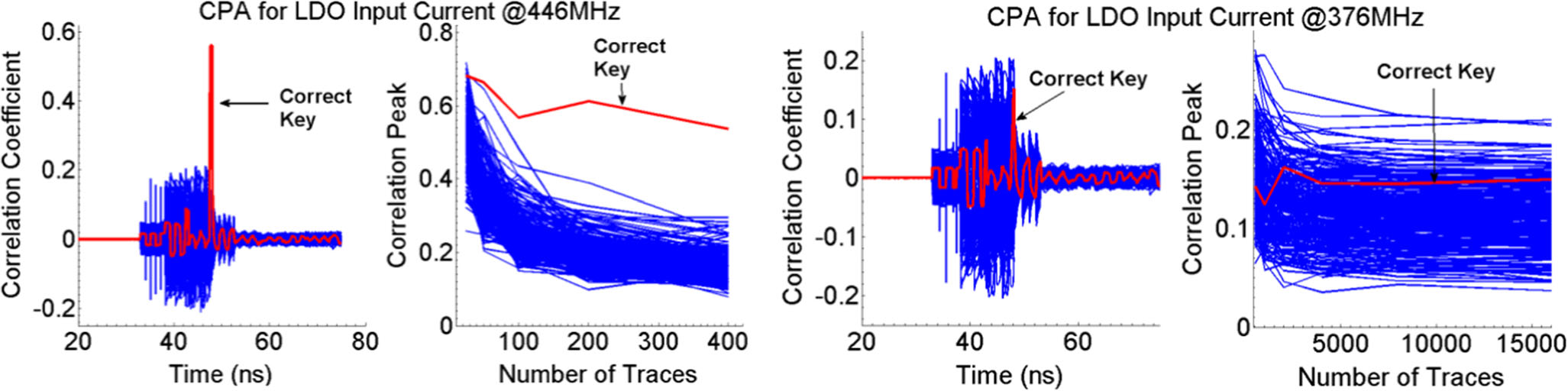

当C‐AES负载电流通过具有可变带宽的片上 ALDO进行变换时,在非常高的ALDO带宽下,我们发现攻击仍然会发生[MTD=50,图9a]。此外,明显峰值的相关性高度仅有小幅变化。然而,在较小带宽下,攻击特征迅速改变,且无法成功实施攻击。在图9b中可以看到,即使使用20,000条功耗轨迹,在376MHz ALDO带宽下也无法实现攻击。同时,正确密钥的相关峰值显著降低。图7a显示了两种带宽下的ALDO输入电流——376和446兆赫。如果我们观察这些电流的快速傅里叶变换(FFT),可以发现如预期一样,446兆赫在较高频率处具有更多的频谱成分。信息内容可能存在于电流特征的较高频率部分,这些高频成分在较高带宽下会未经抑制地通过ALDO,而在较低带宽下则被抑制。

图10显示了该设计在200MHz时钟频率下综合的平均攻击所需迹线数与带宽特性,随着带宽降低,平均攻击所需迹线数起初没有变化,但随后迅速在接近400兆赫时增加。当我们把设计的时钟频率改为 250兆赫时,观察到类似的行为,表明攻击特性与高级加密标准时钟频率无关,仅取决于数据相关电流变化中存在的频谱成分。图10还显示,相关峰值的高度随更高带宽的宽带低压差稳压器而增加,这是符合预期的。

)

)

对于ADLDO,我们在MATLAB中对其进行建模(如第 4.1节所述),并改变模数转换器分辨率(6位到10位)和采样频率(100兆赫到10吉赫)。我们从包含电源网格的布局布线设计中提取了输出电容,并将其在ADLDO输出端建模为集总值(1皮法)。图11a显示了在ADLDO输入端测得的经变换的高性能AES电流上成功实施的相关功耗分析攻击,该测量使用8位模数转换器和500兆赫的采样频率。当同一设计的模数转换器分辨率降低至7位时,此类攻击不再可行[,如图 11b]所示。我们无法利用20,000条功耗轨迹对经过变换的电流实施相关功耗分析攻击。采用7位模数转换器的设计信噪比为0.0076(~ 20×低于原始电流波形的信噪比)。

我们研究了功耗分析攻击抗性(即信噪比和MTD)与全数字低压差稳压器设计参数(即模数转换器分辨率和采样频率)之间的权衡[图12a,b]。当采样频率保持在10吉赫且模数转换器分辨率是 从10位变为6位时,我们发现,在非常高的模数转换器分辨率(10位)下,信噪比最高为0.039(但仍远低于原始电流波形的信噪比0.15)。当模数转换器分辨率降低到8 位时,信噪比降至0.037。然而,我们看到在仅2000条迹数的情况下,8位模数转换器的信噪比(0.053)优于10位模数转换器的信噪比(0.036)。这是反直觉的。一种可能的解释是,使用10位模数转换器时,通过的噪声成分相比有用信号更多。当我们进一步减小模数转换器的量化间隔时,信噪比进一步降低,在模数转换器分辨率为6位时,即使使用20,000条功耗轨迹也无法实现攻击。我们在采样频率方面也观察到类似特性:攻击发生在10G‐250兆赫兹的采样频率下,而在100兆赫时无法进行攻击。在100兆赫时,信噪比为0.004~ 40×,小于原始数据的信噪比,强烈表明对侧信道攻击具有抵抗能力。

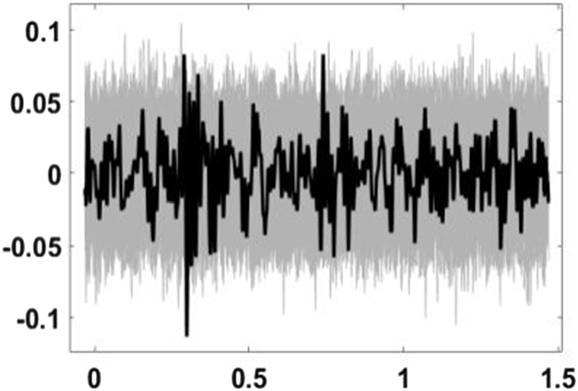

5.2 交流和直流背景噪声的影响

由于嵌入式加密引擎与数字集成电路的其他功能模块共享相同的电源/地线,这些模块消耗的电流会形成噪声,并可能劣化攻击特性。我们研究了交流以及交流噪声和直流噪声对AES电流和ADLDO输入电流的信噪比的影响。交流噪声被建模为具有零均值和变化的标准差(0.5–10 μA)的高斯噪声,直流噪声被建模为恒定的背景电流(5–100 μA)。图12c、d展示了交流噪声和直流噪声对信噪比的影响(MTD呈现出类似的趋势)。

如预期所示,随着噪声方差的增加,原始电流的信噪比下降。然而,当这些带有噪声的电流波形通过ADLDO时,由于其固有的损耗,信噪比进一步恶化(3–5×倍)。因此, ADLDO放大了添加到AES电流中的随机噪声的影响。对于直流噪声我们也观察到类似的行为:原始电流在存在直流噪声时信噪比保持恒定,但在使用数字LDO时信噪比显著降低。ADLDO的负载极点在恒定负载电流存在的情况下发生变化,导致ADLDO整体响应发生改变。

5.3 模拟LDO与全数字LDO的比较

模拟LDO本质上充当一个积分器,在功率波形的攻击点处增加了来自历史的不相关功率,从而降低了攻击点处的信噪比。然而,信息仍然存在于电流波形中,并未丢失。根据底层设计的电流特性(加密引擎本身的电流特性以及其他有源功能模块引入的直流和交流噪声),信噪比的降低程度可能不足以保护该设计。

在图11a中,我们观察到具有较低带宽可以保护紧凑型串行AES(C‐AES)。然而,对于高性能AES设计,即使在非常低的LDO带宽下也会发生攻击 ~ 2 kHz[图11c]。这主要是因为C‐AES设计是字节串行设计,因此在攻击一个字节时,集成会引入来自其他字节的噪声。这种噪声在字节并行的高性能AES中不那么关键(其他字节的噪声本来就存在,并非由LDO引入),使得模拟LDO的效果较差。图13a显示,采用模拟LDO的高性能AES设计在较低

带宽下的信噪比并未显著下降。此外, 图12c,d表明,当在高性能AES设计中加入基于模拟 LDO的保护时,交流/直流噪声的影响可忽略不计。

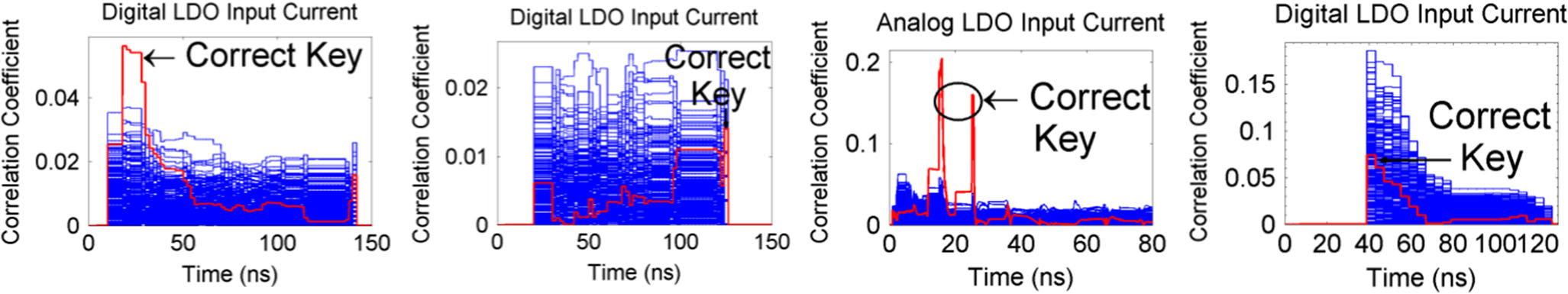

另一方面,全数字低压差稳压器可以保护C‐AES设计 [图11d]以及高性能AES设计[图9b]。这是因为,除了在 攻击点处的积分产生的噪声外,数字辅助低压差稳压器还 通过量化损耗和有限的采样率具有固有的信息丢失机制。 因此,我们观察到,数字辅助低压差稳压器在提供功耗攻 击防护方面优于模拟低压差稳压器。

6 基于集成LDO的功耗攻击防护用于测量高级加密标准负载电流

为了研究集成ALDO和ADLDO对实时测量电流的影响, 我们从一款具有HP‐AES和C‐AES的测试芯片(130纳 米)中采集了功率迹数。测量波形经过用于研究其对PSCA特性影响的ALDO和ADLDO的 MATLAB模型[图2b]。以下小节讨论了测量的功率特征以 及基于这些测量的功率特征的TVLA和相关性CPA结果。

6.1 测量的高级加密标准功耗特征

图14(a)和15(a)分别显示了在高性能AES和紧凑型 AES设计上进行加密时的测量波形。这些波形使用以设 计时钟频率(37兆赫兹)为中心的带通滤波器进行滤 波,以去除带外噪声。对应的滤波后波形如图14(b)和 15(b)所示。由于C‐AES每个周期执行的计算量较少 (一种深度流水线设计),其在轮操作期间的电压波动 相比高性能AES更小。

6.2 测试向量泄露评估分析

接下来,我们考虑使用TVLA结果来检测带有和不带有 集成低压差稳压器的高性能AES和紧凑型AES设计的信 息泄漏量。测量电流通过基于MATLAB的ALDO和 ADLDO模型进行处理,其中ALDO采用可变带宽, ADLDO采用可变采样速度和ADC分辨率。图16显示 了测量电流的TVLA结果。对于这两种设计,存在当缺乏防护时,HP‐AES和C‐AES设计在图16(a)& (b)中分别出现23和28.15的峰值,存在显著的信息泄 露。当在片上集成模拟LDO(ALDO)与加密核心时, ALDO输入端观察到的泄露(图17)虽低于原始AES电 流,但仍显著,表明ALDO对TVLA泄露的改进有限。 然而,当在片上集成全数字LDO时,|t统计值|在两种 AES设计中均降至4.5阈值以下,表明无信息泄露(图 18)。因此,全数字低压差稳压器可在提供充分 PSCA防护的同时,兼具易于集成和工艺可扩展性。此 外,全数字低压差稳压器相比模拟LDO具有更强的 PSCA抗性。

设计和b紧凑型AES(C‐AES) 设计。|t值|峰值在250兆赫和模数转换器分辨率= 6b条件下,对于高性能AES(HP‐AES)和C‐AES设计均降至4.5阈值以下,表明无信息泄漏)

6.3 相关功耗分析

我们通过统计分析多个明文的测量功耗,执行相关功耗分 析(CPA)以提取正确密钥。对于高性能AES和C‐AES设 计,分别仅需5000和400次测量(披露所需最小迹数, MTD)即可恢复正确密钥[图19a, b]。我们观察到,即使 使用带宽极小(640千赫兹)的低压差稳压器,对于 C‐AES设计仍能用2000条迹线发起攻击(5× MTD的改进)。然而,对于相同的ALDO设计,即使使用2万条迹线,也 无法成功攻击HP‐AES设计[图19c, d]。

因此,ALDO提供的PSCA抗性取决于底层加密设计以 及正在泄漏的频率分量。一个设计中泄漏的频率分量 取决于多个参数,例如设计时钟频率、由工艺技术决 定的门延迟等。我们进一步观察到,在使用ADLDO (fs= 250 MHz且ADC分辨率为= 6位)的情况下,即 使采用20,000条功耗轨迹,也无法对HP‐AES和 C‐AES设计成功执行CPA[图20a,b]。因此,我们可以 推断,ADLDO在多种设计中均能提供比ALDO更高的 PSCA抗性。

低压差稳压器。在使用20,000条测量的功率轨迹的情况下,高 性能AES未能被成功攻击,而C‐AES在MTD方面表现出有限的改进(5×)改进)

图20c总结了ALDO和ADLDO对HP‐AES和C‐AES设 计的TVLA泄露及CPA分析的影响。采用ADLDO时,对 于具有较低采样时钟速率和6b模数转换器分辨率的 ADLDO设计,未检测到TVLA泄露。此外,在通过CPA 揭示正确密钥时,至少需要 50×增加MTD。

7 安全感知集成低压差稳压器设计

7.1 利用现有的集成低压差稳压器实现安全防护

我们的讨论表明,将集成低压差稳压器嵌入加密引擎 中,有助于提高对功耗攻击的防护能力。因此,那些 已经利用低压差稳压器实现细粒度电源管理和性能改 进的多核处理器[22–26,30–32]也可以利用这些LDOs以提供功耗攻击防护。然而,为了实现有效的防 护,使用ADLDO比使用模拟LDO更有优势。具有高采 样率(~ 1 GHz)和多比特(3–7位)ADC的全数字LDO可以实现与模拟LDO相当的性能,如文献[22–26,30–32],所示,同时显著提升功耗攻击抗性。需要注意的是,ADLDO的性能(以负载电流阶跃下的电压压 降和电压稳定时间来衡量)与其PSCA抗性之间存在权 衡关系,如图13c所示:尽管降低采样频率可提高功耗 攻击抗性,但会恶化稳定时间并增加电压压降。

7.2 用于低功耗系统的集成低压差稳压器

轻量级加密设计功耗极低,因此集成LDO的设计与针 对大功耗高性能处理器系统的设计相比具有完全不同 的权衡。我们为典型1毫瓦@1V的加密引擎负载设计了 集成ALDO和ADLDO。

7.2.1 集成模拟低压差稳压器的设计

由于ALDO上的压降是功耗开销(以及LDO能效)的 主要因素之一,我们将假设压降尽可能小。然而,压降 具有反比关系与相同负载电流所需的通路栅极尺寸之间的关系(在 直流条件下,由于压降很低,通路晶体管将在三极管 区工作),因此我们必须在面积和功耗开销之间进行 权衡。

传统的低压差稳压器设计的压降低至85mV[25]。我们将设计 用于50mV压降的低功耗低压差稳压器,以在通路栅极上实现非常小 的损耗。所使用的参数为μ p = 0 86 × 10 −2 0432 ox= 1 −2 423 .m 2 V −1 s −1, C.fm,VT p = −0.V。其他参数如图21(a)。根据三极管区电流方程,当负载电流为1毫 安时,宽长比W/L估计为400[图21a]。我们的主要目 标是确保输出电压不超过设计规定的压降(假设为 ± 50毫伏或 ± 5%的工作电压),并且稳定时间要足够 小,以免影响系统性能。对于给定的压降,响应时间 与ALDO系统的带宽成反比,而带宽由主导极点决定。 在低功耗片上ALDO设计中,误差放大器消耗的电流保 持非常小(数百纳安),因此在误差放大器节点处看到的输 出电阻将很大(在MΩs量级)1.2MΩ(400纳安时)。由于类似原因,误差放大器的 增益也较小(~ 45 dB)。然而,由于通路栅极仅向负载提供 1毫安电流,其提供的电容较小(3皮法)。因此,1‐10兆赫 兹范围内的内部极点将为主导极点(휔I=(RoCeq) −1)。负载 极点(ωL= RoutCL) −1)将位于更高的频率,因为Rout= RL|| Rsd较小(Rds= Vds/IL且RL= Vout/IL)。图21b显示了该系统 的开环传递函数随频率的变化情况,其单位增益频率为8兆赫 兹,相位裕度为30°。图21b还显示了系统在负载电流阶跃为 1毫安时的响应。输出端的电压压降为14毫伏。分析表明稳定时间为200纳秒。由于该 ALDO的带宽(8兆赫兹)小于第5.1节中攻击频率,因 此我们不期望在模拟的C‐AES波形上对ALDO输入电流 产生任何功耗攻击。然而,如前所述,测量得到的 C‐AES波形相对于ALDO显示出一定程度的改进,但并 未实现完全保护。图21c显示,当测量的C‐AES波形通 过ALDO后,其MTD确实有所改进( 5×在MTD = 2000与原始C‐AES迹数的MTD= 400相比)。

7.2.2 集成全数字LDO设计

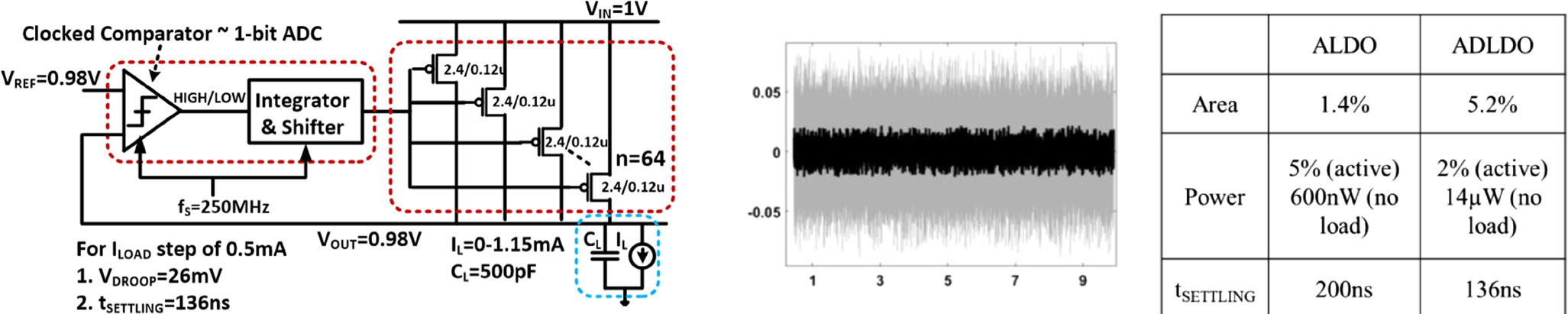

在本小节中,我们研究了将全数字低压差稳压器( ADLDO)集成到带有AES引擎的低功耗系统中作为功耗 攻击对策的可行性;挑战在于设计一个待机功耗极低的 ADLDO。我们采用[26][图22a]中所述的设计,在130纳 米CMOS工艺中设计了一个ADLDO。该ADLDO由一个 时钟比较器、移位输入/输出寄存器和PMOS阵列组成。 时钟比较器充当1位模数转换器,导致响应非常缓慢,但 实现了ADLDO的极低功耗控制器。ADLDO输出的目标 功率(包括AES引擎)为1毫瓦。采用较小的输出电容 (~ 500皮法),以确保在0.5毫安电流阶跃下具有可接受 的响应(电压压降~ 26毫伏)和稳定时间~ 136纳秒)。 然而,若无ADLDO,AES电源节点上的较大电容仅起到 积分器作用,无法防止相关功耗分析(CPA)[图13b]。 当考虑所设计的ADLDO时,即使使用2万条迹线也无法 成功实施任何功耗攻击[图22b]。本质上,在AES电源节 点存在500皮法电容(即ADLDO输出端)的情况下, AES负载电流引起的电压压降非常小,不会导致 ADLDO环路动态/响应发生任何变化。

7.2.3 开销分析

图22c中的表格显示了ALDO和ADLDO设计相对于底 层C‐AES引擎的功率、性能和面积开销。对于ALDO, 误差放大器消耗的电流增加了待机功耗,而50毫伏的 压降电压在活动状态下导致5%的功耗惩罚由于200ns的稳定时间相对于设计延迟(~ 13.5us) 而言,其性能影响较小。总体而言,面积、功耗和性能 开销分别为1.4%、5%和1.4%。对于全数字低压差稳 压器(ADLDO),由于采用数字控制,其面积和待机 功耗开销略大,但工作功耗开销小于对应的低压差稳压 器(ALDO)。然而,由于基于移位器的控制器在每个 时钟周期仅使能一个PMOS,导致ADLDO的响应速度 明显较慢,稳定时间相比ALDO更长。因此, ADLDO相较于ALDO能够提供更好的PSCA抗性,但 需付出更高的性能和面积代价。

8 结论

本文证明了集成LDO可用于增强对PSCA攻击的防护能 力。我们表明,ADLDO在多个安全电路中相比其模拟 对应器件能够提供更好的功耗攻击防护,这是因为在 控制环路中存在由调节电压采样和模数转换器中的量 化损耗所引起的固有信息损失机制。片上LDO目前已 被广泛用于多核处理器中的细粒度电源管理。我们得 出结论:当这些LDO被设计为数字LDO时,也可用于 增强功耗攻击防护。此外,我们还观察到,安全感知 的ADLDO可以集成到低功耗处理器中,主要用于侧信 道防护,同时仅带来极小的面积/功耗开销。

656

656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?