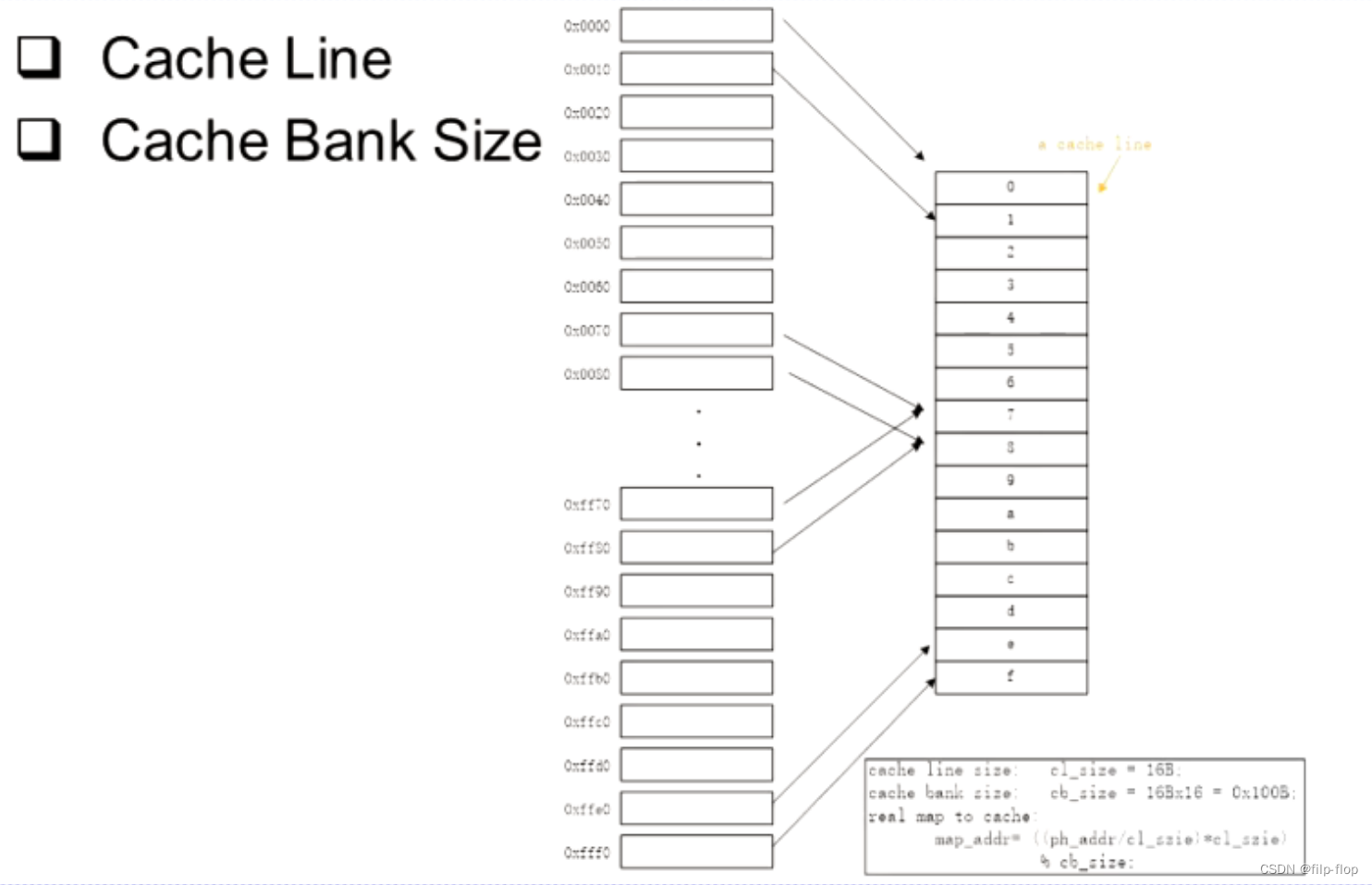

cache line

比如定义cache line的size是16byte;

cpu访问的时候 要用wrap和cache有关

cache的更新是一条line一条line的更新,为了cache管理简单一点,看有没有被hit的时候简单一点,靠cache line要么都被更新,要么都被踢走。

cache line:每次内存和CPU缓存之间交换数据都是固定大小,cache line就表示这个固定的长度。

cpu取一个指令,从memory中

cpu连续两次访问同一个地址,cache看到cache缓存空间中有这个地址的数据,就不用再访问下面的slave,把这个地址的数据拿给cpu直接用,

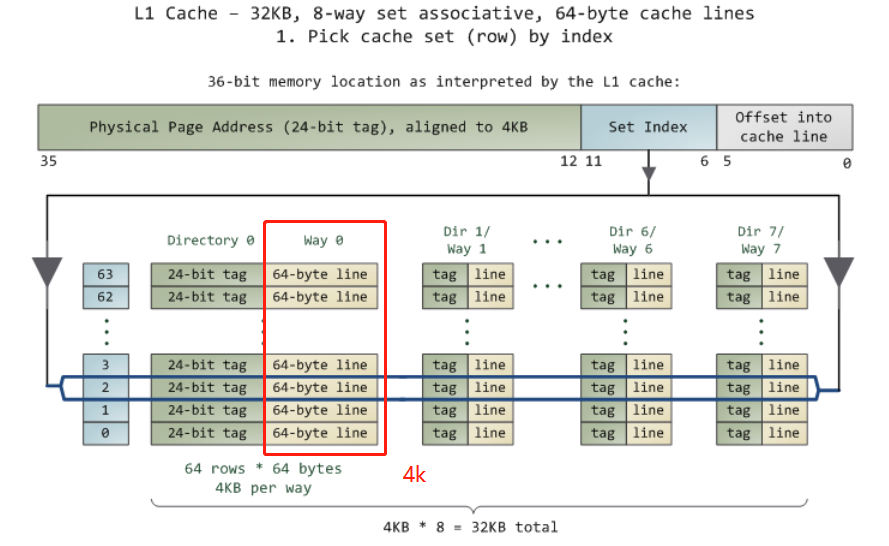

一个cache被分为S个组,每个组有E个cacheline,而一个cacheline中,有B个存储单元,现代处理器中,这个存储单元一般是以字节(通常8个位)为单位的,也是最小的寻址单元。因此,在一个内存地址中,中间的s位决定了该单元被映射到哪一组,而最低的b位决定了该单元在cacheline中的偏移量。valid通常是一位,代表该cacheline是否是有效的(当该cacheline不存在内存映射时,当然是无效的)。tag就是内存地址的高t位,因为可能会有多个内存地址映射到同一个cacheline中,所以该位是用来校验该cacheline是否是CPU要访问的内存单元。

当tag和valid校验成功是,我们称为cache命中,这时只要将cache中的单元取出,放入CPU寄存器中即可。

cache地址和主存地址之间有对应关系:</

文章详细介绍了cacheline的概念,指出其在CPU访问内存时的作用,如何通过wrap机制提升效率,并解释了cache的组织结构,包括组、行和存储单元,以及地址映射和命中检查的过程。

文章详细介绍了cacheline的概念,指出其在CPU访问内存时的作用,如何通过wrap机制提升效率,并解释了cache的组织结构,包括组、行和存储单元,以及地址映射和命中检查的过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8648

8648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?