【系统架构设计师】第一章 计算机组成与体系结构

文章目录

重点:

计算机结构(⭐)

存储系统(⭐⭐⭐⭐)

数据传输控制方式(⭐)

总线(⭐⭐)

CISC 与 RISC(⭐)

流水线(⭐⭐)

校验码(⭐)

嵌入式(⭐)

考频:一般占3分,在0~6分之间浮动

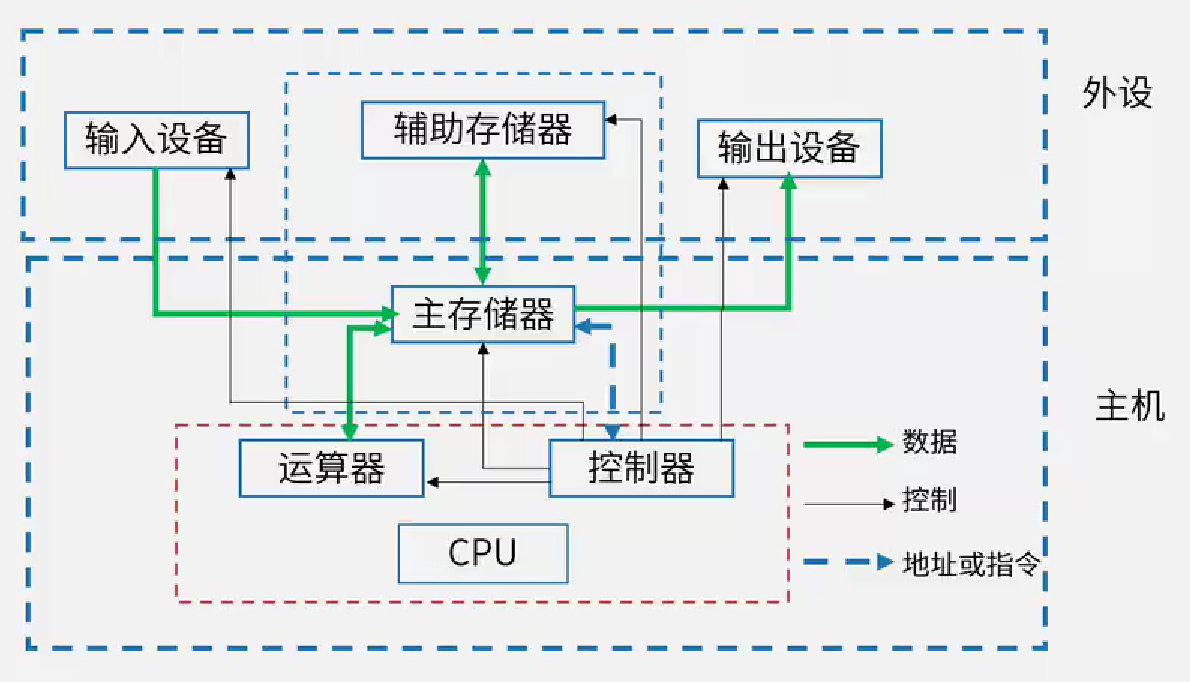

一、计算机组成结构

二、CPU组成

1.运算器

- 算术逻辑单元ALU:数据的算术运算和逻辑运算

- 累加寄存器AC:通用寄存器,为ALU提供一个工作区,用于暂存数据

- 数据缓冲寄存器DR:写内存时,暂存指令或数据

- 状态条件寄存器PSW:存状态标志与控制标志

2.控制器

- 程序计数器PC:存储下一条要执行指令的地址

- 指令寄存器IR:存储即将执行的指令

- 指令译码器ID:对指令中的操作码字段进行分析解释

- 时序部件:提供时序控制信号

三、冯·诺依曼结构与哈佛结构

1.冯·诺依曼结构

冯·诺依曼结构也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储结构

- 一般用于 PC 处理器,如 i3、i5、i7处理器

- 指令与数据存储器合并在一起

- 指令与数据都通过相同的数据总线传输

2.哈佛结构

哈佛结构是一种将程序指令存储和数据存储分开的存储结构。哈佛结构是一种并行体系结构,它的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问

- 一般用于嵌入式系统处理器(DSP)数字信号处理(DSP,Digital Signal Processing)

- 指令与数据分开存储,可以并行读取,有较高数据的吞吐率

- 有 4 条总线:指令和数据的数据总线与地址总线

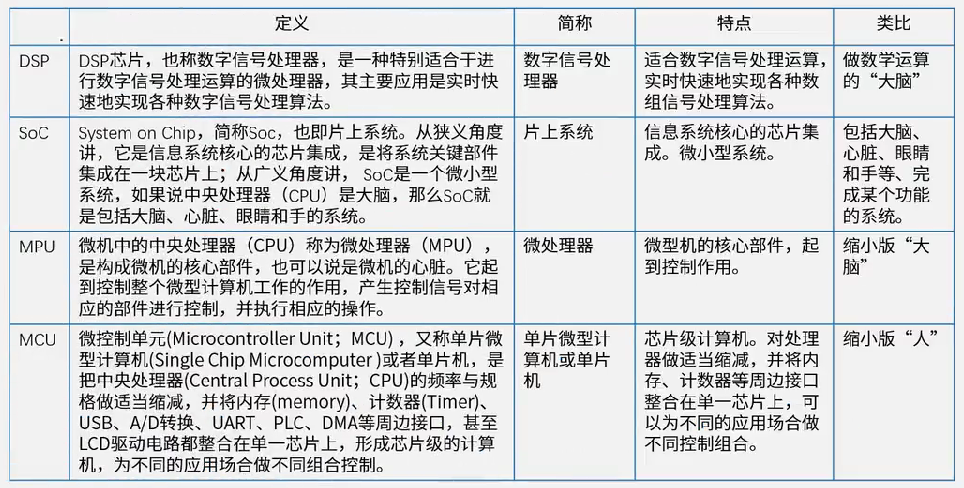

四个容易混淆的概念:

四、层次化存储结构

五、Cache

- Cache 的功能:提高 CPU 数据输入输出的速率,突破冯·诺依曼瓶颈,即 CPU 与存储系统间数据传送带宽限制

- 在计算机的存储系统体系中,Cache 是访问速度最快的层次

- Cache 对程序员来说是透明的,不可见,不可操作的

- 使用 Cache 改善系统性能的依据是程序的局部性原理,包括时间局部性和空间局部性

六、主存编制计算

存储单元

存储单元个数=最大地址-最小地址+1

编址内容

按字编址:存储体的存储单元是字存储单元,即最小寻址单位是一个字

按字节编址:存储体的存储单元是字节存储单元,即最小寻址单位是一个字节

总容量=存储单元个数*编制内容

根据存储器所要求的容量和选定的存储芯片的容量,就可以计算出所需芯片的总数,即:

总片数=总容量/每片的容量

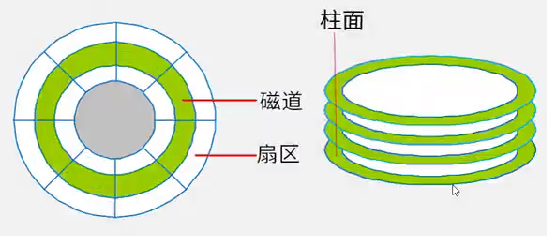

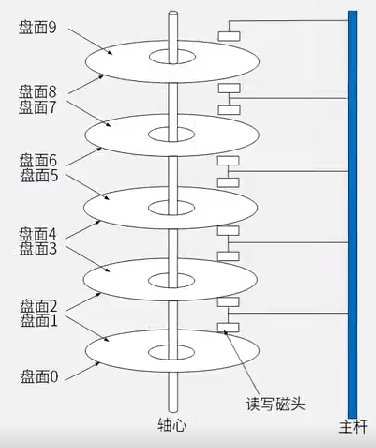

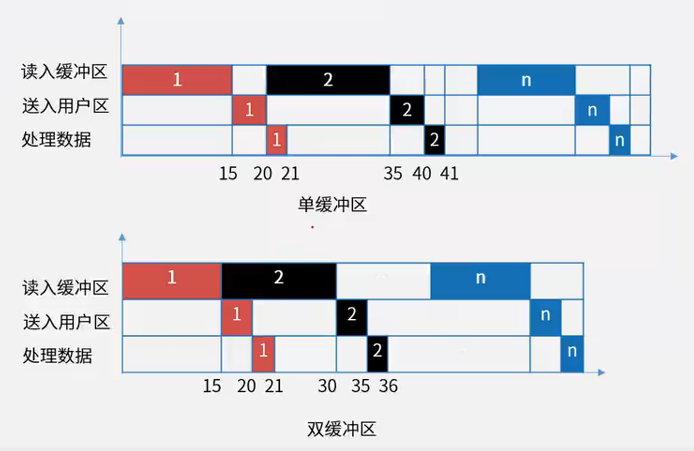

七、磁盘管理

1.磁盘基本结构与存储过程

平均存取时间=平均寻道时间+平均等待时间

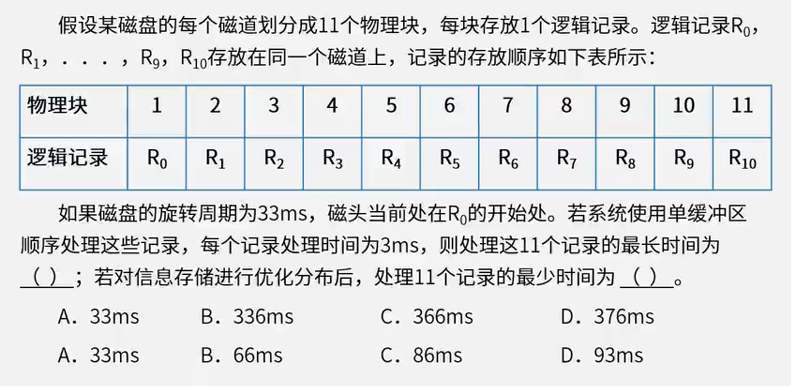

2.磁盘优化分布存储

读取每片物理块所需的时间为 33/11=3ms,然后该物理块就进入了缓冲区。在完全写入缓冲区后,此时又过了 3ms,磁头移动到了下一块物理块的末尾。接着等待磁头旋转到 R1 物理块的起始位置,最长需要30ms,与之前类似,读取 R1 又需要 6ms。因此最长时间为 3611=366ms,那么最少时间只需要 611=66ms

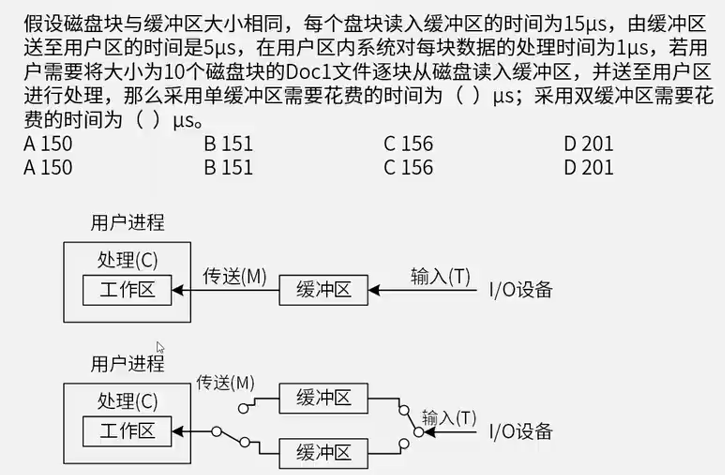

3.磁盘单缓冲区与双缓冲区读取

单缓冲区:(15+5)10+1=201

双缓冲区:1510+1=151

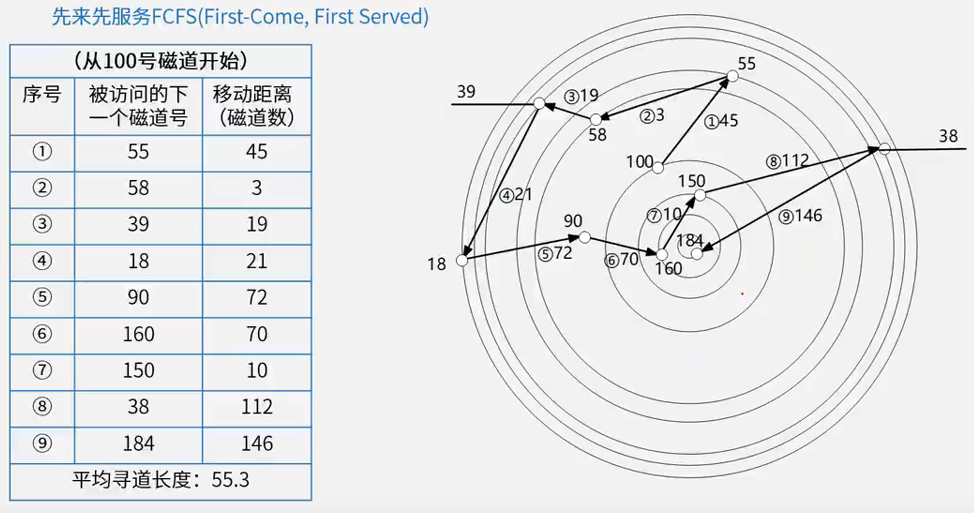

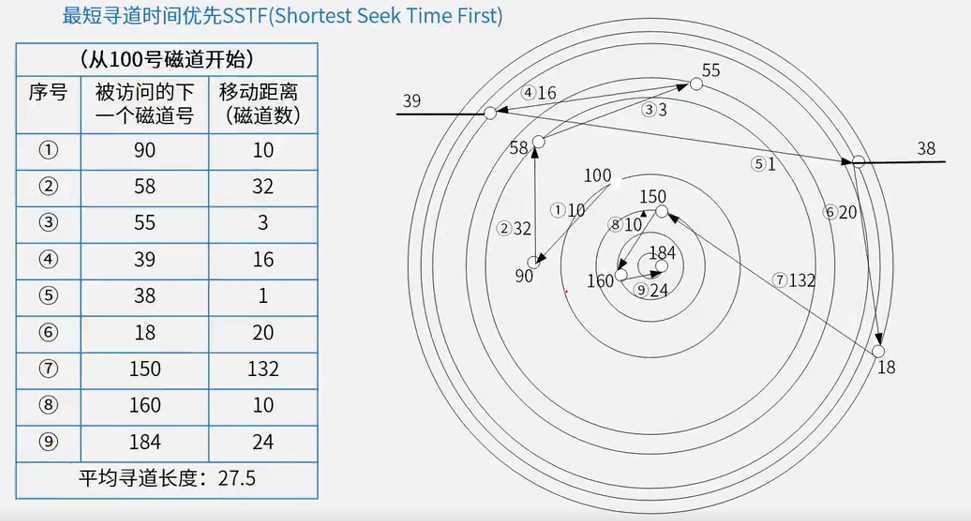

4.磁盘移臂调度算法

磁臂水平旋转永远是同方向的,只有垂直移动寻道时才会有不同的算法

- 先来先服务(FCFS)

- 最短寻道时间优先(SSTF):当前谁最近就先为谁服务

- 扫描算法(SCAN):也叫电梯算法,顾名思义,类似电梯的算法。电梯从 1 层一直到顶层,再从顶层到 1 层

- 循环扫描算法(CSCAN):也就是说,电梯到达最高点时不会接受任何请求,而是直接下到 1 层,再接受请求

八、数据传输控制方式

程序控制(查询)方式

分为无条件传送和程序查询方式两种。方法简单,硬件开销小,但 I/O 速度与 CPU 速度不匹配,严重影响 CPU 的利用率。

- 无条件查询:CPU 默认 I/O 一直是准备好的,要用的时候 CPU 就调用 I/O,显然这种情况太理想化,因此更多使用的是程序查询的方式。

- 程序查询方式:CPU 不断地查询 I/O 是否准备好,准备好了再调用,没有准备好的话,CPU 会持续等待,这个过程会严重影响 CPU 利用率

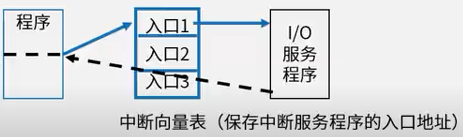

程序中断方式

与程序控制方式相比,中断方式因为 CPU 无需等待而提高了传输请求的响应速度。CPU 收到中断请求后,程序的执行会出现断点,我们会将当前程序的状态放入一个栈中,称为保护现场,这些栈会被记录在中断向量表中。中断处理完成后返回到断点,将我们的保护现场依次恢复

DMA方式

DMA 方式是为了在主存与外设之间实现高速、批量数据交换而设置的。DMA 方式比程序控制方式与中断方式都高效

DMAC 向总线裁决逻辑提出总线请求;CPU 执行完当前总线周期即可释放总线控制权。此时 DMA 响应,通过 DMAC 通知 I/O 接口开始 DMA 传输

通道方式

I/O 处理机

通道方式和 I/O 处理机方式都是通过硬件来实现的,并且这五种方式从上至下,效率越来越高

鼠标键盘采用中断方式,硬盘采用 DMA 方式

九、总线

总线是一组能为多个部件分时共享的公共信息传送线路

- 共享

- 分时:是指同一时刻仅允许一个部件向总线发送信息,但允许多个部件同时从总线上接收相同的信息

总线的分类

- 数据总线(Data Bus,DB):在 CPU 与 RAM 之间来回传送需要处理或是需要储存的数据

- 地址总线(Address Bus,AB):用来指定在 RAM(Random Access Memory)之中储存的数据的地址

- 控制总线(Control Bus,CB):将微处理器控制单元(Control Unit)的信号,传送到周边设备

串行总线适合长距离传输,并行总线适合近距离连接,不宜过长

总线还分为单工、半双工与全双工

总线宽度与总线带宽,总线指的是总线的数量,里面决定了总线所占的物理空间和成本,会影响到数据总线和地址总线,如果地址总线的宽度是 32 位,那么访问的空间大小为 2 的 32 次方,即4GB,因此有一种说法:32 位操作系统应该使用 4GB 的内存。总线带宽会涉及到时间,即单位时间传输的数据大小。总线带宽=总线宽度*频率

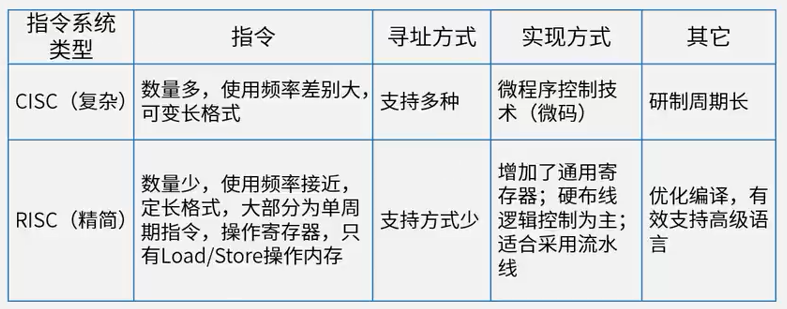

十、CISC 与 RISC

CISC,Complex Instruction Set Computers,复杂指令集计算机

RISC,Reduced Instruction Set Computers,精简指令集计算机

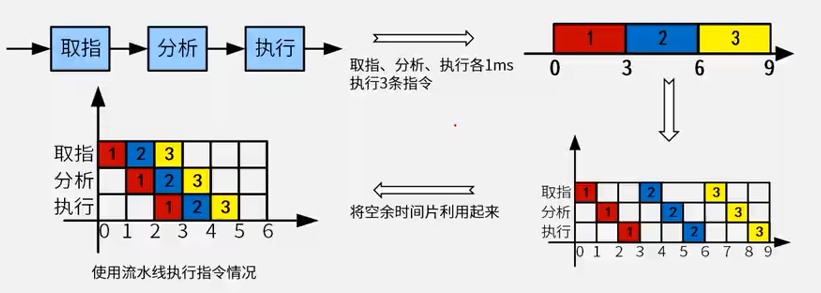

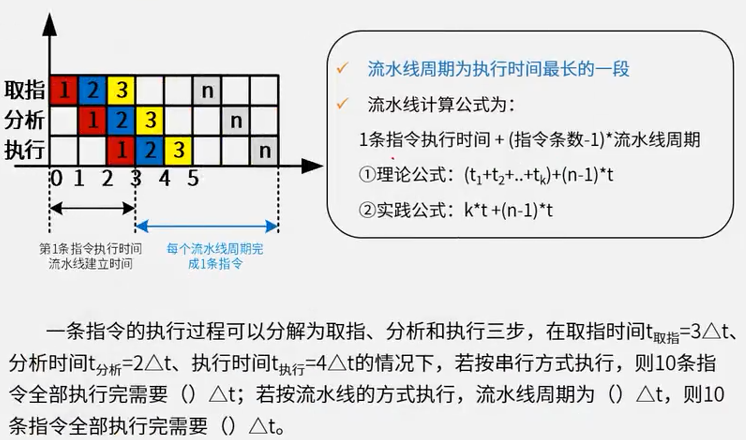

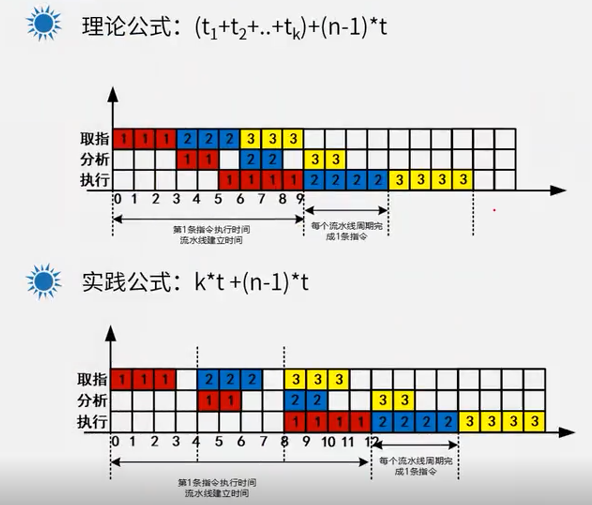

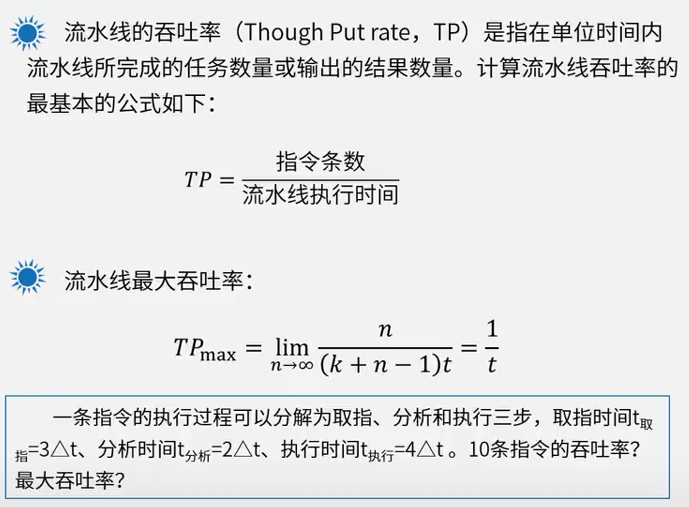

十一、流水线技术

相关参数计算:流水线执行时间计算、流水线吞吐率、流水线加速比等

流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度

用理论公式求出的答案不在选项中时,才用实践公式

1.(3+2+4)*10=90

2.4

3.(3+2+4)+(10-1)4=5+104=45

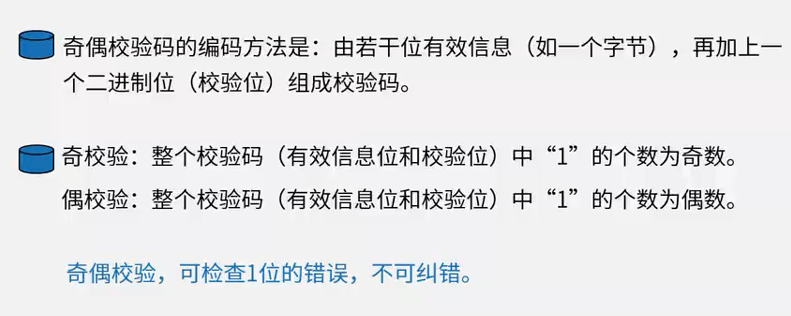

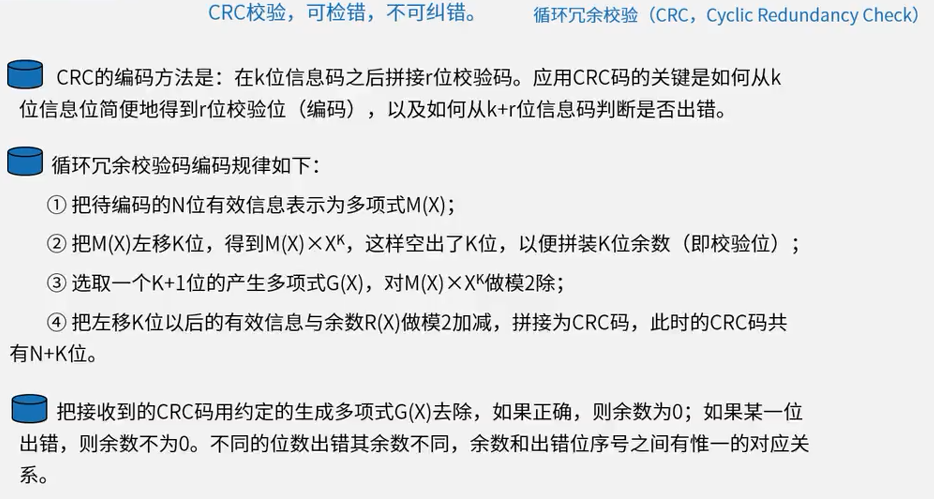

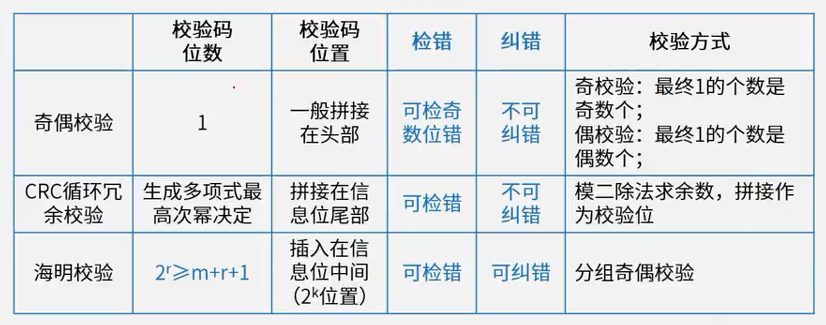

十二、校验码

海明校验仅需要掌握校验码位数的计算公式

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?