一、二进制码转格雷码

给出转换原理:

对于位宽为n的二进制码:

Gray[i]=Bin[i]⊕Bin[i+1]Gray[n]=Bin[n] Gray[i]=Bin[i] \oplus Bin[i+1]\\ Gray[n]=Bin[n] Gray[i]=Bin[i]⊕Bin[i+1]Gray[n]=Bin[n]

举个例子:

| 二进制码 | 1 | 1 | 0 | 1 |

|---|---|---|---|---|

| 格雷码 | 1 | 0 | 1 | 1 |

Verilog如下:

module gray_bin(

input [3:0]bin,

output[3:0] gray_code

);

assign gray_code=bin^(bin>>1);

endmodule

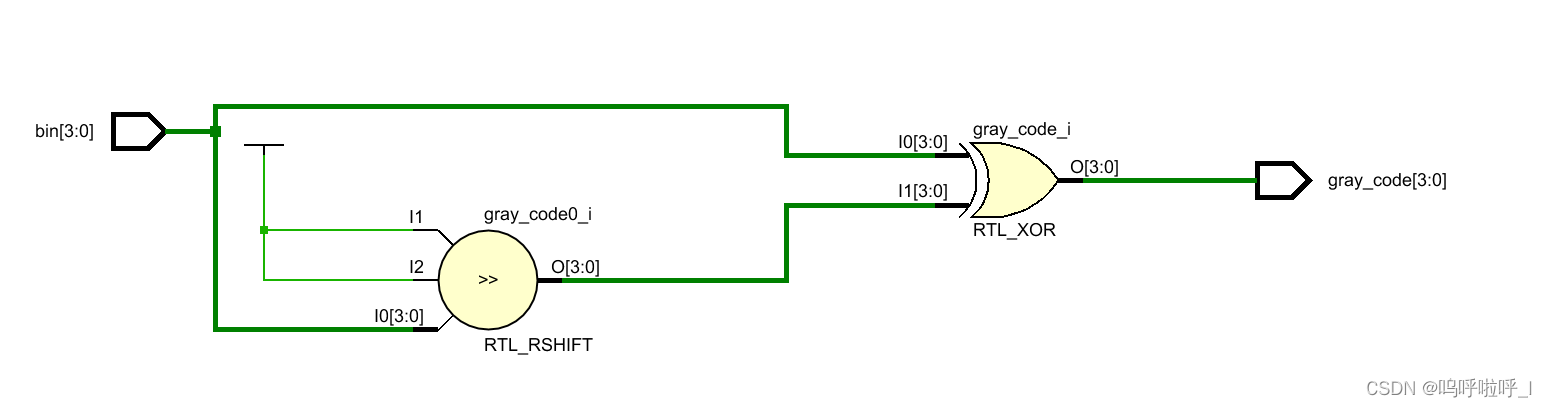

综合电路:

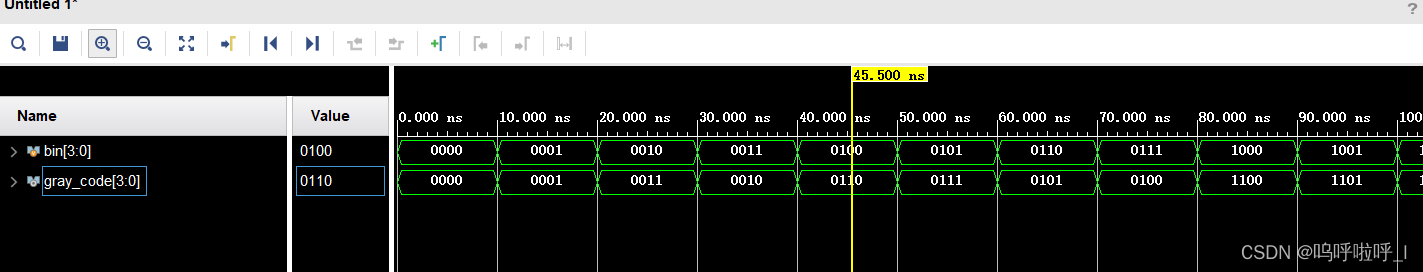

仿真结果:

二、格雷码转二进制码

给出转换原理:

对于位宽为n的二进制码:

$$

Bin[n]=Gray[n] \

Bin[i]=Gray[i] \oplus Bin[i+1]\

$$

将上述式子展开

Bin[3]=Gray[3] Bin[2]=Gray[2]⊕Bin[3]=Gray[2]⊕Gray[3] Bin[1]=Gray[1]⊕Bin[2]=Gray[1]⊕Gray[2]⊕Gray Bin[0]=Gray[0]⊕Bin[1]=Gray[0]⊕Gray[1]⊕Gray[2]⊕Gray[3] Bin[3]=Gray[3]\\ \space\\ Bin[2]=Gray[2] \oplus Bin[3]=Gray[2] \oplus Gray[3]\\ \space\\ Bin[1]=Gray[1] \oplus Bin[2] = Gray[1] \oplus Gray[2] \oplus Gray\\ \space\\ Bin[0]=Gray[0] \oplus Bin[1] =Gray[0] \oplus Gray[1] \oplus Gray[2] \oplus Gray[3] Bin[3]=Gray[3] Bin[2]=Gray[2]⊕Bin[3]=Gray[2]⊕Gray[3] Bin[1]=Gray[1]⊕Bin[2]=Gray[1]⊕Gray[2]⊕Gray Bin[0]=Gray[0]⊕Bin[1]=Gray[0]⊕Gray[1]⊕Gray[2]⊕Gray[3]

举个例子:

| 二进制码 | 1 | 1 | 0 | 1 |

|---|---|---|---|---|

| 格雷码 | 1 | 0 | 1 | 1 |

Verilog如下:

module gray_bin(

input [3:0]gray_code,

output reg [3:0] bin

);

integer i=3;

always@(*)

begin

for(i=0;i<=4;i=i+1)

begin

bin[i]=^(gray_code>>i);

end

end

endmodule

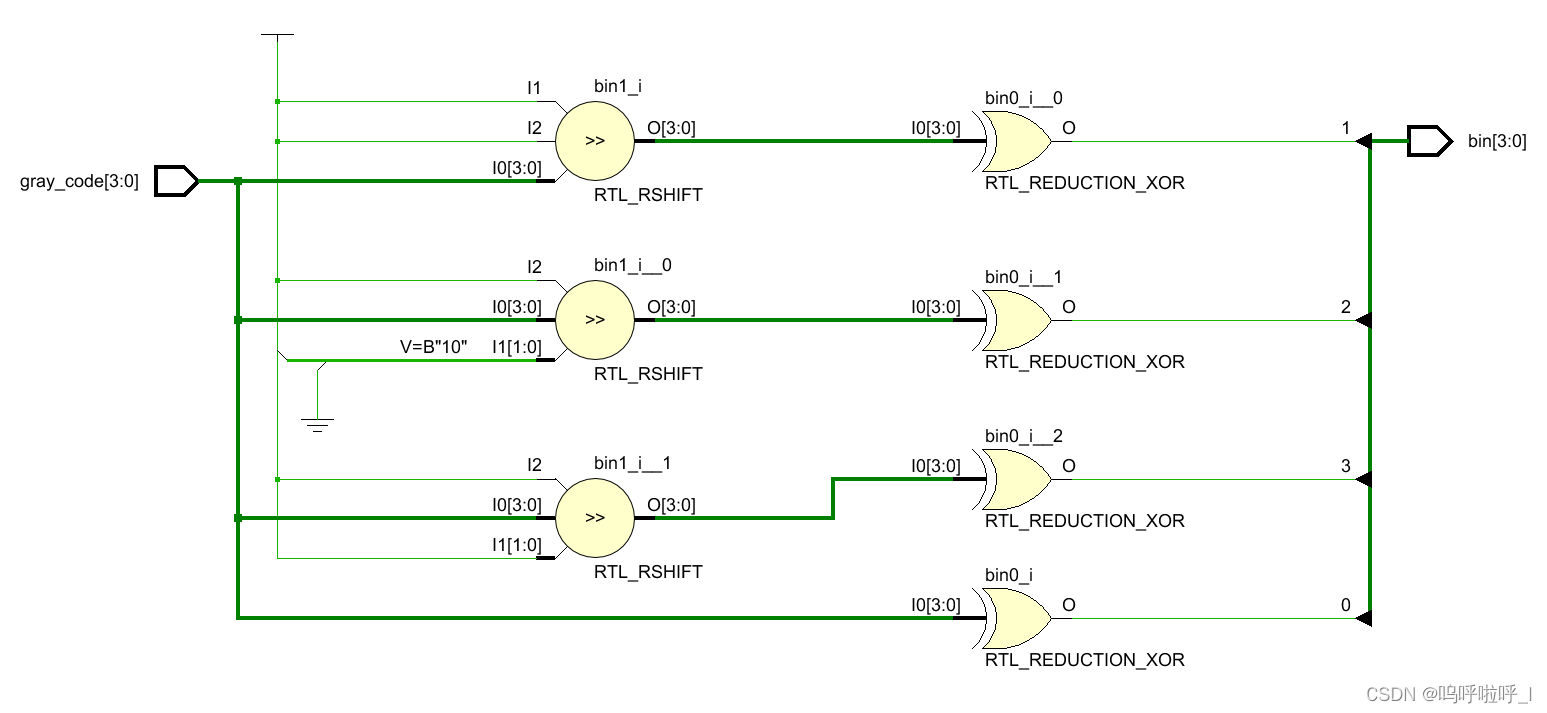

综合电路:

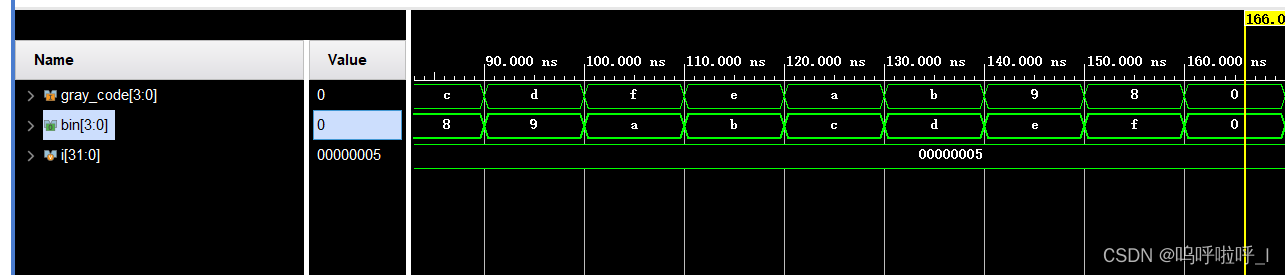

仿真结果:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?