4.7.3 级联型结构的 FPGA 实现

级联型结构的IIR滤波器,实际相当于将级数比较多的滤波器分解成多个阶数小于等于3的IR滤波器,其中的每个滤波器均可以看成独立的结构,只是前一级滤波器的输出作为后一级滤波器的输入而已。由于ⅡR 滤波器的反馈结构,必须要通过仿真确定滤波器输出数据范围,以进一步确定输出数据的位宽。初看起来,这似乎是一件比较困难的事。一个可行的方法是通过 MATLAB来仿真每一级滤波器的输出数据范围,从而确定相应的数据位宽。这里还有一个更为简单的处理方法,因为MATLAB设计出的IR滤波器输出数据范围不会大于输入数据范围(读者可以自己通过编写MATLAB程序仿真查看),也就是说整个IR滤波器的输出数据位宽只需设置成与输入数据的位宽相同即可。通常来讲,IR滤滤波器的增益均小于1,将滤波器增益分配到第一级滤波器实现,则第一级滤波器的输出数据范围定小于输入数据范围,从而各级滤波器的输出数据位宽均可以直接设置成输入数据位宽。

1.分析级联型结构的实现方法

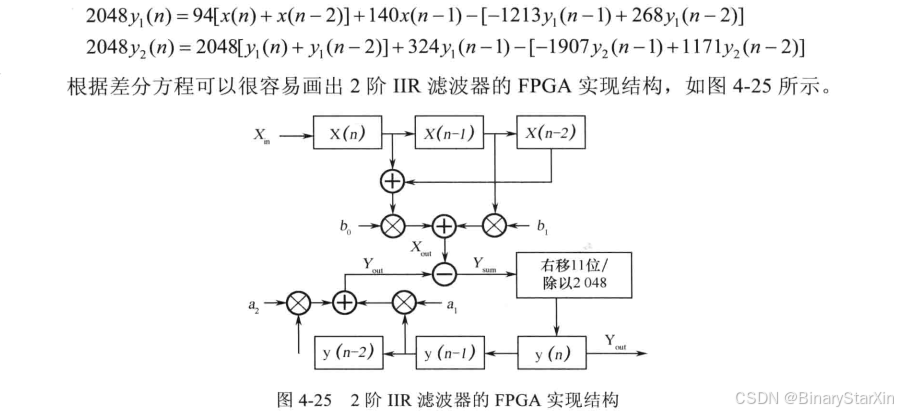

由上一步可知,本实例的4阶ШR滤波器可等效为2个2阶的IR滤波器级联实现,前面已对滤波器系数进行了量化,根据级联型结构可以直接写出滤波器的差分方程。

2.编写

订阅专栏 解锁全文

订阅专栏 解锁全文

1533

1533

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?