前言

在FPGA设计的过程中,有时需要对一些递归的算法进行硬件实现,那么递归调用是否是Verilog所支持的?答案是可以,但是这类算法一般都有比较明确的结构,即递归调用的结构比较清晰明了。那么,我们在RTL代码编写过程中,可以在模块的内部例化当前模块,达到递归调用的目的。

例子

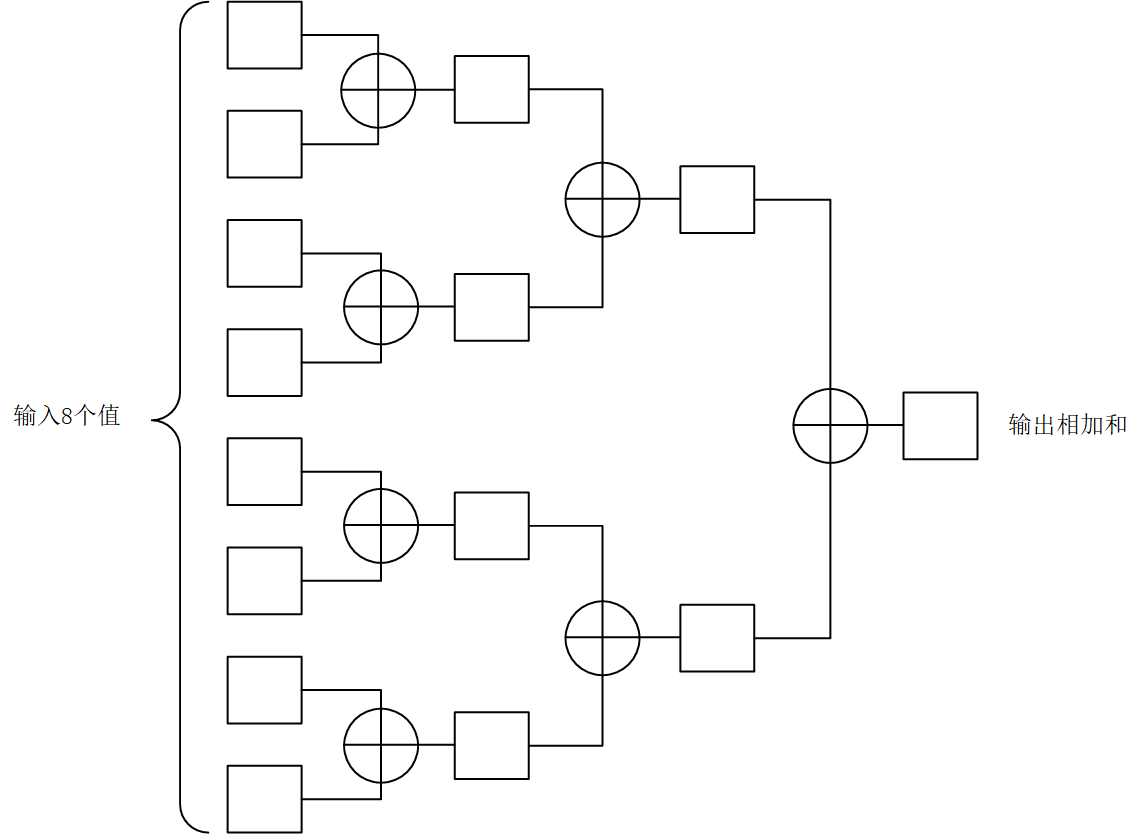

比如,我们设计一个加法器,想要实现如下图的功能,输入N个数据,通过N/2个加法器两两相加,得到N/2个数据,再用N/4个加法器对这N/2个数据进行两两相加,得到N/4个数据…,依此类推,直至计算得到一个数据,即最终计算结果(这里只是用于举例,实际上加法不用这么复杂)。

那么,根据设计要求编写相关代码和测试代码如下。

顶层代码

顶层代码如下:

module test

#(

parameter N = 8,

parameter DW = 8

)

(

clk,

rst_n,

data_in,

data_out

);

input wire clk;

input wire rst_n;

input wire [N*DW-1:0] data_in;

output wire [N*DW-1:0] data_out;

wire [N*DW-1:0] temp;

if(N>2) begin

//1-2-4

test

#(

.N(N/2),

.DW(DW)

)

test_1

(

.clk(clk),

.rst_n(rst_n),

.data_in(data_in[(N/2)*DW-1:

本文介绍如何在FPGA设计中使用Verilog实现递归算法,以加法器为例,展示递归调用的过程及仿真结果。

本文介绍如何在FPGA设计中使用Verilog实现递归算法,以加法器为例,展示递归调用的过程及仿真结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

982

982

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?