3.2 MSP430时钟系统的基本构造

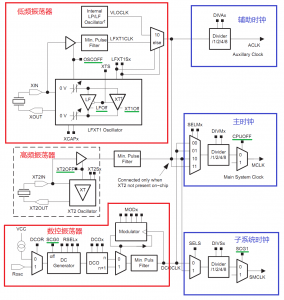

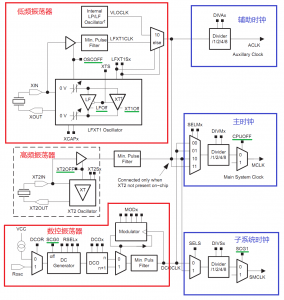

MCLK、SMCLK和ACLK及其来源构造在MSP430G2系列单片机中称为“BasicClock Module+”单元,如下图所示。请注意,不同型号的MSP430,其具体的时钟系统结构可能有所不同,具体请参见芯片datasheet以及各个系列的User’sGuide。

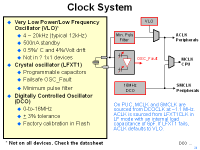

图中左侧是时钟来源,右侧是最终单片机使用的三种时钟。MSP430G2系列单片机的时钟来源有3种,分别是内部低频振荡器VLO、外部晶振LFXT1和内部高频数控振荡器DCO。 DCO是MSP430内部的数字振荡器,MSP430G2553的DCO最高主频可以达到16MHz,主要供CPU和其他一些高速外设使用。DCO的频率可以通过DCOx、MODx和RSELx这几个寄存器位来调整。DCO的精度并不是高,因此如果想要通过DCO获得一个比较精确的时钟频率,必须先进行校准。校准的方法在3.3节中会介绍。 LFXT1是低速外部晶振,频率为32.768kHz。这种晶振俗称“手表晶振”,为什么这么叫呢?是因为这种晶振被广泛用于石英表中。大家可以计算一下,32.768kHz=2^15,因此它的频率非常适合作为实时时钟进行记时,同时它的精度相比DCO也更高。需要注意的是,MSP430G2LaunchPad上的外部晶振在出场时并没有焊接,而是在包装盒中单独提供。用户需要使用外部晶振时需要先将它焊接到LaunchPad上。 VLO是MSP430内置的低频振荡器,它的频率是12kHz左右。VLO的最主要用途是在MSP430进入低功耗模式后作为维持单片机“生命”的时钟源,待MSP430被唤醒后再切换到其他时钟。因此VLO的精度不高,但它的功耗是最低的。请注意当MSP430G2553没有接外部晶振时,系统会自动切换到VLO作为ACLK的时钟源。 在时钟源和系统时钟之间有一系列的选择开关,通过配置这些选择开关(实际操作中是配置寄存器),可以为3种系统时钟选取不同的时钟源。MCLK和SMCLK可以来自3个时钟源中的任意一个,而ACLK只能选择外部晶振或VLO作为时钟源。 出厂默认情况下,MSP430G2553的MCLK和SMCLK来源于DCO,频率约为1.1MHz;而ACLK默认来源于外部晶振(前提是外部晶振已经被焊接),频率为32.768kHz。 3.3 如何配置时钟系统

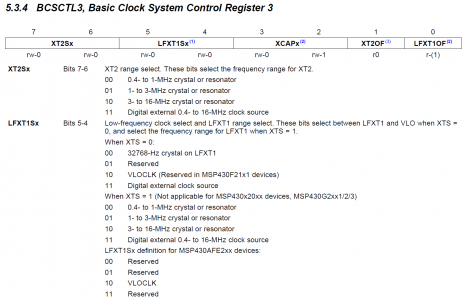

在介绍时钟寄存器之前我们先来看下面一张图,这是MSP430G2系列单片机的时钟系统的详细构造图。图中黑色小方块代表了寄存器的某些位,其上方是对应的名称。通过配置这些寄存器就可以选择时钟源及频率。

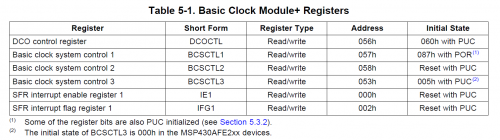

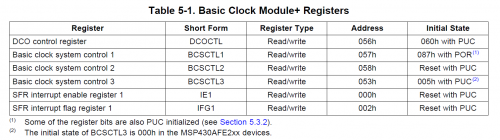

下图是时钟寄存器的列表,上述所有配置位均在DCOCTL、BCSCTL1、BCSCTL2、BCSCTL3这四个寄存器中。四个寄存器具体的定义请见“MSP430x2xxFamily User's guide”的5.3节,这里不一一列举,后面几节中我们将在讲解具体如何配置各个时钟模块时有针对性的介绍。

3.3.1 数控振荡器DCO

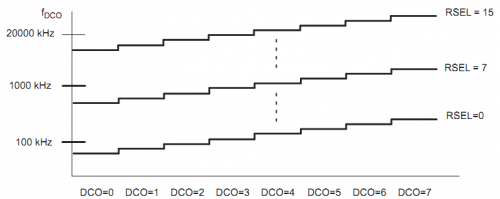

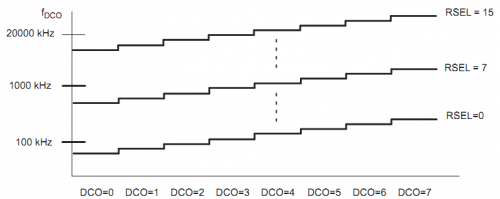

MSP430G2系列只能通过内部数控振荡器DCO来获得高频时钟,不支持外部高频晶振。 DCO 的原理实际是一个开环控制的振荡器,DCO模块内置系列(振荡)电阻,供选择频率范围(RSELx共4位,16档),也就是RSELx负责粗调。接下来是对振荡频率进行分频(DCOx有3位,共8档,档位步进约10%),也就是DCOx负责细调。振荡频率范围和分档的设定示意图如下。

如果粗调和细调仍不满足要求,MSP430单片机还有混频器Modulator,可以交替输出两种DCO频率,将其平均以输出目标频率。寄存器MODx负责控制混频。 大家可能会好奇这样得到的“等效”频率的时钟能用吗?答案是当然有用,可以用于配置通讯的波特率。如果MODx设定值不为0,显然经混频得到的振荡波形在示波器上看将会“抖动”,对于时钟瞬时稳定度要求高的场合应避免使用混频。

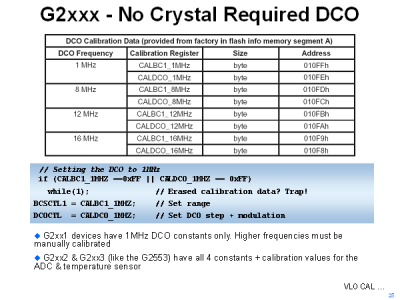

3.3.2 出厂预校正频率

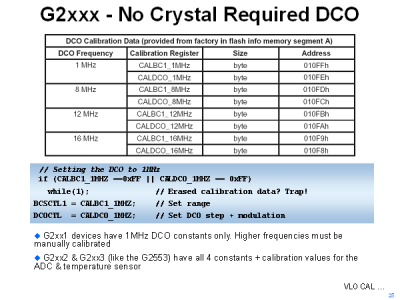

DCO与一些型号MSP430配置的数字锁频环(FLL)不同,DCO并不是一个带反馈的振荡器,而开环输出频率的误差很大。也就是说RSELx的粗调和DCOx的细调都是非线性的。如何保证DCO输出频率精度呢?在出厂时,每一块单片机都校正了4个频率值(1/8/12/16MHz),将这4个频率值的校验参数(RSELx/DCOx/MODx的取值)存在了单片机片内Flash的Info A段中。 下面的代码是将DCO设置为1MHz,实际就是调取出厂校验参数CALBC1_1MHZ和CALDCO_1MHZ。CALBC1_xMHZ和CALDCO_xMHZ这两个宏存储了Flash中记录校正参数的地址,每个单片机的校正参数不一样。利用这两个宏可以直接取得精确的1/8/12/16MHz的时钟频率。

- void BCSplus_init(void)

- {

- ...

- BCSCTL1 = CALBC1_1MHZ; // Set DCO to 1MHz

- DCOCTL = CALDCO_1MHZ;

- ...

- }

复制代码 同样也可以类似的将频率设置为8/12/16MHz,具体的宏定义如下图。

3.5.png (50.58 KB, 下载次数: 1) 下载附件 2019-1-22 15:43 上传 有了这4个常用频率,再配合分频寄存器DIVA、DIVS和DIVM,我们就可以很方便的将时钟设置为想要的频率。 3.4 时钟系统配置实例

下面我们就来举几个例子,学习如何配置时钟。 首先请大家再来回顾一下,默认情况下MSP430G2553单片机的MCLK和SMCLK都来源于DCO,频率约为1.1MHz;ACLK来源于外部晶振,频率为32.768kHz。请特别注意默认的MCLK和SMCLK的频率是未经校正的,如果需要精确地1MHz,还是要用上一节学到的指令来配置。另外ACLK默认的外部晶振如果电路板上没有焊接的话,单片机会自动切换到内部VLO。 例1 将MSP430G2553的时钟设置为:MCLK和SMCLK均为1MHz,ACLK设为32.768kHz

- BCSCTL1 = CALBC1_1MHZ; // 要取得精确的1MHz,一定要调取校正参数

- DCOCTL = CALDCO_1MHZ; // ACLK保持默认即可

复制代码 例2 将MSP430G2553的时钟设置为:MCLK和SMCLK均为16MHz,ACLK设为VLO

- BCSCTL1 = CALBC1_16MHZ; // 调取16MHz校正参数

- DCOCTL = CALDCO_16MHZ;

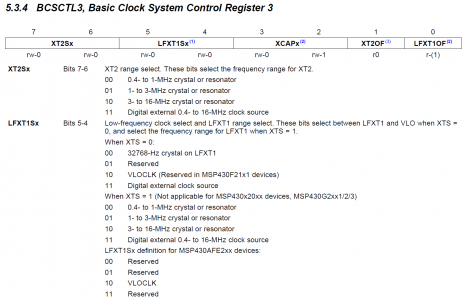

- BCSCTL3 |= LFXT1S_2; // 设为VLO

复制代码 低频晶振源是由BCSCTL3中的LFXT1Sx控制的。将LFXT1Sx置为10即可用VLO作为低频时钟源。

在MSP430G2553.h头文件中,可以找到寄存器对应的宏定义:

- #define LFXT1S_0 (0x00) /* Mode 0 for LFXT1 : Normal operation */

- #define LFXT1S_1 (0x10) /* Mode 1 for LFXT1 : Reserved */

- #define LFXT1S_2 (0x20) /* Mode 2 for LFXT1 : VLO */

- #define LFXT1S_3 (0x30) /* Mode 3 for LFXT1 : Digital input signal */

复制代码 例3 将MSP430G2553的时钟设置为:MCLK为4MHz,SMCLK为2MHz

- BCSCTL1 = CALBC1_8MHZ; // 先将DCO设为8MHz

- DCOCTL = CALDCO_8MHZ;

- BCSCTL2 |= DIVM_1 + DIVS_2; // 再对MCLK 2分频,SMCLK 4分频

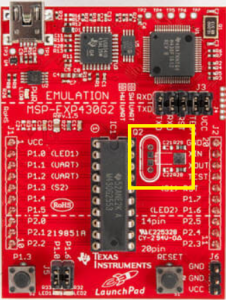

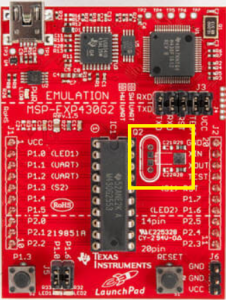

复制代码 MSP430G2单片机出厂时没有提供4MHz和2MHz的校正参数,但我们可以灵活利用分频功能来得到想要的频率。先将DCO频率设为8MHz,再将DIVM和DIVS寄存器设为2分频和4分频,即可得到4MHz和2MHz的频率。 例4 将MSP430G2553的时钟设置为:MCLK设为32.768kHz外部晶振 MSP430G2553包装中提供了一个32.768kHz的外部晶振,但出厂时未焊接。要使用外部晶振,需要将晶振焊接在LaunchPadQ2处。另外晶振要想起振,需要配合2个12.5pF的外围电容。MSP430G2553内部专门内置了电容配合晶振使用,以减少外围电路复杂程度。BCSCTL3寄存器的XCAPx可以配置此电容。

如果想要使用外部晶振或是VLO作为MCLK和SMCLK的时钟源,除了配置寄存器之外,还要注意一定的操作顺序。在“MSP430x2xxFamily User's guide”的5.2.7.1节详细介绍了如何将MCLK配置为外部晶振,具体步骤如下: 1) 开启晶振并设置为合适的模式; 2) 清除OFIFG标志位; 3) 等待至少50us; 4) 检查OFIFG,如果未能清除成功则重复2-4步骤。 其中OFIFG是MSP430的低频晶振失效标志位,如果外部晶振或是内部VLO晶振发生故障,此位将被置为高电平,且单片机会自动切换DCO作为MCLK的时钟源。当MSP430上电时OFIFG也会被置为高电平,因此在设置外部晶振或是VLO作为MCLK时钟源时,必须先将OFIFG清除。 本例具体代码如下:

- ...

- BCSCTL3 |= LFXT1S_0 + XCAP_3; // clock system setup

- while(IFG1 & OFIFG) // wait for OSCFault to clear

- {

- IFG1 &= ~OFIFG;

- _delay_cycles(100000);

- }

- _bis_SR_register(SCG1 + SCG0); // clock system setup

- BCSCTL2 |= SELM_3;

- ...

复制代码 本文参考:https://e2echina.ti.com/group/universityprogram/students/f/11/p/149721/424157#424157 |

本文详细介绍了MSP430单片机的时钟系统,包括MCLK、SMCLK和ACLK三个主要时钟的工作原理,以及如何通过配置内部数控振荡器DCO来获得精确的时钟频率。

本文详细介绍了MSP430单片机的时钟系统,包括MCLK、SMCLK和ACLK三个主要时钟的工作原理,以及如何通过配置内部数控振荡器DCO来获得精确的时钟频率。

1510

1510

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?