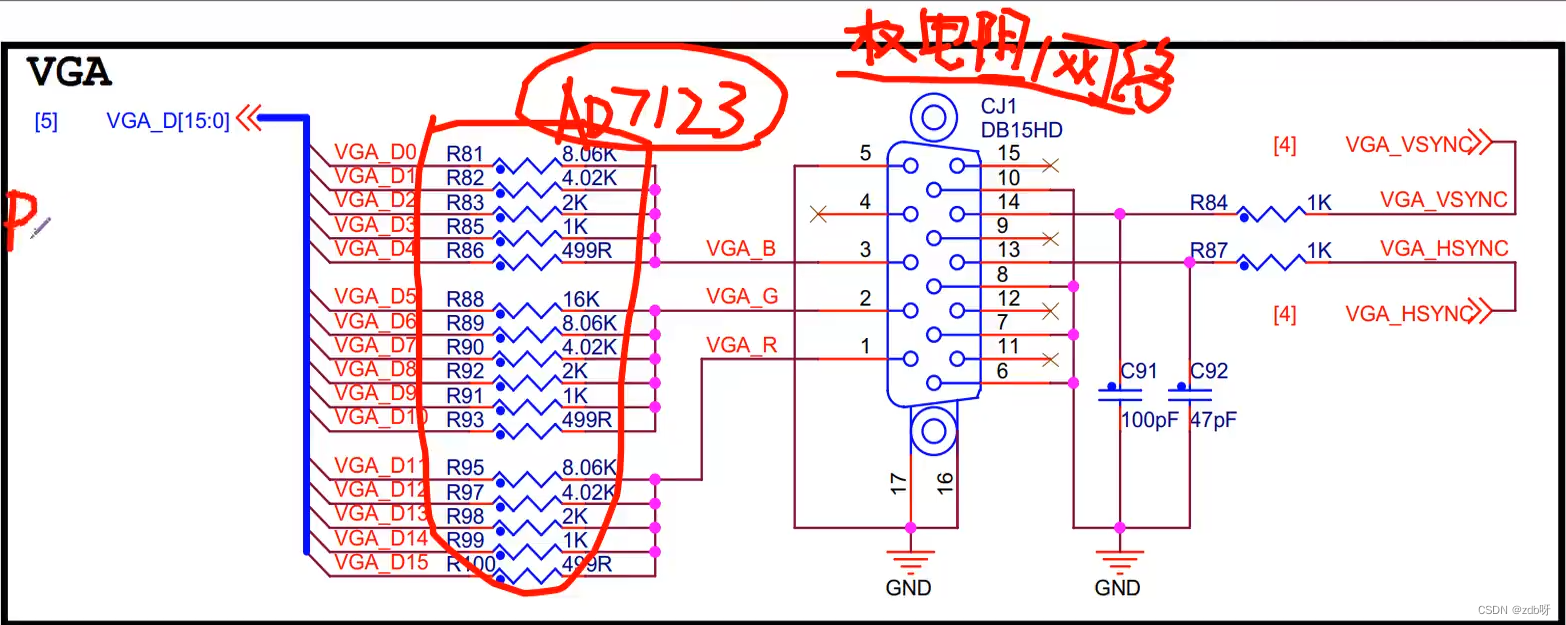

第29讲:VGA显示器驱动设计与验证

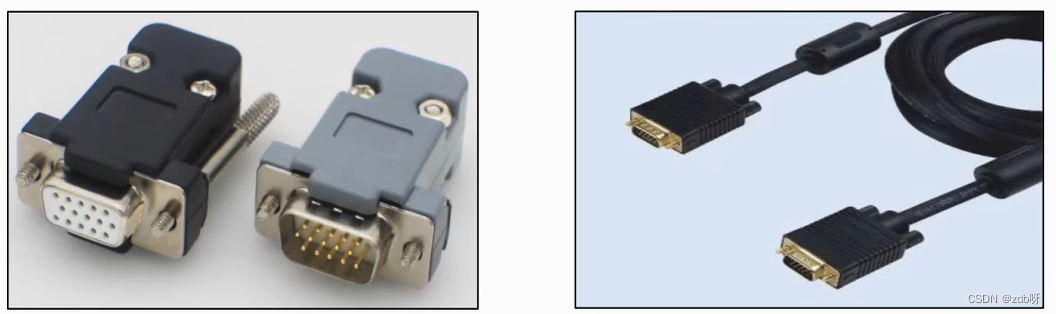

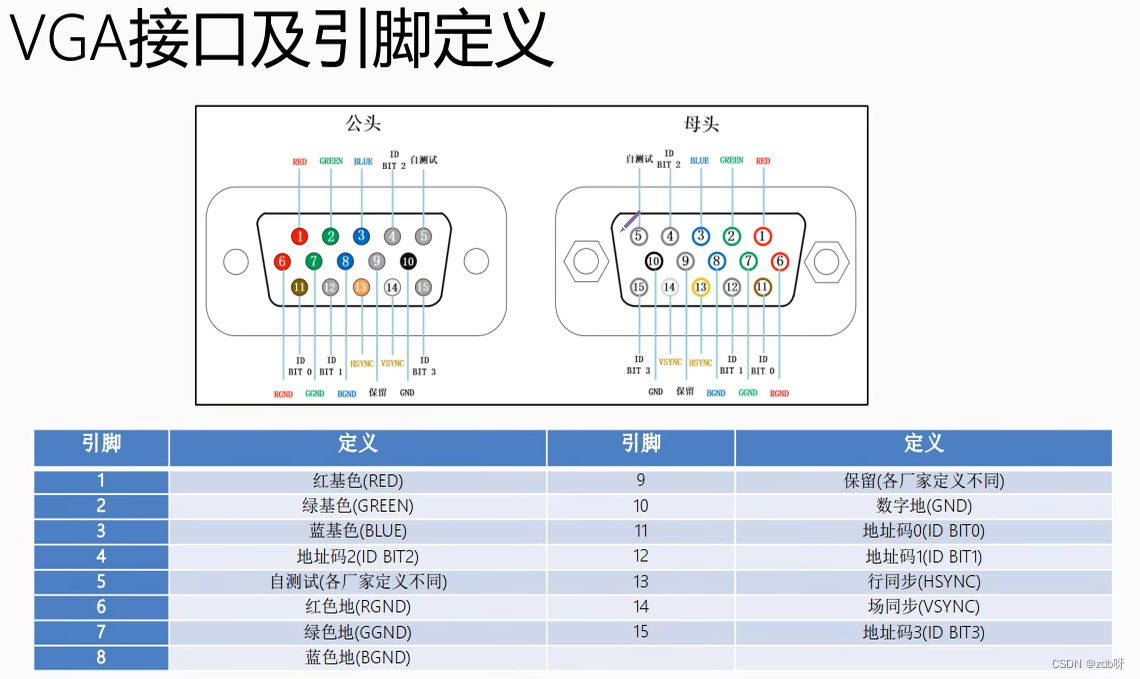

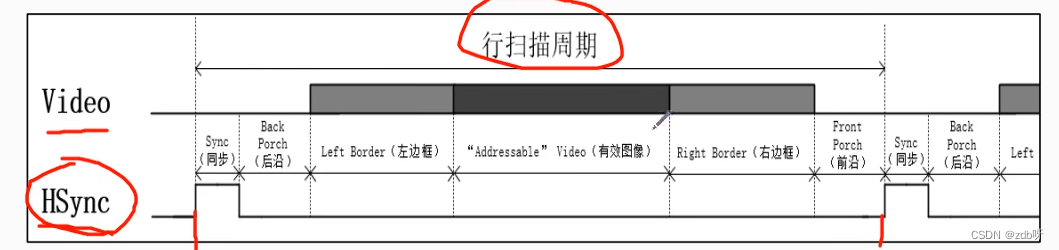

VGA,(Video Graphics Array,即视频图形阵列),是一种使用模拟信号进行视频传输的标准协议,由IBM公司与1987年推出,因其分辨率高、显示速度块、颜色丰富等优点,广泛应用于彩色显示器领域。

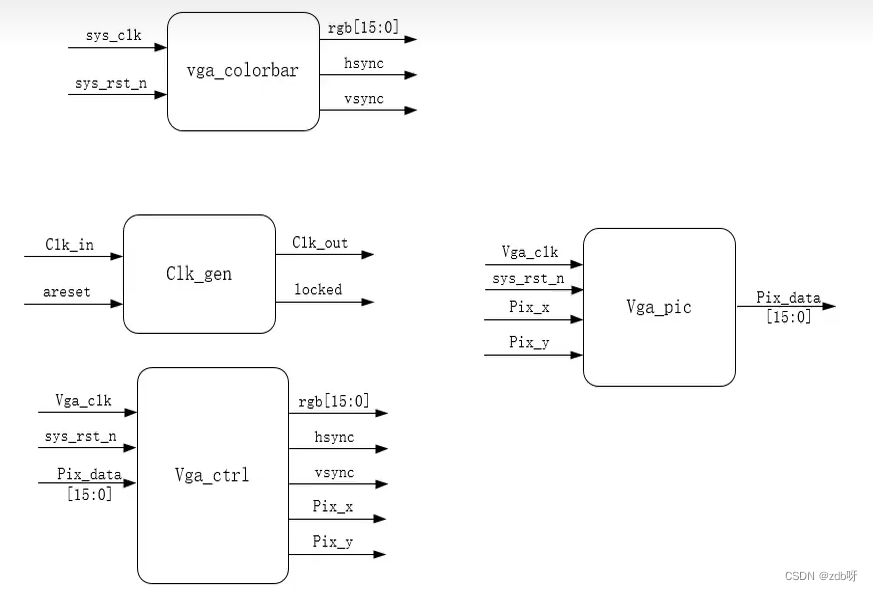

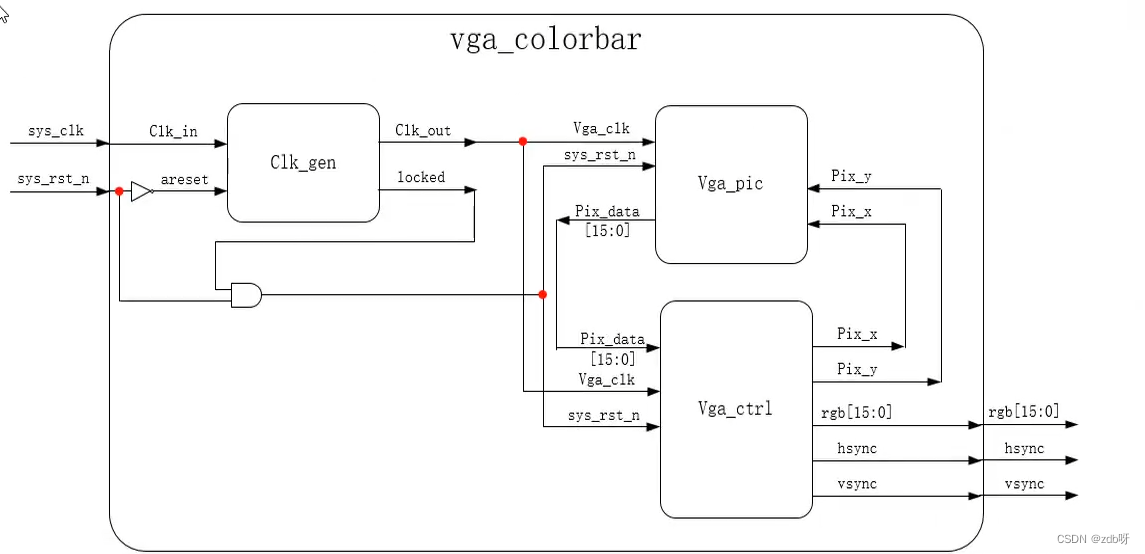

子功能模块划分

系统框图设计

vga_ctrl

`timescale 1ns/1ns

module vga_ctrl

(

input wire vga_clk , //输入工作时钟,频率25MHz

input wire sys_rst_n , //输入复位信号,低电平有效

input wire [15:0] pix_data , //输入像素点色彩信息

output wire [9:0] pix_x , //输出VGA有效显示区域像素点X轴坐标

output wire [9:0] pix_y , //输出VGA有效显示区域像素点Y轴坐标

output wire hsync , //输出行同步信号

output wire vsync , //输出场同步信号

output wire [15:0] rgb //输出像素点色彩信息

);

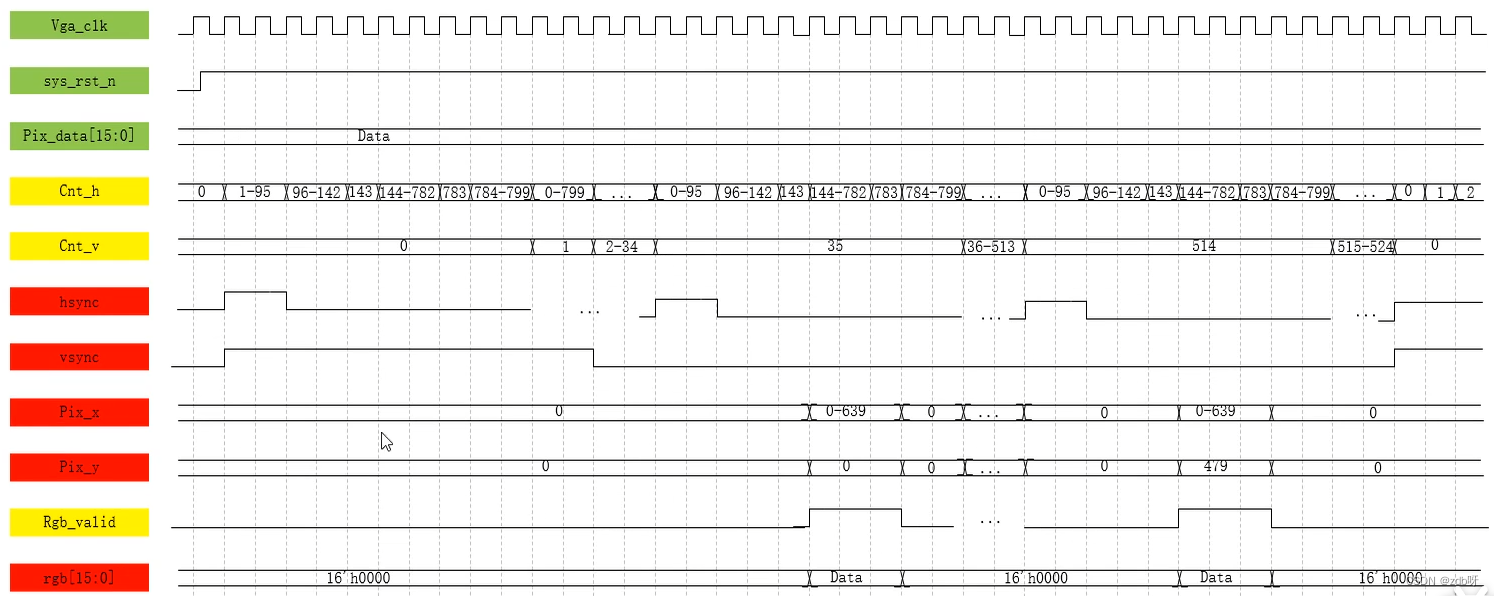

//parameter define

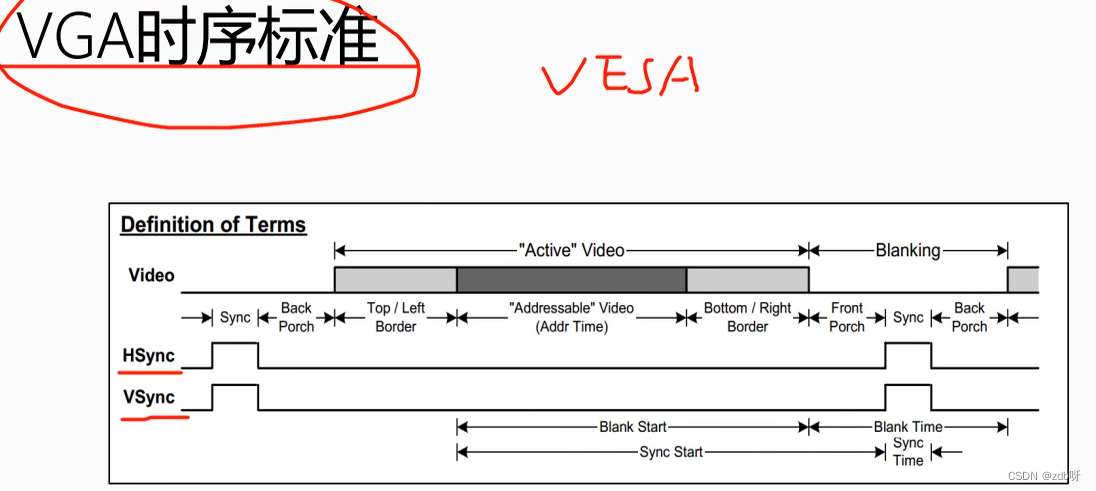

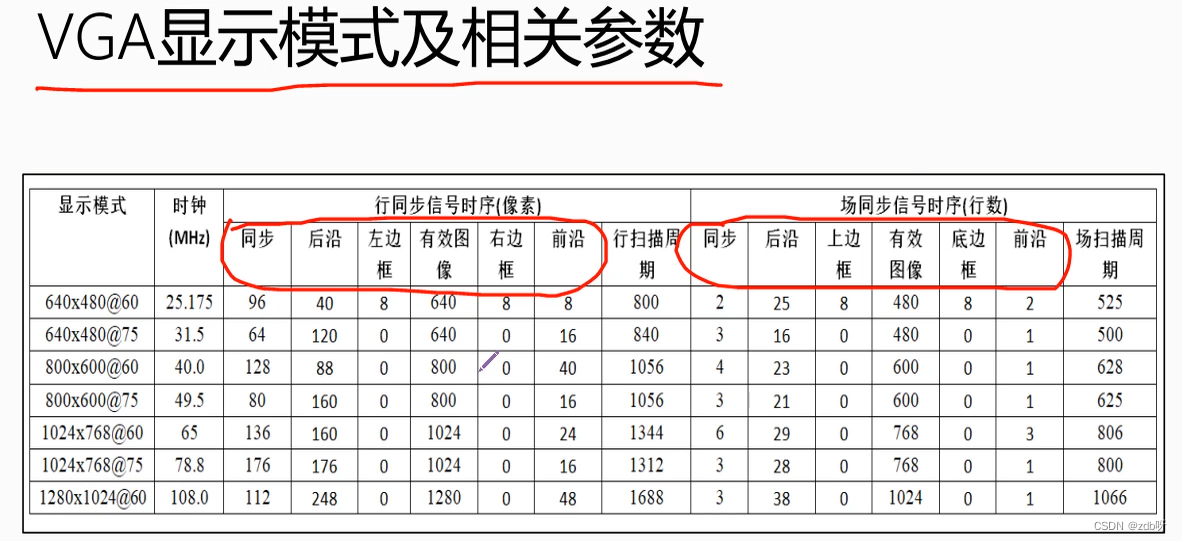

parameter H_SYNC = 10'd96 , //行同步

H_BACK = 10'd40 , //行时序后沿

H_LEFT = 10'd8 , //行时序左边框

H_VALID = 10'd640 , //行有效数据

H_RIGHT = 10'd8 , //行时序右边框

H_FRONT = 10'd8 , //行时序前沿

H_TOTAL = 10'd800 ; //行扫描周期

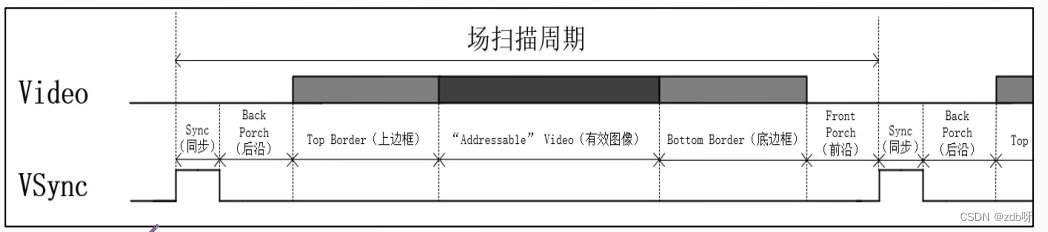

parameter V_SYNC = 10'd2 , //场同步

V_BACK = 10'd25 , //场时序后沿

V_TOP = 10'd8 , //场时序上边框

V_VALID = 10'd480 , //场有效数据

V_BOTTOM = 10'd8 , //场时序下边框

V_FRONT = 10'd2 , //场时序前沿

V_TOTAL = 10'd525 ; //场扫描周期

//wire define

wire rgb_valid ; //VGA有效显示区域

wire pix_data_req ; //像素点色彩信息请求信号

//reg define

reg [9:0] cnt_h ; //行同步信号计数器

reg [9:0] cnt_v ; //场同步信号计数器

//cnt_h:行同步信号计数器

always@(posedge vga_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_h <= 10'd0 ;

else if(cnt_h == H_TOTAL - 1'd1)

cnt_h <= 10'd0 ;

else

cnt_h <= cnt_h + 1'd1 ;

//hsync:行同步信号

assign hsync = (cnt_h <= H_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//cnt_v:场同步信号计数器

always@(posedge vga_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_v <= 10'd0 ;

else if((cnt_v == V_TOTAL - 1'd1) && (cnt_h == H_TOTAL-1'd1))

cnt_v <= 10'd0 ;

else if(cnt_h == H_TOTAL - 1'd1)

cnt_v <= cnt_v + 1'd1 ;

else

cnt_v <= cnt_v ;

//vsync:场同步信号

assign vsync = (cnt_v <= V_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//rgb_valid:VGA有效显示区域

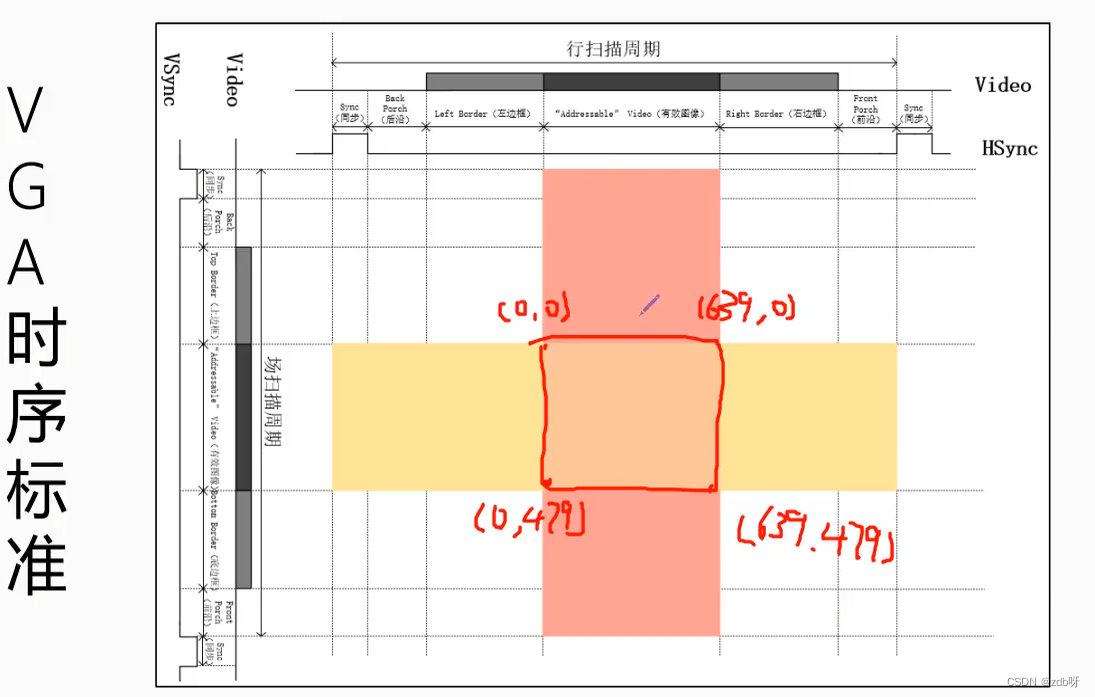

assign rgb_valid = (((cnt_h >= H_SYNC + H_BACK + H_LEFT)

&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID))

&&((cnt_v >= V_SYNC + V_BACK + V_TOP)

&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))

? 1'b1 : 1'b0;

//pix_data_req:像素点色彩信息请求信号,超前rgb_valid信号一个时钟周期

assign pix_data_req = (((cnt_h >= H_SYNC + H_BACK + H_LEFT - 1'b1)

&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID - 1'b1))

&&((cnt_v >= V_SYNC + V_BACK + V_TOP)

&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))

? 1'b1 : 1'b0;

//pix_x,pix_y:VGA有效显示区域像素点坐标

assign pix_x = (pix_data_req == 1'b1) ? (cnt_h - (H_SYNC + H_BACK + H_LEFT - 1'b1)) : 10'h3ff;

assign pix_y = (pix_data_req == 1'b1) ? (cnt_v - (V_SYNC + V_BACK + V_TOP)) : 10'h3ff;

//rgb:输出像素点色彩信息

assign rgb = (rgb_valid == 1'b1) ? pix_data : 16'b0 ;

endmodule

`timescale 1ns/1ns

module tb_vga_ctrl();

//wire define

//wire locked ;

//wire rst_n ;

//wire vga_clk ;

//reg define

reg sys_clk ;

reg sys_rst_n ;

reg [15:0] pix_data ;

//sys_clk,sys_rst_n初始赋值

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#200

sys_rst_n <= 1'b1;

end

//sys_clk:产生时钟

always #20 sys_clk = ~sys_clk;

//rst_n:VGA模块复位信号

//assign rst_n = (sys_rst_n & locked);

//pix_data:输入像素点色彩信息

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

pix_data <= 16'h0;

else

pix_data <= 16'hffff;

//------------- clk_gen_inst -------------

/* clk_gen clk_gen_inst

(

.areset (~sys_rst_n ), //输入复位信号,高电平有效,1bit

.inclk0 (sys_clk ), //输入50MHz晶振时钟,1bit

.c0 (vga_clk ), //输出VGA工作时钟,频率25Mhz,1bit

.locked (locked ) //输出pll locked信号,1bit

); */

//------------- vga_ctrl_inst -------------

vga_ctrl vga_ctrl_inst

(

.vga_clk (sys_clk ), //输入工作时钟,频率25MHz,1bit

.sys_rst_n (sys_rst_n ), //输入复位信号,低电平有效,1bit

.pix_data (pix_data ), //输入像素点色彩信息,16bit

.pix_x (pix_x ), //输出VGA有效显示区域像素点X轴坐标,10bit

.pix_y (pix_y ), //输出VGA有效显示区域像素点Y轴坐标,10bit

.hsync

本文详细介绍了VGA显示器驱动的设计与实现,包括VGA控制器、像素颜色映射及字符显示等核心模块。通过参数配置实现了不同分辨率下的同步信号生成,并展示了如何根据坐标设置像素颜色。

本文详细介绍了VGA显示器驱动的设计与实现,包括VGA控制器、像素颜色映射及字符显示等核心模块。通过参数配置实现了不同分辨率下的同步信号生成,并展示了如何根据坐标设置像素颜色。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3727

3727

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?