在PCB设计中,以下类型的信号线通常需要进行阻抗匹配,以确保信号完整性和系统稳定性:

一、必须进行阻抗匹配的信号类型

1. 高速数字信号

- 典型应用:

- USB 2.0/3.0/4.0(差分对)

- HDMI/DisplayPort(视频传输)

- PCIe/SATA(高速串行总线)

- DDR3/DDR4/DDR5内存总线

- 要求:

- 单端阻抗:50Ω(如时钟线);

- 差分阻抗:90Ω(USB)、100Ω(HDMI)、85Ω(PCIe Gen4)。

2. 射频(RF)信号

- 典型应用:

- 天线馈线(如Wi-Fi、蓝牙、4G/5G模块);

- 射频前端(PA、LNA连接线);

- 微波电路(如雷达、卫星通信)。

- 要求:

- 标准阻抗:50Ω(多数射频系统)或75Ω(视频传输);

- 误差控制:±10%以内(高精度射频需±5%)。

3. 差分信号对

- 典型应用:

- 以太网(100Ω差分对);

- LVDS(低压差分信号,100Ω);

- MIPI(摄像头/显示接口)。

- 要求:

- 严格保持差分阻抗一致性,线长误差≤5mil(0.127mm)。

4. 高频模拟信号

- 典型应用:

- 视频信号(如CVBS、YPbPr,75Ω);

- 高速ADC/DAC模拟输入输出;

- 高频传感器信号(如超声波、激光测距)。

- 要求:

- 单端阻抗匹配,减少反射和失真。

5. 关键控制信号

- 典型应用:

- 系统时钟(如25MHz/100MHz晶振输出);

- 高速控制线(如SPI/I2C在超频模式下);

- 复位信号(高频干扰敏感场景)。

- 要求:

- 根据信号边沿速率(Edge Rate)确定是否需要阻抗控制。

二、阻抗匹配设计要点

1. 传输线模型选择

- 微带线(Microstrip):

- 表层走线,成本低,适合数字信号。

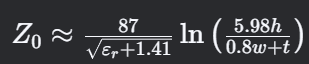

- 阻抗公式:

,其中 ( h ) 为介质厚度,( w ) 为线宽,( t ) 为铜厚。

- 带状线(Stripline):

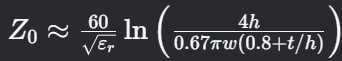

- 内层走线,屏蔽性好,适合射频和高速信号。

- 阻抗公式:

2. 关键设计参数

| 参数 | 影响 | 典型值 |

|---|---|---|

| 线宽(w) | 线宽越窄,阻抗越高 | 4mil(0.1mm)@50Ω(FR4,1.6mm) |

| 介质厚度(h) | 厚度越大,阻抗越高 | 常用48mil(0.10.2mm) |

| 铜厚(t) | 铜厚增加,阻抗降低 | 1oz(35μm)或0.5oz(17.5μm) |

| 介电常数(εr) | 材料选择(FR4≈4.2,Rogers≈3.0) | 高频板材需低εr |

3. 工具与验证

- 阻抗计算工具:Polar SI9000、Altium阻抗计算器、ADS。

- PCB制造标注:在Gerber文件中注明阻抗要求和测试条位置。

- 实测验证:使用TDR(时域反射计)测试实际阻抗。

三、常见误区与解决方案

| 误区 | 问题 | 解决方案 |

|---|---|---|

| “低频信号不需要阻抗匹配” | 边沿速率快(如>1ns)仍需控制 | 计算信号带宽 ( f_{3dB}=0.35/t_r ) |

| “差分对只需控制线宽” | 线距和耦合度同样关键 | 使用差分阻抗计算工具,优化线距(S) |

| “阻抗误差±20%可接受” | 高速信号需严格容差(如±10%) | 与PCB厂商确认工艺能力,选择高精度板材 |

四、典型场景设计示例

1. USB 3.0差分对设计

- 目标阻抗:90Ω差分;

- 叠层:FR4,6层板,L2为参考地;

- 参数:

- 线宽/线距:5mil/5mil;

- 介质厚度:4mil;

- 铜厚:0.5oz。

2. 50Ω射频微带线设计

- 目标阻抗:50Ω单端;

- 板材:Rogers RO4350B(εr=3.66);

- 参数:

- 线宽:20mil;

- 介质厚度:8mil;

- 铜厚:1oz。

五、总结

需进行阻抗匹配的信号线包括 高速数字信号、射频线、差分对、高频模拟信号及关键控制信号。设计时需:

- 根据信号类型选择传输线模型;

- 使用工具计算线宽、线距和叠层参数;

- 标注制造要求并实测验证;

- 避免常见误区(如忽略边沿速率影响)。

通过精准的阻抗控制,可有效减少信号反射、串扰和失真,提升系统性能和可靠性。

766

766

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?