cpu

算术部件与运算器

需解决的问题:如何以加法器为基础,实现各种类型的算术逻辑运算处理。

解决思路:

复杂运算——>四则运算——>加法运算

解决方法:在加法器的基础上,增加移位传送功能,并且输入运算控制条件

加法单元

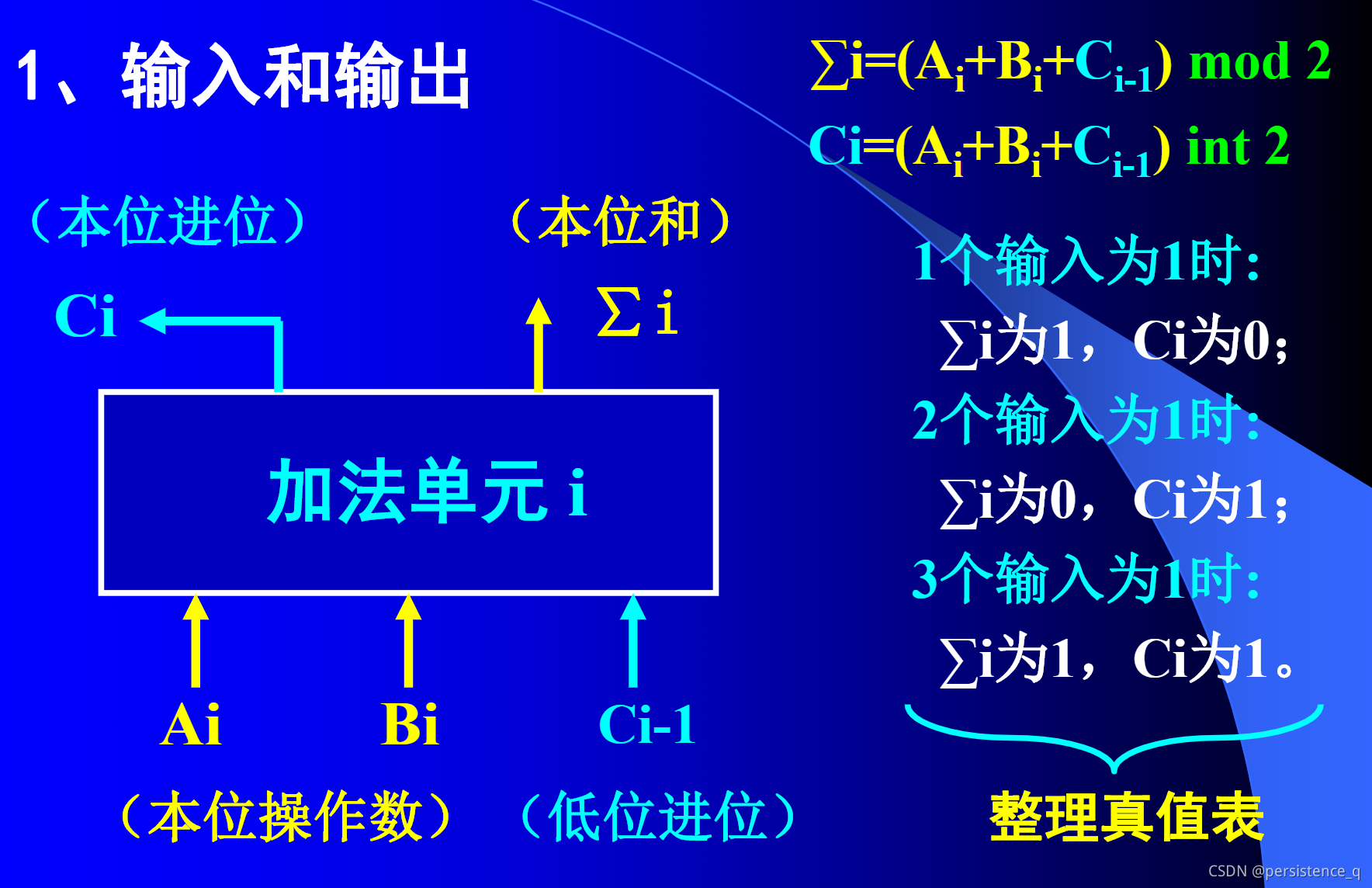

1.输入和输出

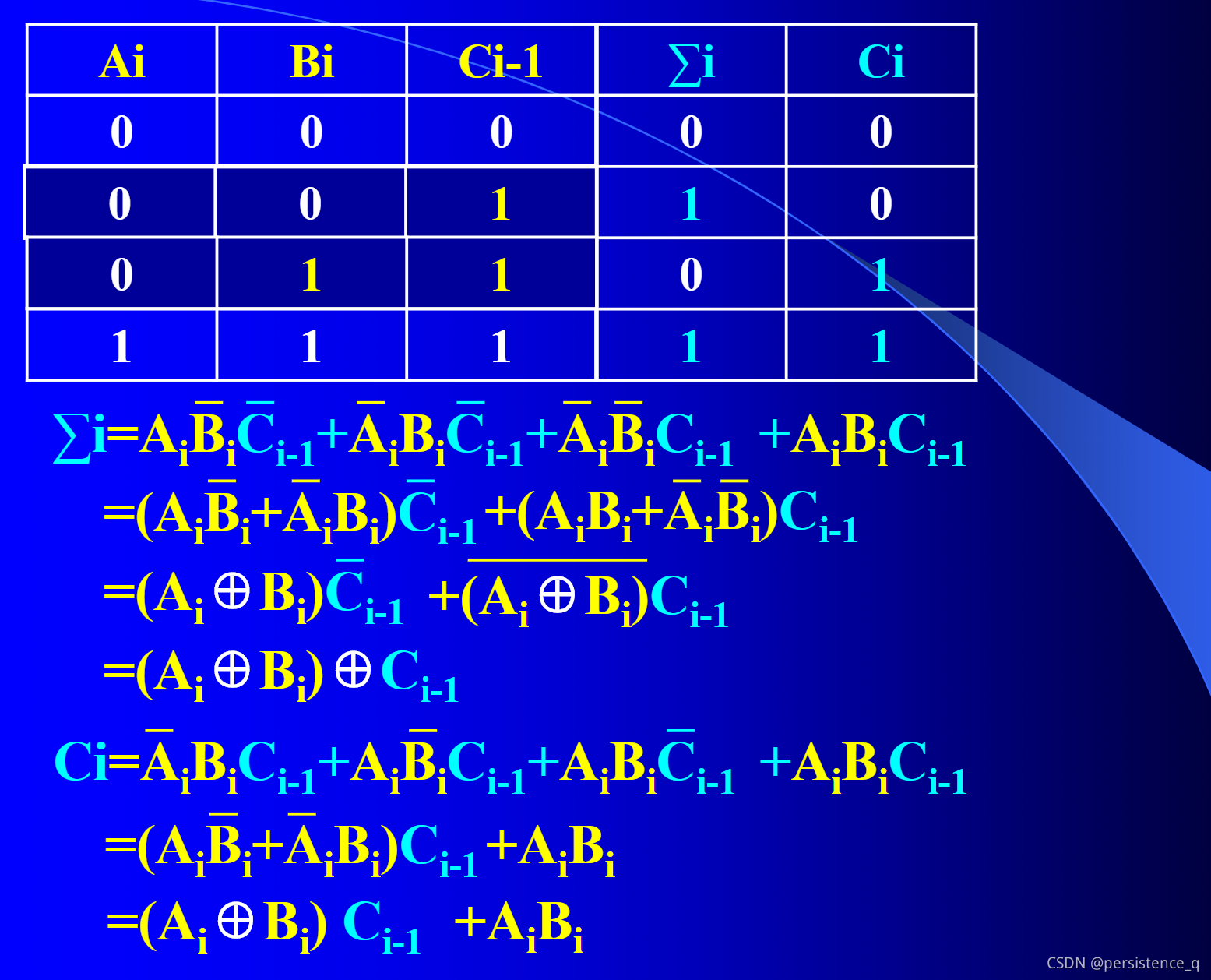

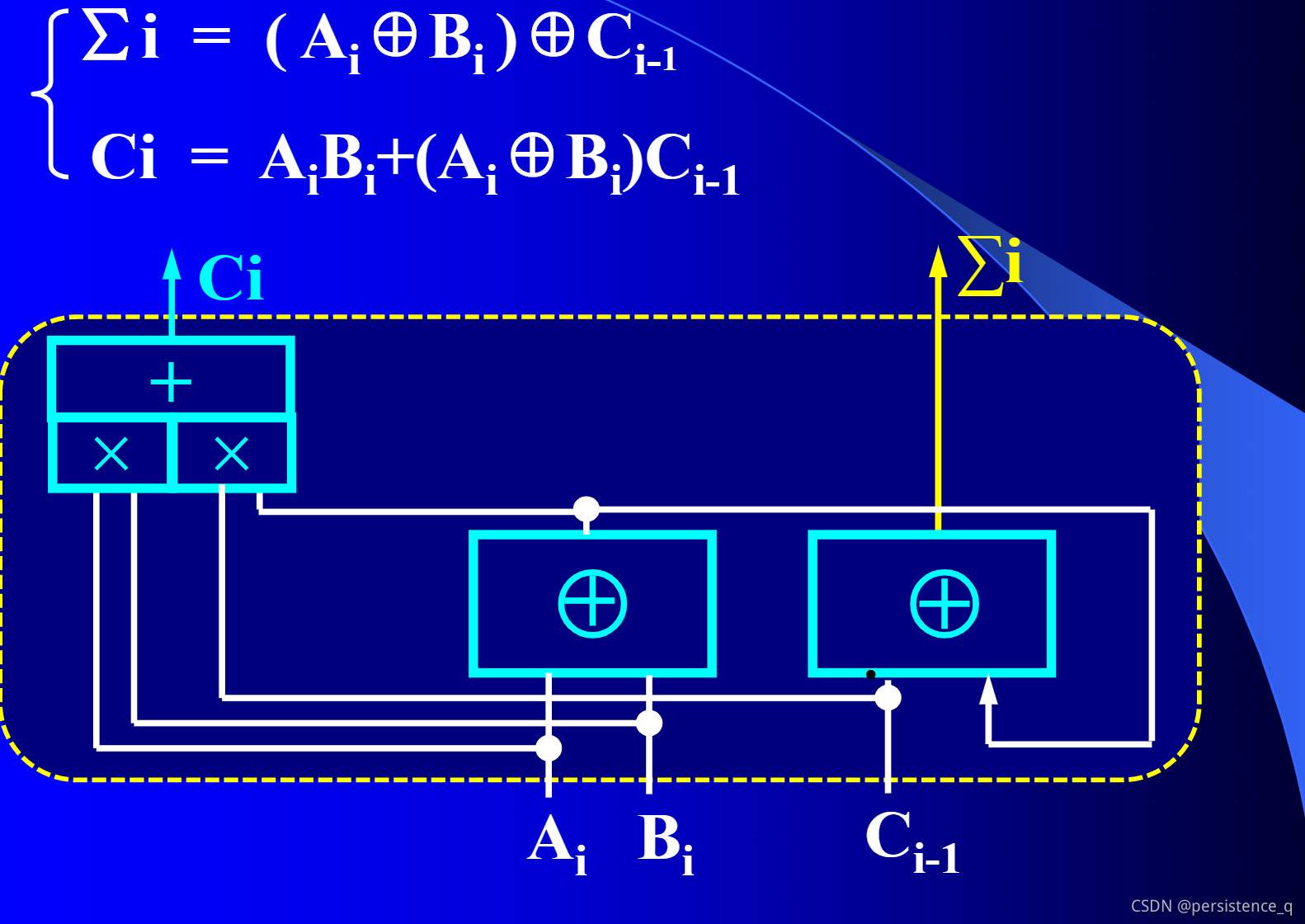

2.全加器

加法器与进位链逻辑

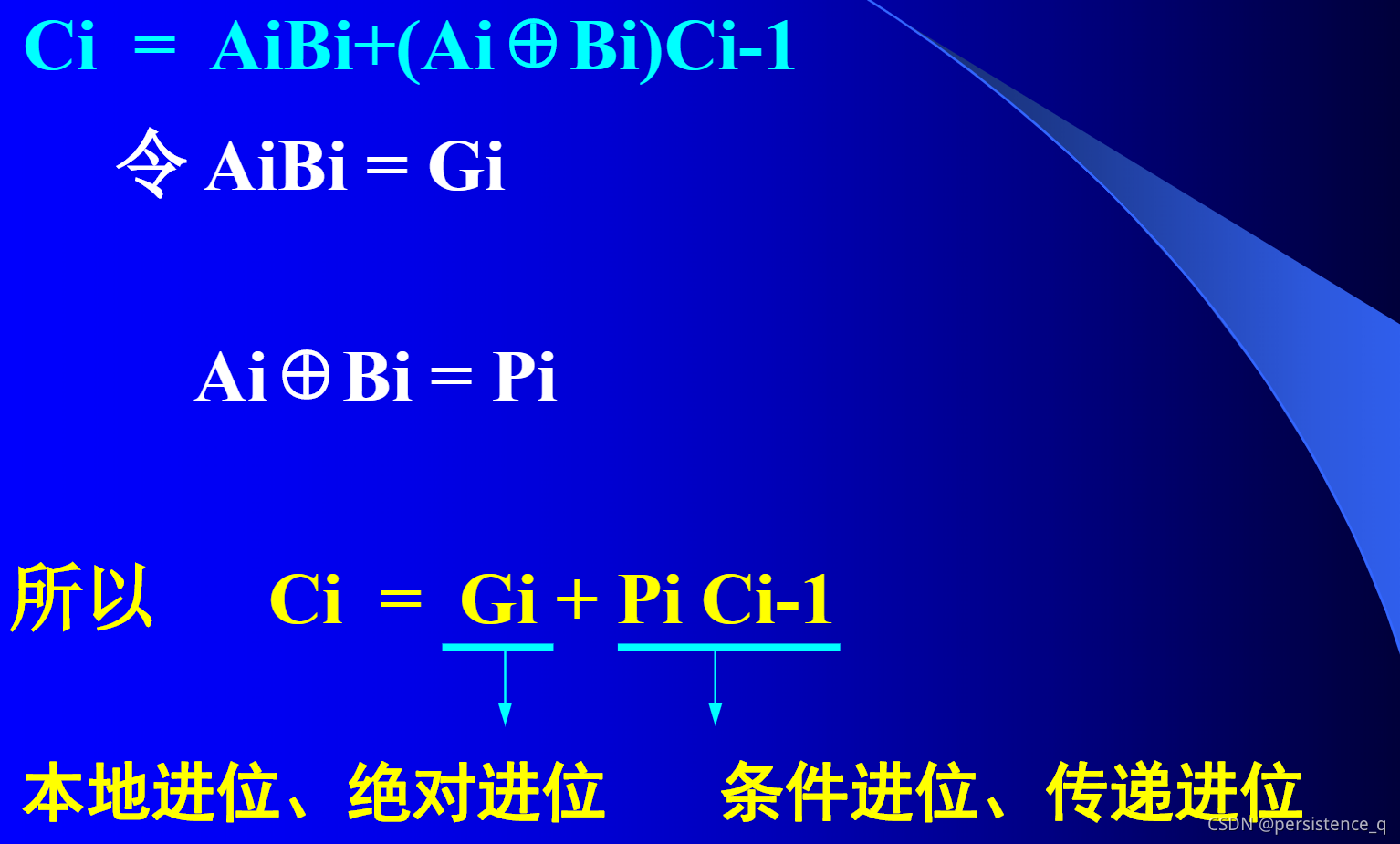

进位的基本逻辑

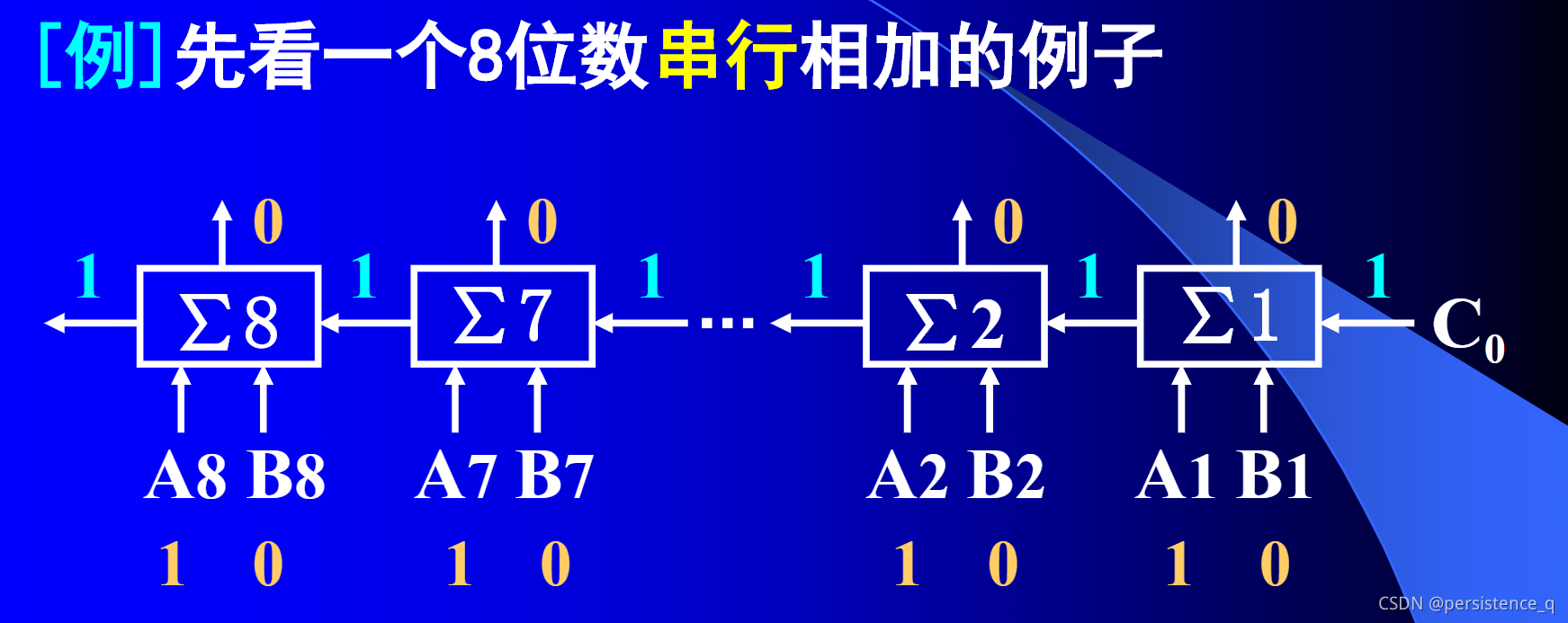

(1)串行加法器

特点:低位向高位依次传递进位信号

影响运算速度的主要因素:进位信号的传递

进位逻辑:进位信号逐位形成

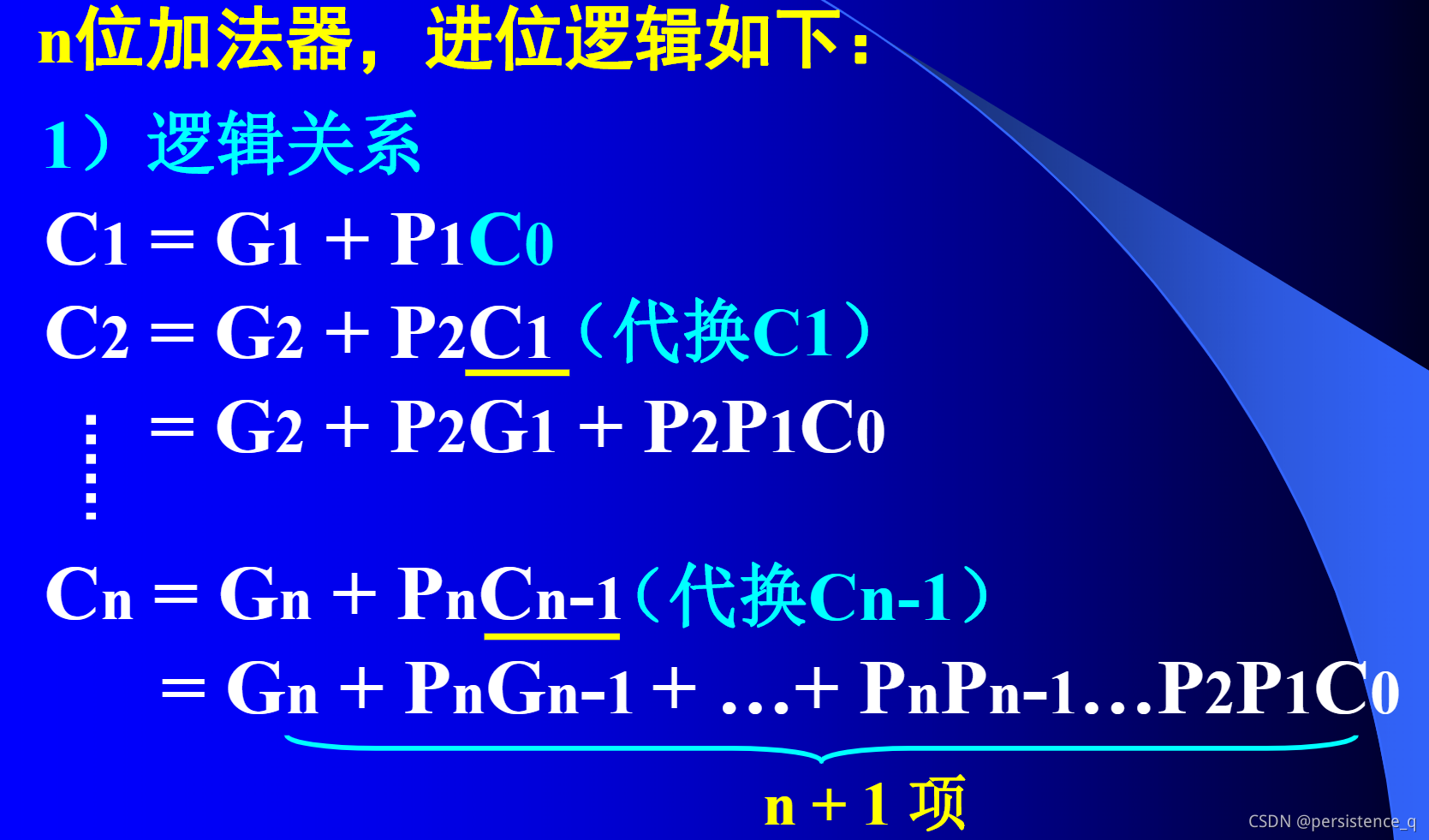

(2) 并行加法器

特点:各位进位信号同时形成

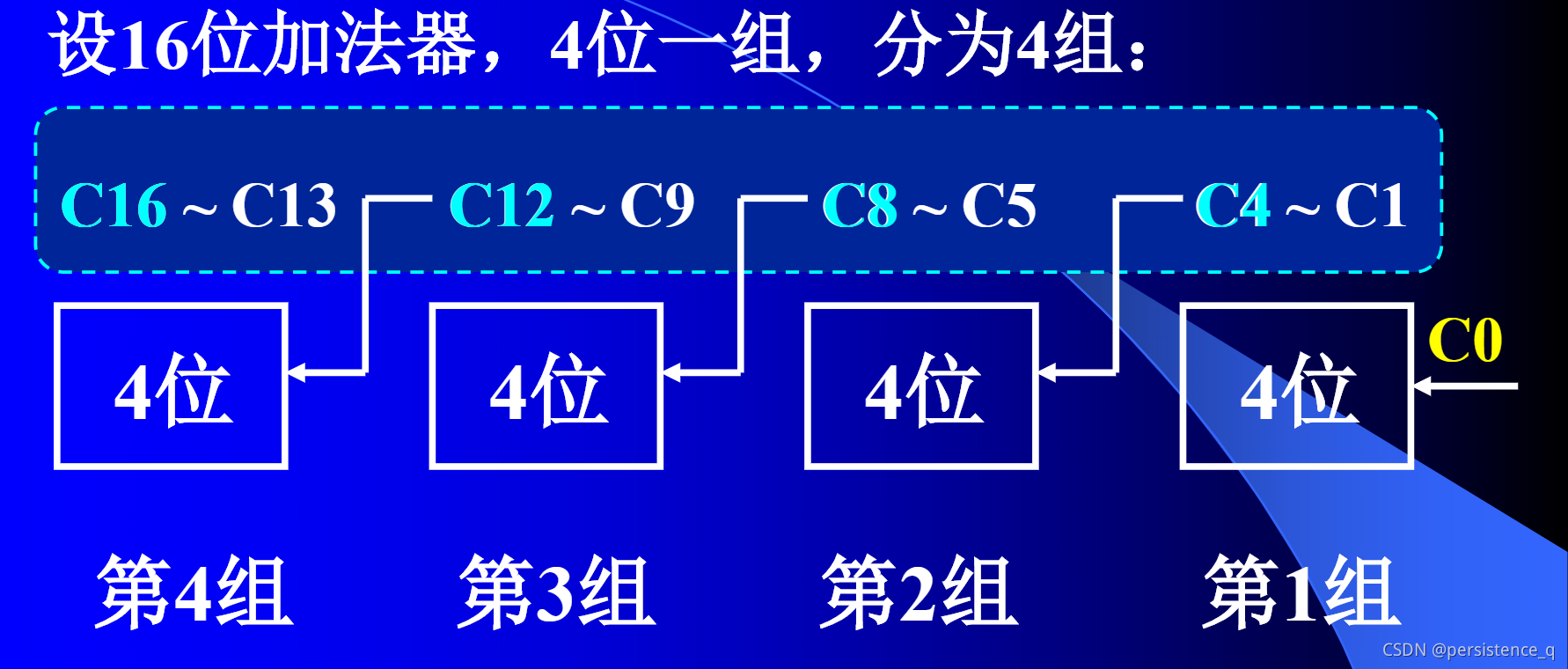

分组:组内并行,组间并行

分级(2级)同时进位:组内并行,组间也并行

速度/结构:介于全串行和全并行之间

运算器组织

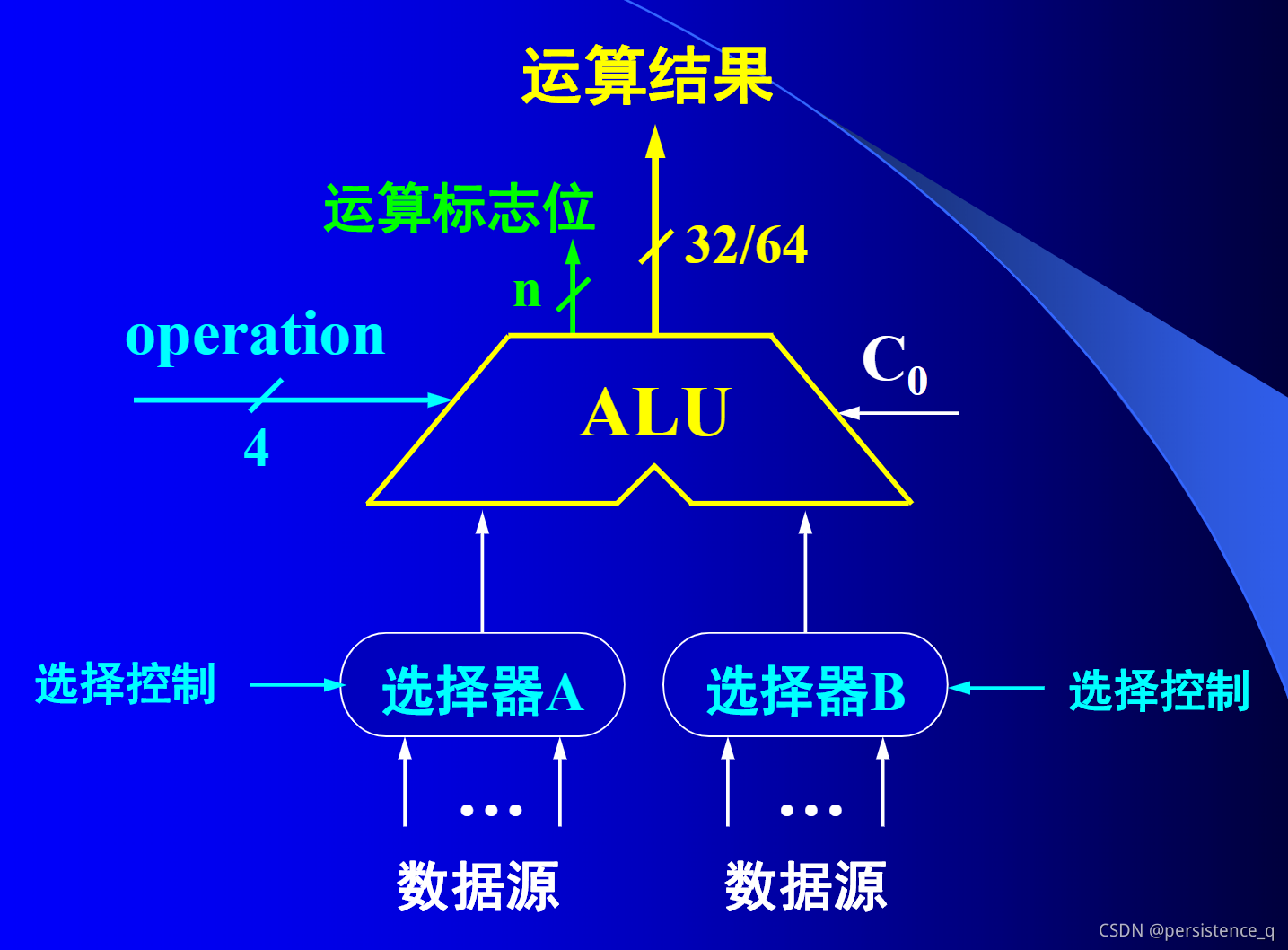

(1)带多路选择器的运算器

特点:r各自独立,可同时向ALU提供两个操作数,采用单向内总线。

(2)带输入锁存器的运算器

特点:单口ram不能同时向ALU提供两个操作数,用锁存器暂存操作数,采用双向内总线

(3)位片式运算器

特点:用双口ram(两地址端,两数据端)作通用寄存器组,可同时提供数据

用多路选择器作输入逻辑,不需暂存操作数,ALU增加乘除功能,用乘商寄存器,存放乘数、乘积或商。

本文详细探讨了如何利用加法器基础实现算术逻辑运算,涉及全加器设计、进位逻辑、串行与并行加法器的区别,以及运算器的不同组织形式,如多路选择器、输入锁存器和位片式运算器。

本文详细探讨了如何利用加法器基础实现算术逻辑运算,涉及全加器设计、进位逻辑、串行与并行加法器的区别,以及运算器的不同组织形式,如多路选择器、输入锁存器和位片式运算器。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?