内核地址https://github.com/Lichee-Pi/linux/tree/nano-4.14-exp

分支 nano-4.14-exp

内核的.config文件 根据官方提供的http://nano.lichee.pro/build_sys/kernel.html

spi flash启动

-

修改设备树

arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts

将原来的&spi0{…}替换为:&spi0 { pinctrl-names = "default"; pinctrl-0 = <&spi0_pins_a>; status = "okay"; spi-max-frequency = <50000000>; flash: w25q128@0 { #address-cells = <1>; #size-cells = <1>; compatible = "winbond,w25q128", "jedec,spi-nor"; reg = <0>; spi-max-frequency = <50000000>; partitions { compatible = "fixed-partitions"; #address-cells = <1>; #size-cells = <1>; partition@0 { label = "u-boot"; reg = <0x000000 0x100000>; read-only; }; partition@100000 { label = "dtb"; reg = <0x100000 0x10000>; read-only; }; partition@110000 { label = "kernel"; reg = <0x110000 0x400000>; read-only; }; partition@510000 { label = "rootfs"; reg = <0x510000 0xAF0000>; }; }; }; };重新编译设备树

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- dtbs -j4 -

配置内核

(1)make ARCH=arm menuconfig

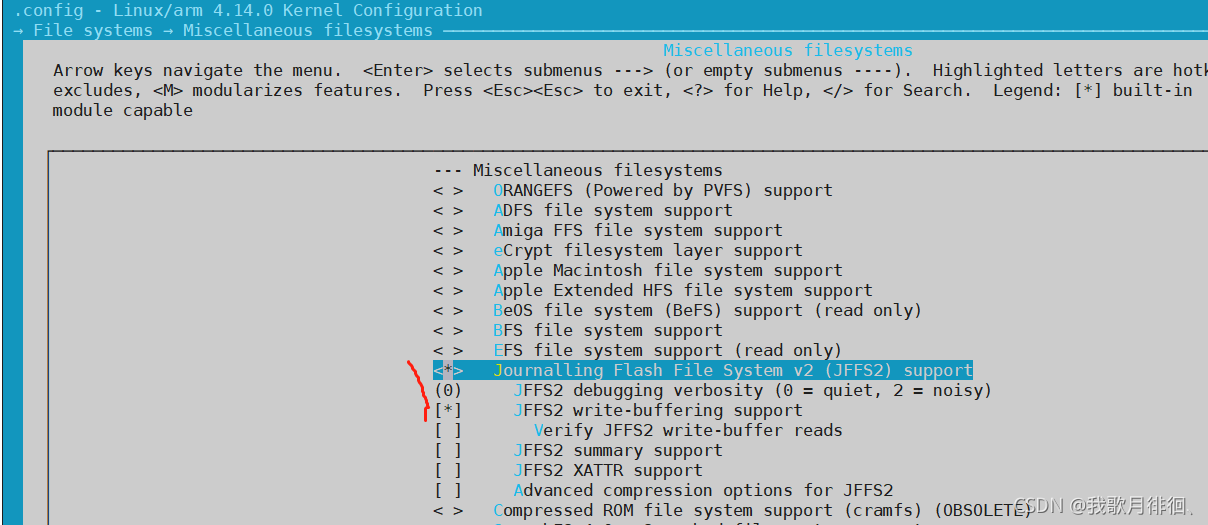

(2) 勾选File systems ‣ Miscellaneous filesystems ‣ Journalling Flash File System v2 (JFFS2) support

(3) 修改源码下的 ./drivers/mtd/spi-nor.c

vi ./drivers/mtd/spi-nor/spi-nor.c

注释掉以下一行:

//{ "w25q128", INFO(0xef4018, 0, 64 * 1024, 256, SECT_4K) },

在这一行下面增加一项:{ "w25q128", INFO(0xef4018, 0, 64 * 1024, 256, 0) },(4) 重新编译内核

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- -j4

问题

Waiting for root device /dev/mtdblock3…

解决:

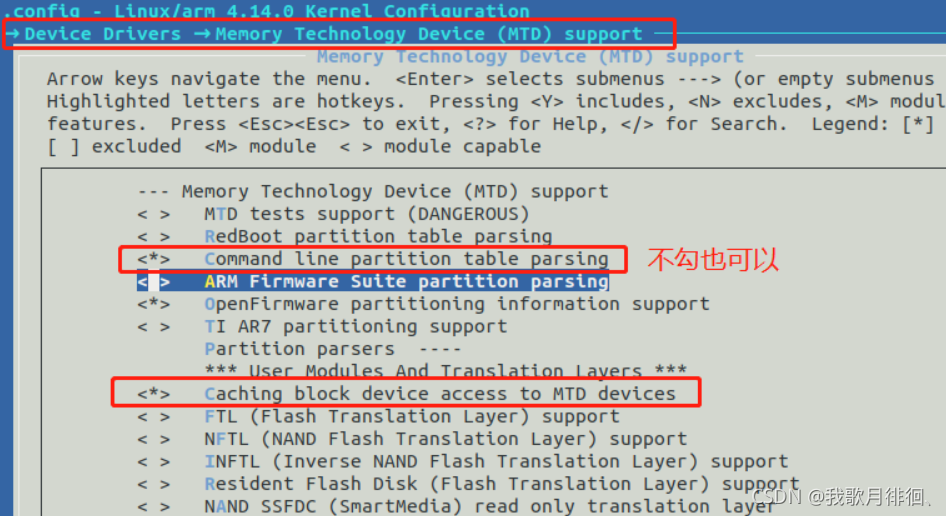

内核配置中增加

caching block device access to MTD devices必须加 我就是卡在这

-CONFIG_MTD_BLKDEVS=y

-CONFIG_MTD_BLOCK=y

VFS: Cannot open root device “mtdblock3” or unknown-block(31,3): error -19

这个问题是文件系统格式导致的,在内核配置中增加 jffs2 的支持

这个是我最后一个坑 启动成功了。

设备树使能

dtb-$(CONFIG_MACH_SUNIV) += \

suniv-f1c100s-licheepi-nano.dtb

本文介绍如何通过SPI Flash启动Lichee Pi Nano开发板,包括修改设备树、配置内核及解决启动过程中遇到的问题。具体步骤涉及内核.config文件设置、设备树suniv-f1c100s-licheepi-nano.dts的修改、内核配置选项调整等。

本文介绍如何通过SPI Flash启动Lichee Pi Nano开发板,包括修改设备树、配置内核及解决启动过程中遇到的问题。具体步骤涉及内核.config文件设置、设备树suniv-f1c100s-licheepi-nano.dts的修改、内核配置选项调整等。

4823

4823

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?