目录

1. 简介

以STM32为例,我们知道对于STM32来说,每个GPI/O端口有两个32位配置寄存器(GPIOx_CRL, GPIOx_CRH),两个32位数据寄存器(GPIOx_IDR和GPIOx_ODR),一个32位置位/复位寄存器(GPIOx_BSRR),一个16位复位寄存器(GPIOx_BRR)和一个32位锁定寄存器(GPIOx_LCKR)。

根据数据手册中列出的每个1/0端口的特定硬件特征,GPIO端口的每个位可以由软件分别配置成多种模式:

- 输入:浮空输入、上拉输入、下拉输入、模拟输入。

- 输出:开漏输出、推挽输出、复用开漏输出、复用推完输出。

其中对于输入,根据其名字都比较好理解,但是对于输出,什么是开漏?什么又是推挽呢?明明也是高低电平,为什么这样命名呢?

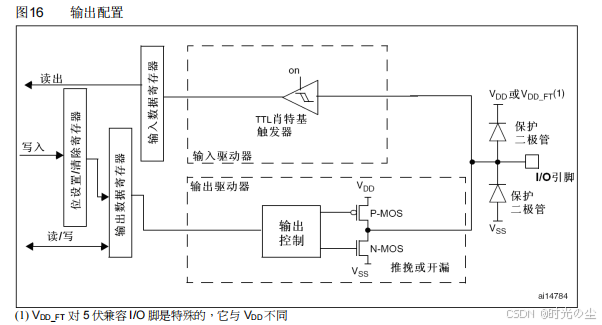

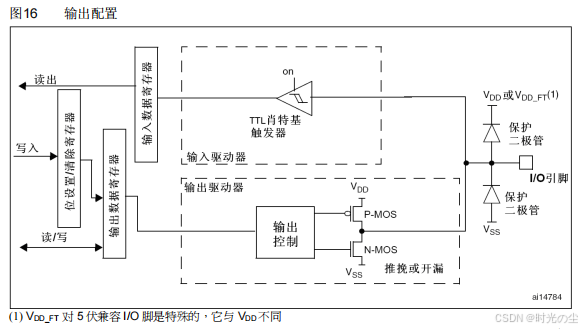

看一下其数据手册,其输出物理层配置如下:

首先先看一下其介绍,当I/O端口被配置为输出时:

● 输出缓冲器被激活

─ 开漏模式:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将端口置于高阻状态(PMOS从不被激活)。

─ 推挽模式:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将激活P-MOS。

● 施密特触发输入被激活

● 弱上拉和下拉电阻被禁止

● 出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器

● 在开漏模式时,对输入数据寄存器的读访问可得到I/O状态

● 在推挽式模式时,对输出数据寄存器的读访问得到最后一次写的值。

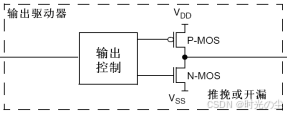

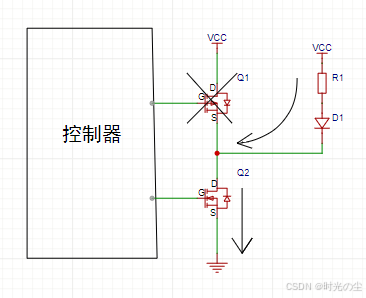

根据介绍,我们将这一块单独拿出来,进行讲解:

根据介绍,对于推挽和开漏的区分,主要在这两个MOS管上进行的一些区分,我们将这两个MOS管可能存在的状态列举一下:

| P-MOS | N-MOS | 输出 | |

| 状态1 | 打开 | 关闭 | 高电平 |

| 状态2 | 关闭 | 打开 | 低电平 |

| 状态3 | 关闭 | 关闭 | 浮空/高阻态 |

| 状态4 | 打开 | 打开 | 不存在 |

对于第四种状态,为什么不存在呢?我们可以看一下,如果两个MOS管都处于导通状态,那么VDD和VSS也会导通,导致正负极短接烧毁电路,因此不存在两个MOS管都打开的状态:

2. 推挽输出

这里我们将前两种状态拿过来:

| P-MOS | N-MOS | 输出 | |

| 状态1 | 打开 | 关闭 | 高电平 |

| 状态2 | 关闭 | 打开 | 低电平 |

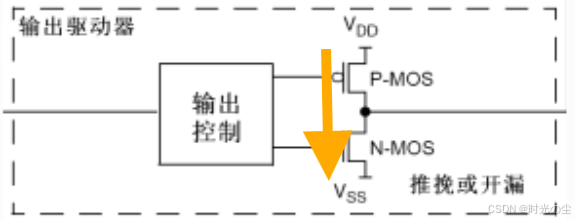

首先状态1,P-MOS管打开,N-MOS管关闭,此时电流的方向是从MCU往外输出,这个电流称为拉电流,我们想象是将电流“推”出去:

接着状态2,P-MOS管关闭,N-MOS管打开,此时电流的方向是从外往MCU输入,这个电流成为灌电流,我们可以将其理解为“挽”回来:

这样就实现了电平的“推”“挽”输出,通过开关两个MOS管的状态实现高低电平。

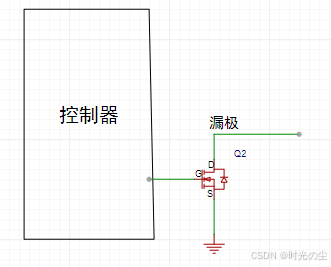

3. 开漏输出

接着我们在将状态2和3拿出来:

| P-MOS | N-MOS | 输出 | |

| 状态2 | 关闭 | 打开 | 低电平 |

| 状态3 | 关闭 | 关闭 | 浮空/高阻态 |

根据上面两种状态我们可以看出,P-MOS管一直处于关闭状态,相当于没有,也就是说下面的MOS管的漏极相当于啥也没接,处于一个开路状态,因此这个模式称之为“开漏”输出:

开漏输出最重要的作用是:电平匹配,在设计电路时不论是单片机还是外设芯片或是负载,每个个体的逻辑电平可能是不一样的,这种情况时就需要作电平的匹配,就用到了开漏输出模式。

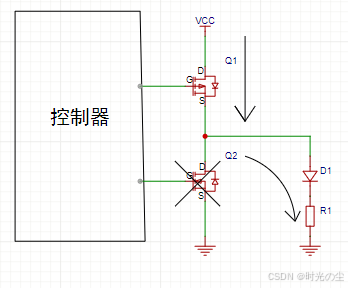

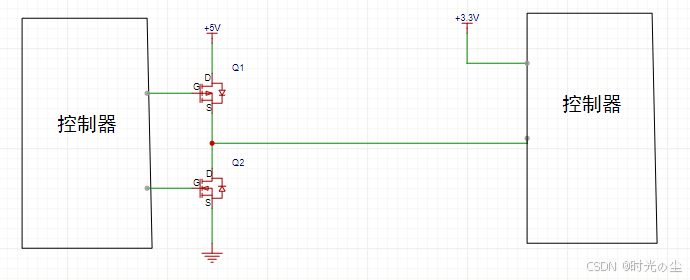

举个例子,假如我们有一个5V的芯片,此时想要去控制另一个3.3V的芯片,如果使用推挽输出,是不是5V的电平有可能将3.3V的引脚烧毁:

而如果我们使用开漏输出,对于开漏输出模式,因为场效应管的漏极直接引出,是需要加一个外置电源的,我们可以通过外接电源的方式得到想要的电平:

这样就可以实现5V单片机对于3.3V芯片的控制。

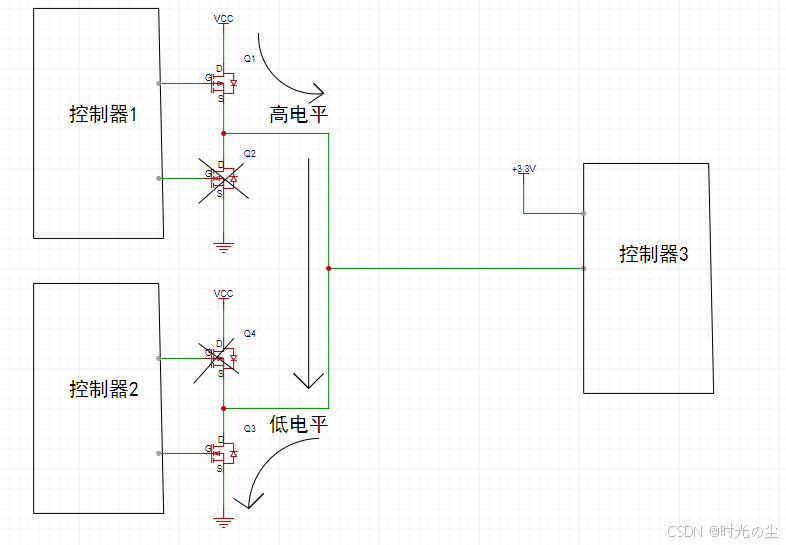

同时我们在思考一个问题,假如我们想要两个单片机控制同一个控制器的引脚,如果我们使用推完输出,可能会导致这样的情况:

如果控制器1想要控制高电平,但是控制器2想要控制低电平,这就会导致两个控制器的正负极直接短接,可能会烧毁电路。

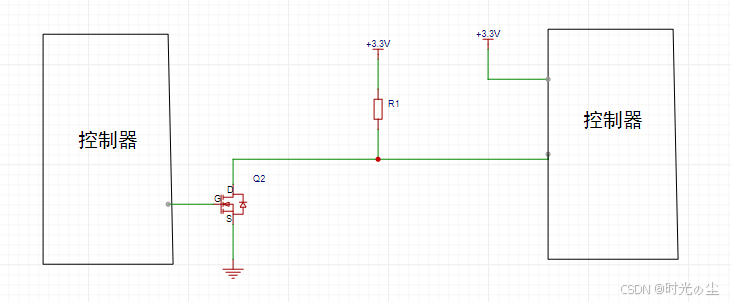

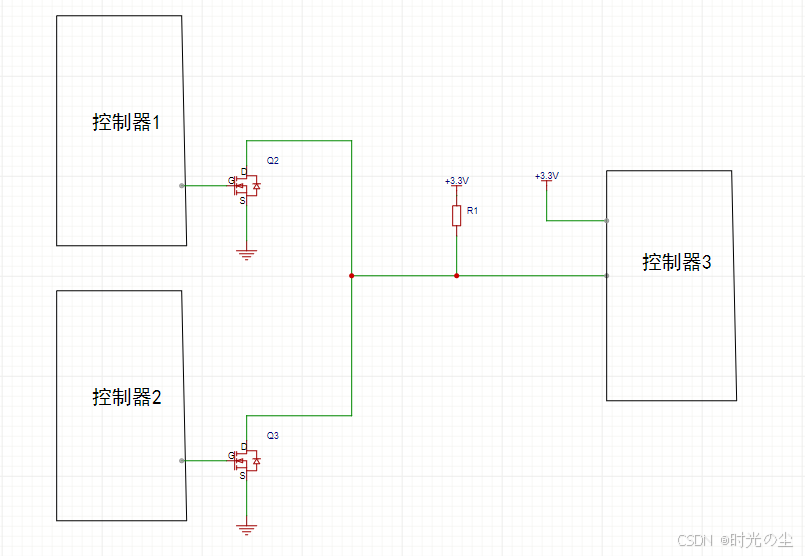

而如果我们使用开漏输出,电路如下:

此时Q2和Q3的几种状态如下:

| Q2 | Q3 | 输出 |

| 打开 | 关闭 | 低电平 |

| 关闭 | 打开 | |

| 打开 | 打开 | |

| 关闭 | 关闭 | 高电平 |

也就是线与的特性,只有全为关闭的状态下,也就是MOS管都截止时,此时的引脚就相当于连接了一个无穷大的电阻,所有IO引脚对外呈现的是高阻态,当MCU供电为5V,开漏输出引脚上接外部3.3V电源时,因为N-MOS的阻值无穷大,所以此时IO引脚上的电压就接近与3.3V电压。

根据这一特性我们就可以实现IIC的主从机控制。

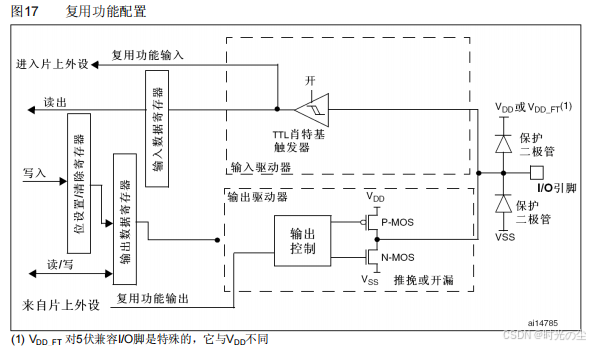

4. 复用推挽/开漏输出

对于复用的介绍:

● 在开漏或推挽式配置中,输出缓冲器被打开

● 内置外设的信号驱动输出缓冲器(复用功能输出)

● 施密特触发输入被激活

● 弱上拉和下拉电阻被禁止

● 在每个APB2时钟周期,出现在I/O脚上的数据被采样到输入数据寄存器

● 开漏模式时,读输入数据寄存器时可得到I/O口状态

● 在推挽模式时,读输出数据寄存器时可得到最后一次写的值

我们可以对比一下普通和复用的两张图:

可以发现二者的功能实现大体上是相同的,只是

- 普通GPIO模式:输出信号来自CPU的输出数据寄存器(由你写代码 GPIOx->ODR = 1 来控制)。

- 复用功能模式:输出信号直接来自片上的外设(例如,当UART要发送一个bit时,它会自动控制这个引脚的电平)。

2028

2028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?