9 离散分配存储方案

9.1基本分页存储管理方式

9.1.1 分页存储管理基本思想

程序地址空间

- 把用户程序按系统规定的逻辑页划分成大小相等的部分,称为页(page)

- 从0开始编页号,页内地址是相对于0编址

- 用户程序的划分是由系统自动完成的,对用户是透明的

- 一般一页的大小为2的整数次幂

逻辑地址

- 地址的高位部分为页号

- 地址的低位部分为页内地址

内存地址空间

- 按系统规定的逻辑页大小划分为大小相等的区域,称为块或内存块(物理页面、页框)

- 从0开始编块号

内存分配

- 物理块表:整个系统有一个物理块表,描述物理内存空间的分配使用状况

- 数据结构:位示图、空闲块链表

- 内存以块为单位进行分配,并按应用程序的页数多少来分配。

- 逻辑上相邻的页,物理上不一定相邻。

9.1.2 页地址映射

页表

- 若将应用程序的包含页号和页内地址的逻辑地址转换成内存地址,必须要有一个数据结构,用来登记页号和块号的对应关系和有关信息。

- 这样的数据结构称为页表。

- 系统为每个进程在内存建立一个页表

- 页表内容

- 页号:登记程序地址空间的页号

- 块号:登记相应的页所对应的内存块号

- 其它:登记与存储信息保护有关的信息

- 页表的首地址和长度存于该进程的PCB中;

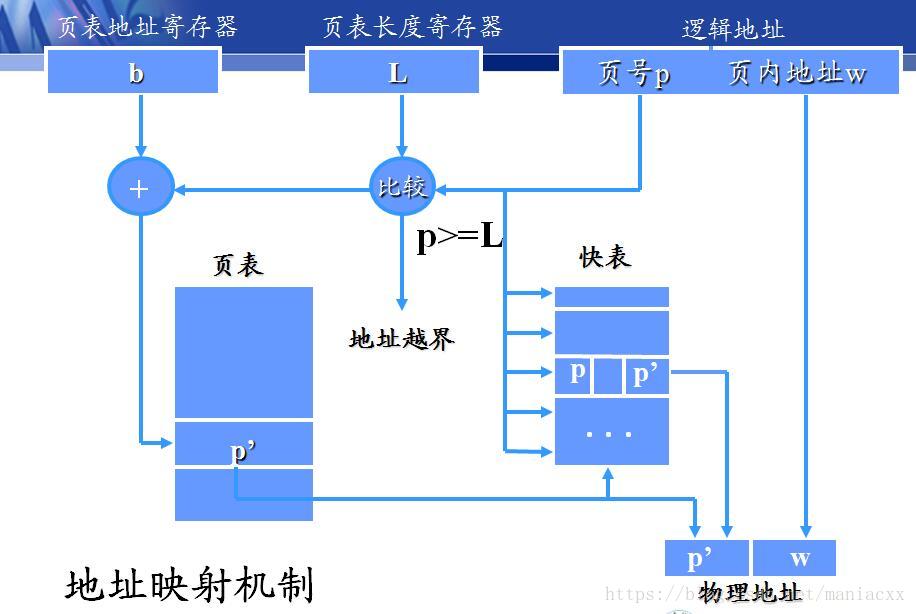

- 占用处理机的当前进程的页表首地址和长度需要放在地址映射机构的页表首址寄存器和页表长度寄存器。

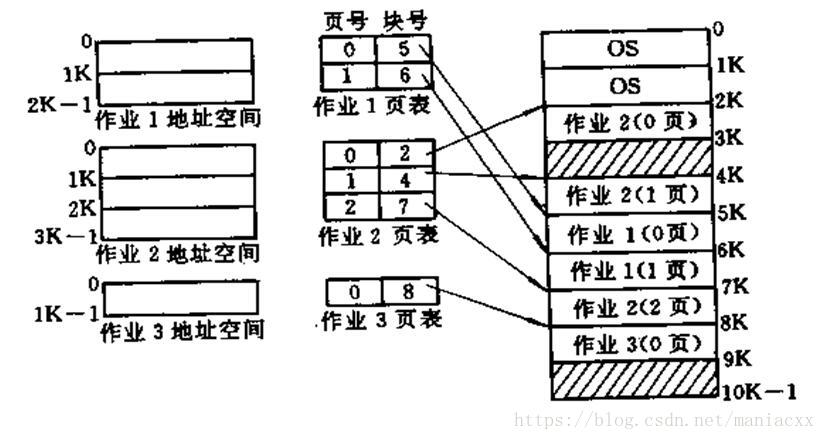

例:作业1有2页分别装入内存的5、6号块

作业2有3页装入内存的2、4、7号块

作业3有1 页装入内存的8号块

页大小的选择

太大:浪费;太小:页表过长。页的大小是2K ,K: 9~16。

各种系统的页表大小:

- IBM AS/400 VAX NS32032:512字节

- Intel 80386 Motorola 68030: 4096字节

- Windows2000: 4096字节

- Windows NT 随CPU的不同而不同:4~64K

页地址映射

- 分页中的地址映射其实与通常的地址映射的概念是一样的,即把程序地址转换成内存地址,这个转换过程是在程序执行过程中完成的,是动态地址映射。

- 在现代计算机系统中,由系统提供的地址映射硬件来完成地址映射工作。

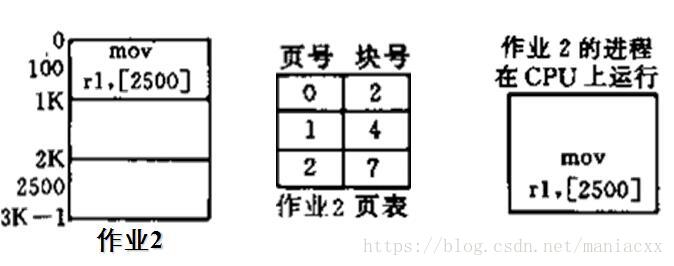

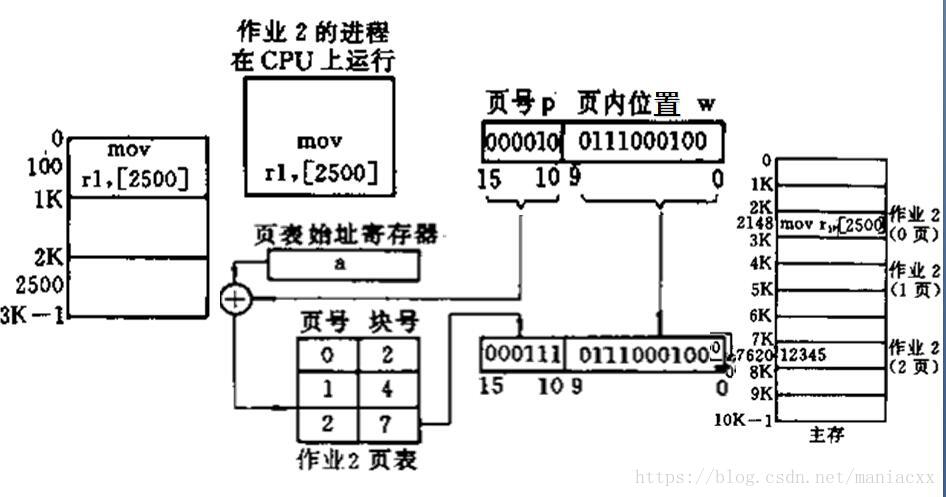

例:设页长为1K,程序地址字长为16位。

在执行指令MOV r1,[2500]时,地址转换步骤:

1.取出程序地址字2500送虚地址寄存器VR;

2.由MMU硬件分离出页号P和页内地址W;

- 因为页长为1K,所以页内地址占10位(0-9位),页号占6位(10-15位);

- 硬件取出VR寄存器中的高6位即为页号,低10 位即为页内地址。

3.计算可得P=000010(2),W=0111000100;

4.根据页号P=2,硬件自动查该进程的页表,找到2号页对应的块号为7(000111),将块号送到内存地址寄存器MR的高6位中。

5.将VR中的W的值0111000100复制到MR的低10位中,从而形成内存地址。

6.系统就以MR中的地址访问内存。

计算时要注意:

- 若给出的地址为16进制,则将其转换为二进制,然后,根据页长及程序地址字的长度,分别取出程序地址的高几位和低几位得到页号及页内地址。

如页长为2K,程序地址字为16位,21A4,则高5位为页号,低11位为页内地址,页号为00100,页内地址为00110100100 若给出的地址为十进制,则用公式: 程序地址/页长,商为页号,余数为页内地址。内存地址=块号*页长+页内地址

如程序地址为8457, 页长为4KB

则8457/4096可得:商为2,余数为265。

即P=2,W=265

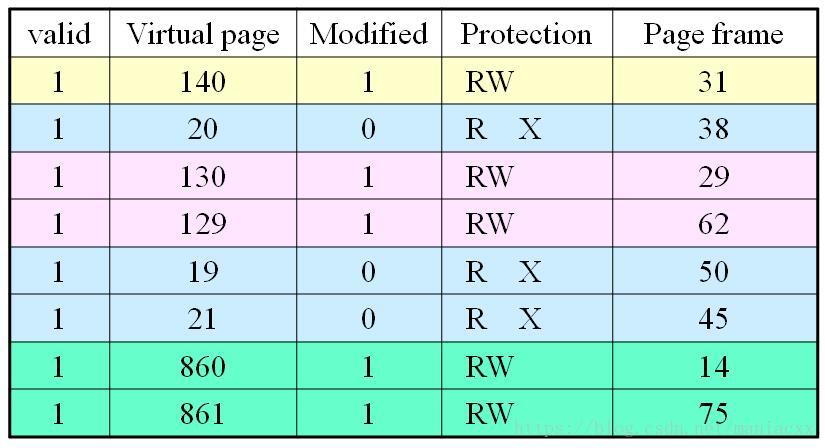

分页存储管理中的信息保护

信息保护从两个方面实现:

- 在分离程序地址的页号和页内地址时判别访问地址是否越界

若产生的页号满足下式为合法:

- 0 ≤页号<程序地址空间的页数

- 判断由硬件自动做,若不合法,硬件产生越界中断,由操作系统的越界中断处理程序进行处理。

- 判断访问是否越权

- 在页表中增加用于存取控制和存储保护的信息,当要访问某页的某个逻辑地址时系统要根据该页的存取控制和存储保护信息检查访问是否合法。

快表/联想存储器

在前述的页地址变换过程中有一个严重的问题—— 每一次对内存的访问都要访问页表,页表是放在内存中的,也就是说每一次访问内存的指令至少要访问两次内存,运行速度要下降一半。

解决方法:

- 把页表放在一组快速存储器中(Cache),从而加快访问内存的速度。

- 把这种快速存储器组成的页表称为快表,把存放在内存中的页表称为慢表。

- 快表又叫相联(联想)存储器(associative memory)或TLB (Translation lookaside buffers)

一个程序可能会很大,如1M,若页长为1K,则该程序有1000个页,则页表就需要1000个表项,当程序更大时,页表会更大,那么应该有一个多大的快速存储器才能满足要求呢?

遇到两个问题:

可能快速存储器多大都是不够的,因为程序可能会更大,并且快速存储器是非常昂贵的。

解决方法:

- 实际上并不需要一个很大的快速存储器,有一个能存放16个页表表目的快速存储器就够了。

- 硬件根据需要将页表中当前需要的少量表目读入快表,其它表目仍留在内存的页表中,当需要时读入新的表目,并淘汰适当的表目。

- 快表表项:

页号;内存块号;保护位;修改位;有效位

结合快表的查询分析:

- 当调度合理时,可以达到97%的效率。

- 访问页表的速度大致相当于访问快表的速度,考虑到快表的速度是内存速度的数倍或数十倍,那么相对于真正的访问内存工作来讲,访问快表的时间可以忽略不计。

- 即具有快表的页地址变换不会造成进程运行速度的下降。

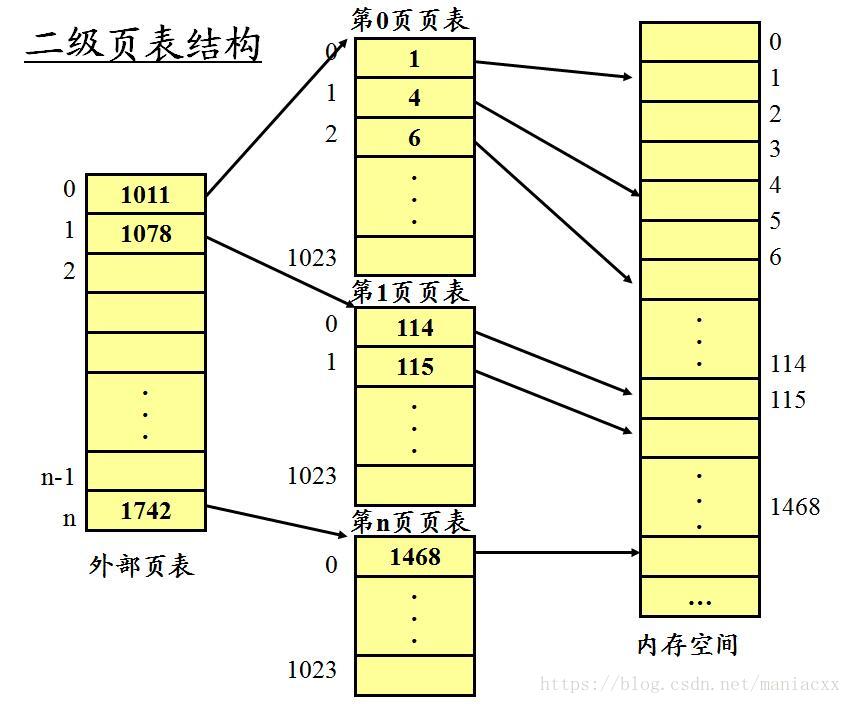

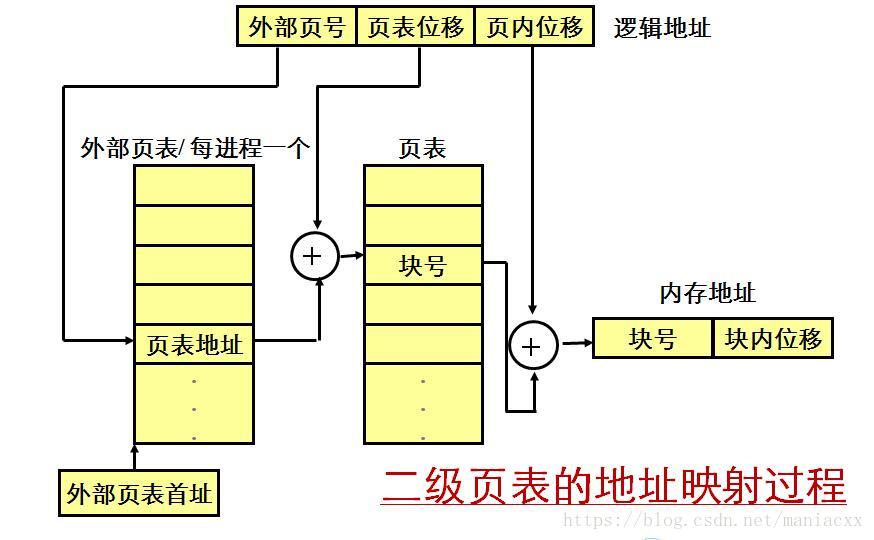

两级页表和多级页表

- 页表需要连续空间存储的,但是当页表项很多时,仅采用一级页表需要大片连续空间。

- 可将页表也分页,并对页表所占的空间进行索引形成外层页表。由此构成二级页表。

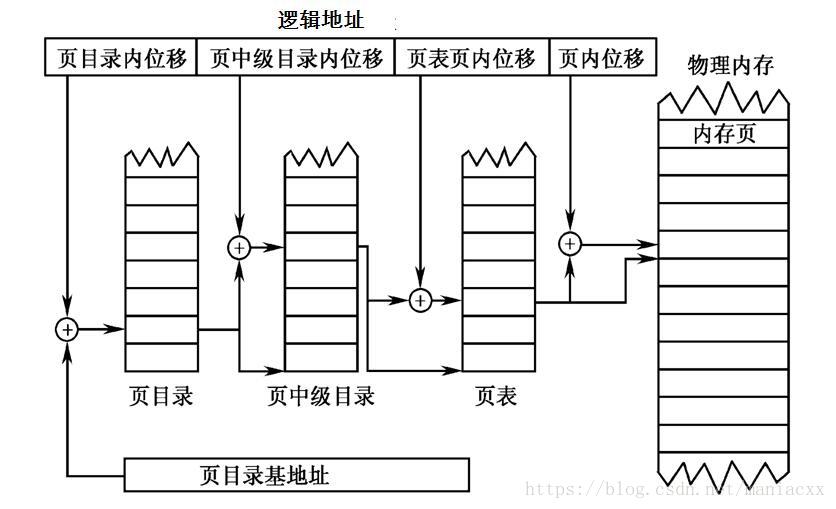

- 更进一步可形成多级页表。

三级页表结构及其地址映射过程:

9.1.3 基本页式存储管理方案小结

优点:解决了碎片问题

便于管理缺点:不易实现共享

不便于动态链接

9.2 基本分段存储管理方式

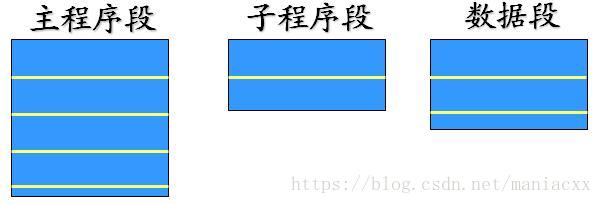

9.2.1 分段存储管理基本思想

程序地址空间

- 按程序自身逻辑关系划分为若干个段,每个段都有一个段名和段号;

- 段号从0开始;

- 每段段内从0开始编址,段内地址连续。

逻辑地址

内存地址空间

- 内存空间被动态的划分为若干个长度不相同的区域,称为物理段;

- 每个物理段由起始地址和长度确定。

内存分配

- 以段为单位分配内存,每一个段在内存中占据连续空间;

- 各段之间可以不连续存放。

- 空闲块管理

空闲块表(队列) - 内存分配算法(三种)

首次 最佳 最坏

与动态分区管理相同

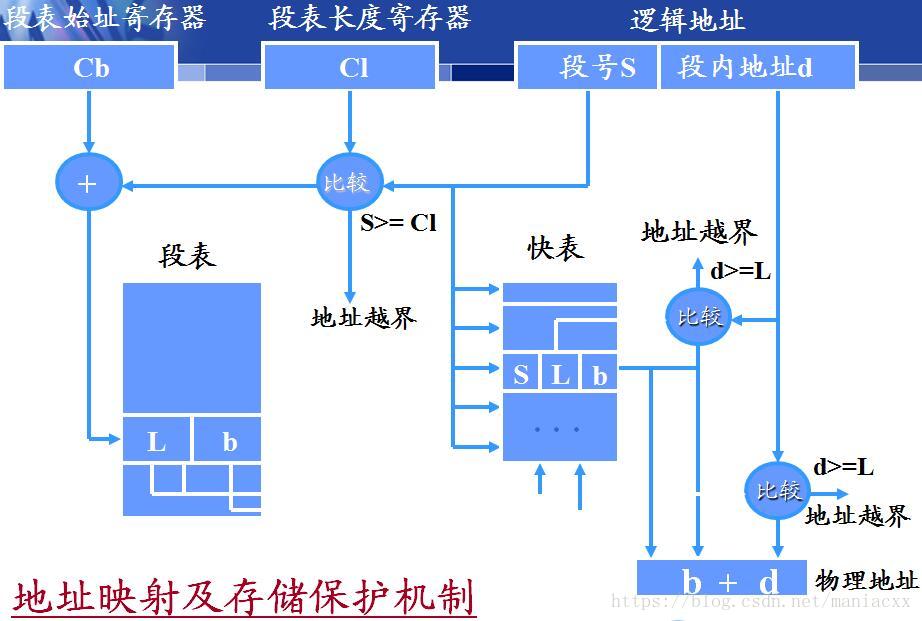

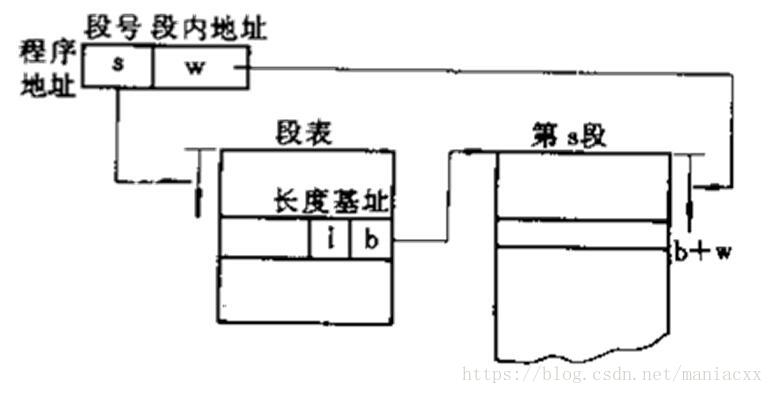

9.2.2 段地址映射

1、 地址映射数据结构

- 每一进程有个段表,它的每一个段在段表中占用一个表目;

- 段表一般包括有段的首址、段的长度和存取状态等信息。

- 段表首址指针和段表的长度存放在进程PCB中,当前进程的还需装入寄存器。

2.段地址映射

由硬件地址变换机构完成。

段地址映射过程为:

- 程序地址送入虚地址寄存器VR中;

- 取出段号S和段内位移W;

- 根据段表首址指针找到段表,查找段号为S的表目,得到该段的首地址;

- 把段首地址与段内位移相加,形成内存地址送入MR中,并以此地址访问内存。

3、存储保护

- 防止越界访问

- 段号

- 段内地址

- 防止越权访问

4、快表

- 同页地址变换一样,在段地址变换过程中,也有两次访问内存的问题。为了加快访问内存的速度也可采用快速存储器组成快表。

5、分段与分页技术的比较

分段与分页主要有以下差别:

- 页大小是系统固定的,段大小通常不固定。

- 分页是出于系统管理的需要,分段是出于用户应用的需要。

- 一条指令或一个操作数可能会跨越两个页的分界处,而不会跨越两个段的分界处。

- 逻辑地址表示

- 分页是一维的,各个模块在链接时必须组织成同一个地址空间;

- 分段是二维的,各个模块在链接时可以每个段组织成一个地址空间。

- 通常段比页大,因而段表比页表短,可以缩短查找时间,提高访问速度。

- 段的共享比页的共享更容易

9.2.3 段式存储管理方案小结

优点:

- 便于动态申请内存

- 管理和使用统一化

- 便于共享

- 便于动态链接

缺点:产生碎片

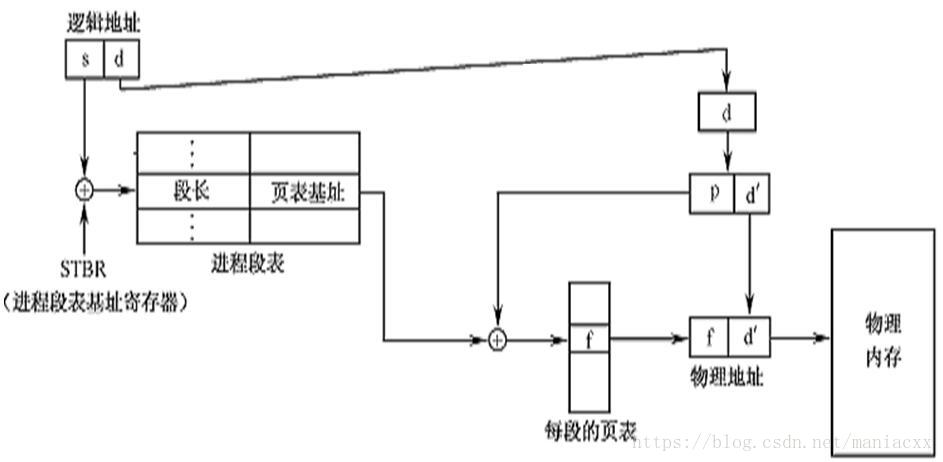

9.3 段页式存储管理方式

结合页式段式优点,克服二者的缺点

9.3.1 段页式存储管理基本思想

- 程序地址空间

按段式划分(对用户来讲,按段的逻辑关系进行划分;对系统讲,按页划分每一段)

逻辑地址

内存地址空间

按页式存储管理方案- 内存分配

以块为单位进行分配。

9.3.2 地址映射

段表:记录了每一段的页表始址和页表长度

页表:记录了该段中每个逻辑页号与内存块号的对应关系

(每一段有一个,一个程序可能有多个页表)

本文深入探讨了计算机系统中的存储管理技术,包括分页、分段和段页式存储管理方式的基本原理、地址映射机制、信息保护措施以及各自的优缺点。通过详细分析,帮助读者理解这些技术是如何解决内存分配与管理中的关键问题。

本文深入探讨了计算机系统中的存储管理技术,包括分页、分段和段页式存储管理方式的基本原理、地址映射机制、信息保护措施以及各自的优缺点。通过详细分析,帮助读者理解这些技术是如何解决内存分配与管理中的关键问题。

2814

2814

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?