在 Apple 的2022春季发布会中,苹果推出了全新的 Apple 硅芯片 M1 Ultra,M1 Ultra 是 M1 系列的最后一款芯片,也是迄今为止最强大的芯片。

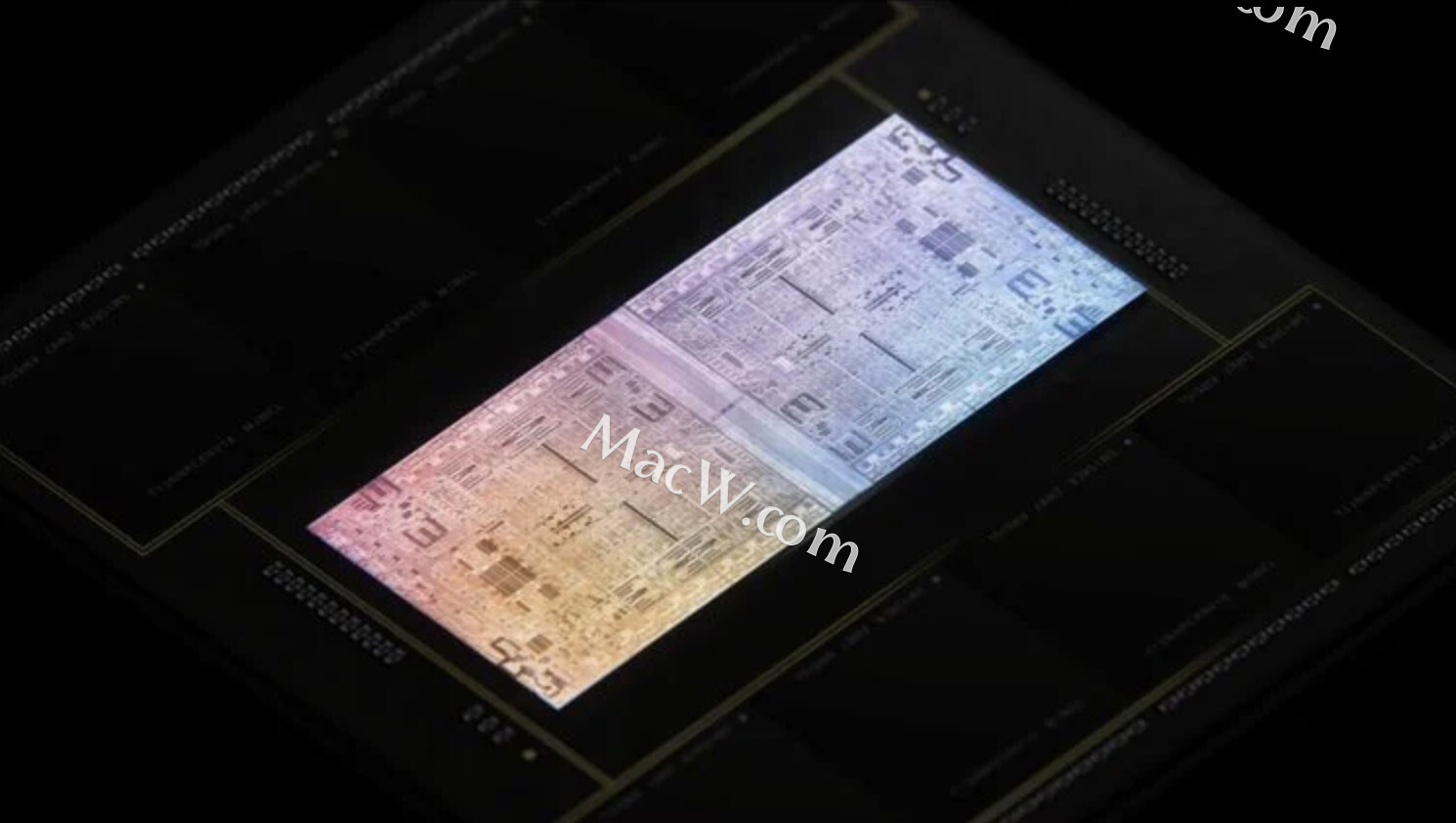

M1 Ultra 是 Apple 在 M1 系列中最新(也是最后一个)Apple 硅片上系统 (SoC),由于它是 SoC,计算机的所有部分都在同一个芯片上,而不是单独的 CPU、GPU 等。该处理器实际上是由去年发布的两个 M1 Max 芯片制成的。

这两个芯片使用 Apple 的处理器组合技术 UltraFusion 连接。UltraFusion 使用硅中介层连接芯片,而不是通过主板进行典型连接。M1 Ultra 的芯片已连接超过 10,000 个信号,可提供 2.5TB/s 的低延迟、处理器间带宽。

M1 Ultra 配备功能异常强大的 20 核 CPU,具有 16 个高性能内核和 4 个高效内核。搭配该芯片,内存带宽为800GB/s,M1 Ultra可配置128GB统一内存。

M1 Ultra 内部的 32 核神经引擎每秒运行高达 22 万亿次运算,专门用于机器学习任务。从历史上看,Apple 将其用于板载视频和音频处理以及其他日常流程。

M1 Ultra 的媒体引擎功能是 M1 Max 的两倍,还提供令人难以置信的 ProRes 视频编码和解码,M1 Ultra 支持播放多达 18 个 8K 视频流。

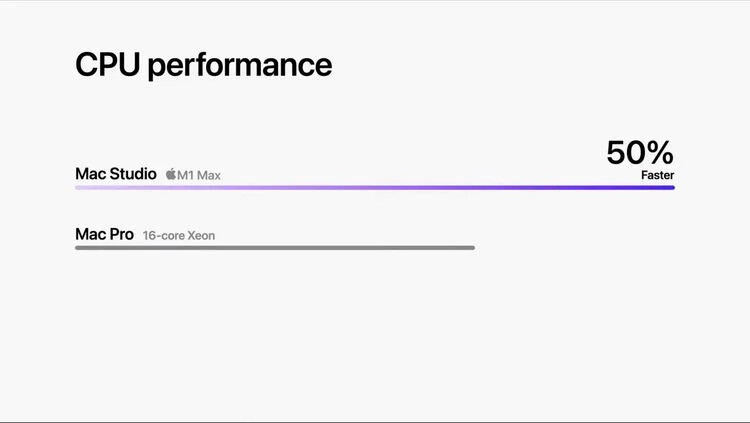

根据 Apple 在主题演讲中的图表,M1 Ultra 在完成任务时比 Mac Pro 快 50%。它的功耗比 16 核台式 PC(配备 Intel Core i9)低 90%,而且速度仍然更快。

新的 M1 Ultra 处理器是 Apple 迄今为止最强大的处理器,它确实拥有一些令人难以置信的数字。M1 Ultra 则是专为最高级别的专业人士而设计。

苹果发布了M1Ultra,由两块M1Max芯片融合而成,提供20核CPU、800GB/s内存和强大的媒体引擎,比MacPro快50%,能耗低且性能卓越,定位顶级专业人士

苹果发布了M1Ultra,由两块M1Max芯片融合而成,提供20核CPU、800GB/s内存和强大的媒体引擎,比MacPro快50%,能耗低且性能卓越,定位顶级专业人士

1255

1255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?