课题的研究内容

研究方法

此项研究工作中全面涉及到对Cadence设计软件和Linux的使用。首先借助Oracle VM VirtualBox软件进入Linux操作系统的终端,使用icfb&各类不同指令程序,才能对应进到软件中进行设计,然后在设计软件外充分处理完各类运算工作,主要包括对Schematic和总体积分电路Schematic的操作任务。Cadence本身具有良好的仿真功能,然后结合TSMC 1P6M CMOS工艺的spectre模型库,运算放大器进行DC直流仿真,整体电路进行tran瞬态仿真,及时制作出类波图。由出现的各类仿真输出,对应调试不同的重要元器件的相关参数,最终实现整个电路效果的最优。然后,结合该软件另外一款工具——Virtuoso,对规定的电路图来完成设计效果,期间需要关注不同元器件之间的位置及对应关系。版图绘制完毕后,还得使用Calibre工具通过版图的DRC和LVS验证,本次课题的研究才能结束相关工作。

研究步骤

第一阶段,将与本研究课题有关的背景、意义及现状弄清楚,并整理问相关文档。

第二阶段,将与本课题有关的文献资料归纳出来,以此通盘了解积分电路的整体结构。

第三阶段,开始将本课题有关的电路原理运用逻辑图表现出来以备后用。

第四阶段,在Cadence中正确使用Schematic来作图,并将确定的电路图正确绘制,检查后确定并存档。

第五阶段,在Cadence中应用Spectre做仿真,仿真电路逻辑,使其能够得到仿真结果,以实现积分电路的作用;

第六阶段,在Cadence中使用Virtuoso来对电路逻辑进行实现,绘制出完整电路板,以此对版图进行优化处理,最终使用Calibre验证工具来保障最后的产出结果。

电路元件参数的选择

若在操作中,对于积分时间按照常数来设定,那么可进一步确定电阻R和电容C的值。根据积分电路原理,反相积分器的输入电阻,且时间常数,可以得知电阻R的取值越大,越可以更好地提高积分器的输入电阻。但是增大电阻R,就必须相应的减小电容C,这又会导致积分漂移想象的加剧。并且随着电容器的容量增大,漏电情况也随之加剧,同样也使得积分误差增大。综合考虑这些方面的原因,积分电容C最好不要超过1μF。因此得出结论,电阻R和电容C的参数的选择应该是在满足积分电路输入电阻要求的前提条件下,尽可能地选择使用比较小的R值和较大的C值,并且电容C值以不超过1μF为宜。

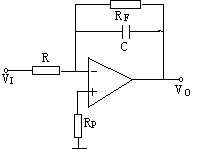

图2.4 反向积分电路

若用积分电路来进行一般的波形变换,那么应该选用基本的反相积分电路,如图2.4所示。在实际电路中,为了尽量减小积分漂移带来的影响[4],在研究设计积分电路时,应增加使用适当的补偿电路。

比如:

①首先对进行设定,要保证对于这个静态平衡电阻的设计,能够使得电流在非常状态中所产生的损失。值大小设计上,按照。

②再来针对 求解。

正常情况下,结构的上要保障在积分电路中的电容两端做个并联设计,由此产生了电阻。这个电阻的置放就是为了预防在积分漂移时候,会过于饱和或者自行停止的状况。在控制误差使其尽可能小的情况下,通常要求。

选择运算放大器

在积分电路中,应当选择输入失调参数小及漂移较小的集成运算放大器,来减小积分漂移。同时也应当选择开环增益变化很大同时增益带宽也变化较多,另外对于输入电阻要选择那些电阻高能够实现集成放大运算的部分,只有这样才能减轻给积分电路带来的输出电压的影响[5]。

单元电阻的选择

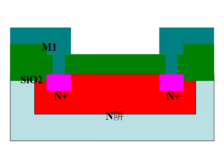

阱电阻

阱电阻,顾名思义就是用阱来做电阻的主体,在 P 衬底工艺下阱电阻一般使用 n well 层来实现。因为阱是低掺杂, 方块电阻大, 可以用阱来做大阻值的电阻。但是阱电阻的精度不高,自身误差很大,这就会使得阱电阻的大小会有变化,不能准确确定。于是就可能出现不合适的情况,后续就更难得进行配对。因此,一般使用阱电阻来做相对要求不高的低值电阻,像日常使用的PAD中的拉电阻,就是利用这个原理。

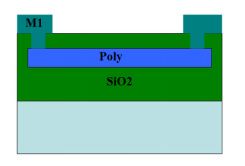

图3.1 N阱电阻的工艺实现

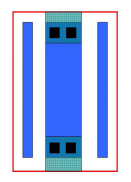

图3.2 阱电阻版图

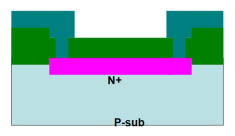

扩散电阻

所谓扩散电阻,其最大特点是能够在阱部或者衬底部的扩散区使用P+或N+电阻的方式。利用衬底部的物理特性,做成能够具备扩散特定的电阻,阱和衬底的参杂浓度要比P+/N+扩散区低得多,这也是直接导致两种电阻性能差别的主要原因。因为扩散电阻的参杂浓度高,在一定的压差变化下,扩散区中的反型层厚度会变小,电压变化就不会那么敏感,因此它的匹配性要比阱电阻好。

图3.3扩散电阻的工艺实现

图3.4 扩散电阻版图

poly电阻

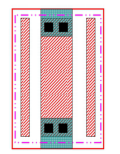

多晶硅电阻,又称为Poly电阻,指的是在单晶硅结构中混合了P+或N+,使得其具备低电阻率特性的电阻。在硅衬底上沉积化学特性的离子质,使其电阻大小发生改变,掺入杂志的质浓度的不同会影响阻值大小,一般来说轻度的杂志使得多晶硅电阻方块电阻阻值可以达到几百甚至几千欧姆,而重搀杂电阻阻值在通常只有几十欧姆。因为poly电阻的偏差比较小,并且其温度系数可以通过参杂离子的浓度进行控制,同时在版图设计中不需要单独的岛,所以通常情况下,poly电阻是非常好的选择。

图3.5 Poly电阻的工艺实现

Poly电阻版图

如果要减少应力的作用、少干扰电阻,不要出现突然某地方电阻超大超过负荷的情况,因此在绘制版图时候,不要出现扭曲式的线条,注意在连接处设计好电阻的连接形式,在串联结构中要加入金属连接。此外,如果想保证电阻的精确程度,使其内部环境一致且对称,通常需要在电阻的边缘添加虚拟(Dummy)电阻。此次版图的设计采用的就是Poly电阻。

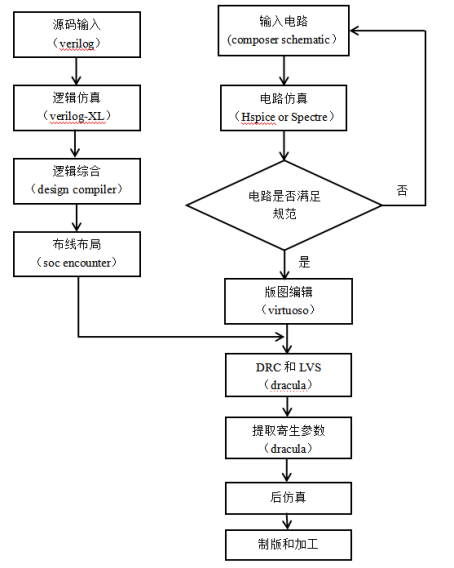

版图设计流程

接下来要进行集成板图设计工作。该工序流程主要有:首先要进行电路的输入处理,然后要进行一些简单的手工计算,接着绘制一些原理仿真图,做好版图的匹配及寄生参数的仿真工序,最后需要重检并评估效果[12]。

集成电路版图设计流程图

在设计版图工作中,主要的工序有:

1、在打开Cadence 5.1系统软件之前,先将Linux操作指令icfb&启动开;

2、利用Cadence设计软件在自己的库中新建一个版图的View,选择Virtuoso工具在这个View中绘制版图;

3、调用所需要的电路元器件;

4、按照电路原理图和匹配规则摆放好各个元器件,并将各器件连线,并进行优化处理;

5、完成版图设计并检查无误后,进行DRC验证。先找到上方项目中并点选Calibre,接着Run DRC,做好路径设定,然后可以看到DRC,在界面中找到Input选项,打开后选择需要用到的drc文件,紧接着进行运行。运行后,如果听到报错提示,查看错误提示逐项修改,一直到最后没有错误就停止操作,进行保存,完成DRC的验证。

6、进行LVS的验证。先点击工具栏中的Calibre,然后点击Run LVS,选Rules的规则和DRC相同,在Inputs界面时,为了可以在修改网表后版图验证的网表可以同时修改,要把Netlist中的Export from schematic viewer勾选。

在运行LVS时候,出现先这些情况,需要分别处理:一种情况是,Device数目不对,这时候杂版图上看看有没有需要改正的地方,改调后选择必须的器部件做填充,这步骤需要很细致检查原有设计中的器部件数目及位置,然后在来操作;第二种情况也非常容易出现,主要是在设计时候稍不留神连接少了一根或者出现短路,虽然问题不大但是错误很严重,需要及时调整;第三种情况是,在power操作中出现漏连接等失误。

版图的匹配规则

在设计中,即使是在做模拟电路,也需要设计好元器件位置及数目,注意对称性设计思路,也就是所谓的匹配性。比如,差分电路就需要高度的对称性设计,一旦匹配失效,那么可能出现失调电压数值,对于共模比值带来较大变化,最终影响一系列指标值,最终使得整体电路系统性能变得很差。通俗说,如果两类器部件的环境差不多,两者即为匹配度高。

要实现较好的匹配性能,及需要做到:

(1)注意器部件之间的位置关系,不要距离太大;

(2)在位置设置上,需要关注方向,相匹配的器部件所置方向应该一致。

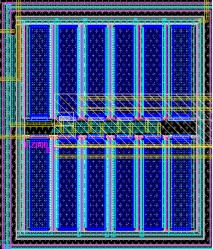

图4.2 差分对管版图

由上图4.2所示,如果途中的两组差分版对管环境相同,按照相反方向放下,在相同工作器件沿着相同方向处理,就会产生极大地对撞及摩擦,最终呈现不匹配的后果。对于匹配的好坏,可以根据“栅阴影”特性去做选择。注意不要让离子进入到工艺沟到中,因此在设计时候,可以将倒入方向调整微微倾七度。这种方式可以形成“栅阴影”,同时避免离子进入工艺沟道。

(3)注意在器部件设计时候,让宽度尽可能等于长度;

(4)差分对管都往中间位置设计;

(5)尽量选择常规匹配结构,比如叉指型、共质心型等。

(6)学会使用Dummy虚拟器来保护匹配结构

(7)注意仿真参数值同寄生参数值的对应关系

结论

本篇文章重点介绍了集成电路以往的发展过程,最初仅仅是有粗略构思,后来使得其技术实现能够精确到纳米度。然后,还归纳了国内外目前集成电路的整体发展情况,了解了模拟积分电路在通讯系统、自动控制系统、国防军事等诸多领域中获得了广泛的应用。

就本次课题研究,先是介绍了积分电路的工作原理,并对其进行了理论分析,熟悉并掌握了其功能是怎样实现的,根据NMOS低电平导通,PMOS高电平导通的原理,设计了此模拟积分运算电路的原理结构,同时正确运用Cadence来仿真,将电路图中的重要性能参数进行测试仿真,还能够仔细说明各种仿真中需要用到的工具及过程。而且也详细说明电路板图勾画方法及过程,并将最后的版图表现结果进行表现,同时解释LVS验证结果。在版图结构中,本论文使用了Cadence设计平台,采用 TSMC 1P6M CMOS 工艺设计,这种工艺会有更好的集成度,对积分电路版图勾画完整性进行设计及检验,运用到了器件匹配思路,例如差分对管应该在设计中用到交叉匹配及共质心约束,还提到对于抗干扰的提前设计,强调Dummy保护环的重要性,以保证电路内部工作环境的一致,以及需要多开凿衬底、阱电位接触孔,避免出现闩锁反应;结合模块的处置地点,保证连线不要太长,同时版图的面积尽量小。随着科学技术的不断创新,集成电路工艺的不断减小,这样的电路表现的参数值会被改进,最终变得更为精确,同时能耗较低等效果。

这个版图设计工作,是结合模拟积分运算而设计的,通过版图的实现完整展示了积分运算效果,而且能保证高匹配同时还具备很好的卡干扰性能,最终在实验中也满足DRC及LVS的测验,能够给较好的做成模拟实验及版图的设计实现。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?