思路

-

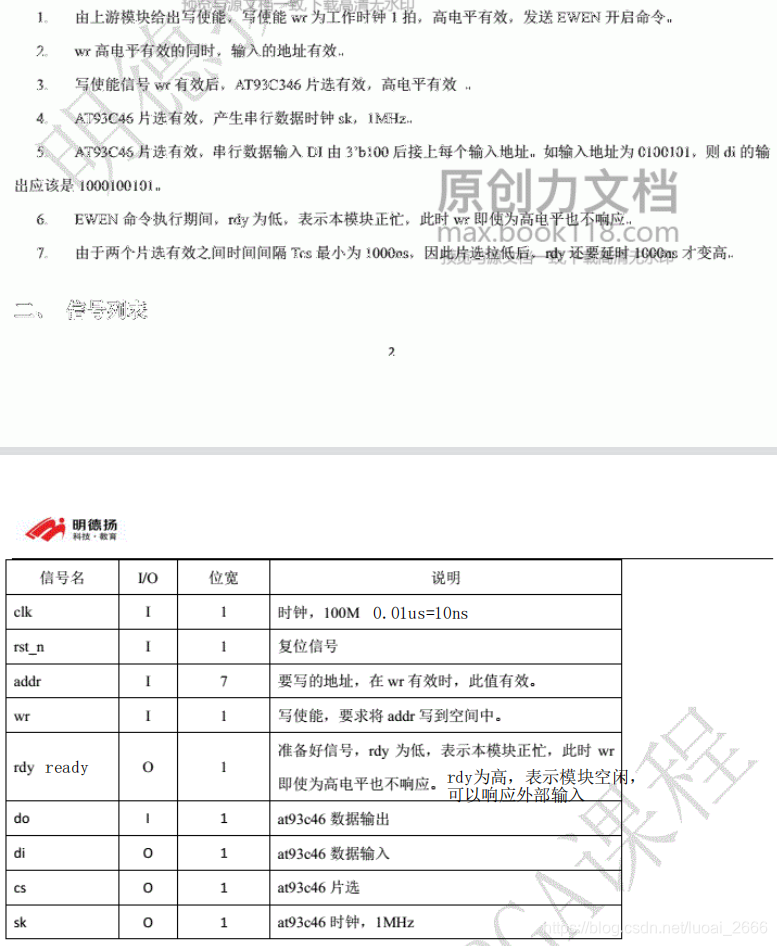

明确功能 输入输出信号列表+功能描述

rdy信号可以防止在运算过程中,外部又来wr和数据导致的会乱。 -

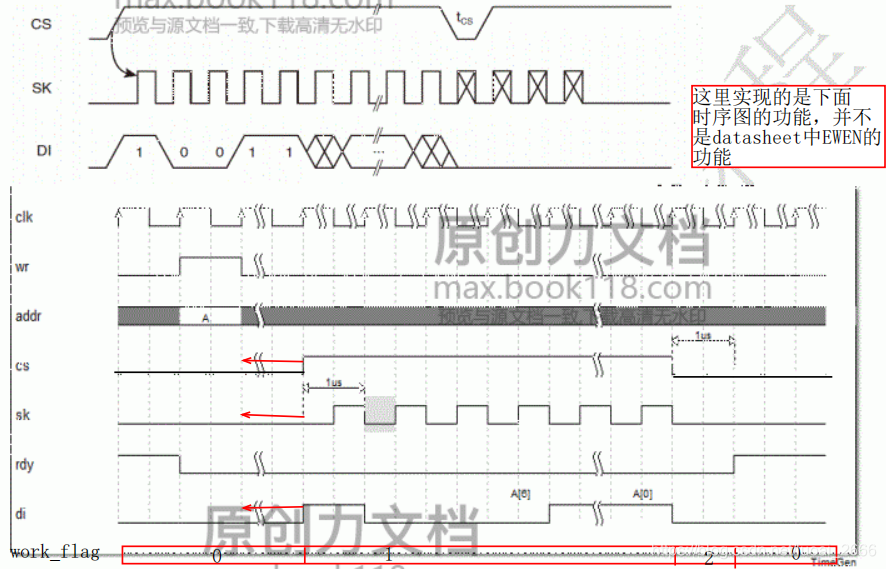

画功能波形图 明确每个信号的变化情况

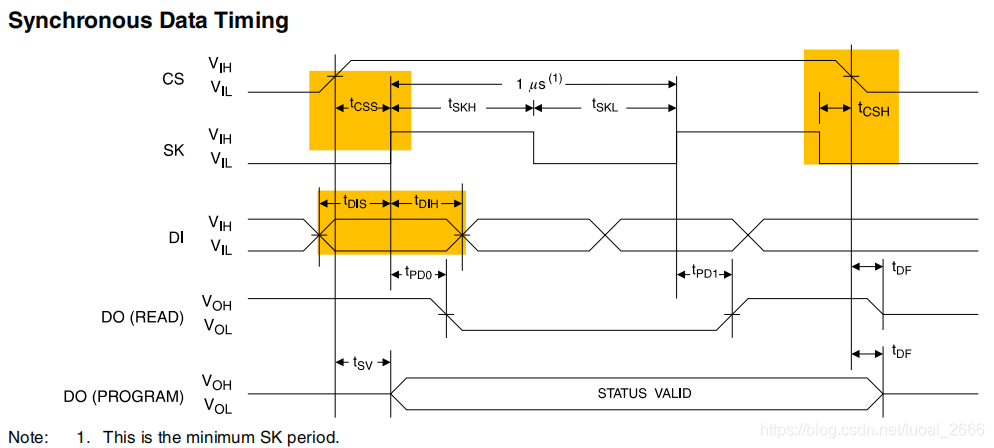

不能违背器件datasheet的时序要求

查阅datasheet可知,假设电平标准为2.7V~5.5V。fSK max=1MHz,1us; tSKH和tSKL min=250ns, 下图是500ns;tCSS min =50ns,下图留有0.5us;tCSH min=0,下图=0;tCS min=250ns,下图=1us;tDIS=tDIH min=100ns,下图=500ns。均满足要求。

-

确定计数器结构

cnt0 计数1us

需要引入计数标志信号work_flag

//add_cnt0 = cs==1; 错。cs拉低后仍计数了1us,不能用来做标志位

add_cnt0 = work_flag!=2'b0;

end_cnt0 = add_cnt0 && cnt0==99; //100-1

cnt1 计数几个1us

add_cnt1 = end_cnt0 && work_flag==2'b01;

//也可写成 add_cnt1 = work_flag==2’b1 && cnt0==99;

end_cnt1 = add_cnt1 && cnt1==9; //10-1

- 其他reg信号 初值,变化点,else保持or归零

变化点应精确到每个clk

a) work_flag [1:0] 引入计数标志信号,分两个计数阶段,其中第1个阶段cnt0, cnt1均计数;第2阶段只有cnt0计数

初值0 else保持

0to01: wr1 01to10: cnt19 && cnt0== 99 10to00: cnt0==99不对

光用计数值作为变化点不够区分,应该加上work_flag自身状态

reg [1:0] work_flag;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

work_flag <= 2'b00;

else if(work_flag==2'b00 && wr==1)

work_flag <= 2'b01;

else if(work_flag==2'b01 && cnt1==9 &&a

本文详细解析了如何设计嵌入式系统中的计数器,通过工作标志、时序控制和信号同步,确保在fSK调制和数据传输中避免混乱。涵盖了rdy信号的保护作用,以及根据datasheet规范设置的精确时序操作。通过实例展示了work_flag、sk、cs和data信号的变化逻辑,并结合测试模块进行验证。

本文详细解析了如何设计嵌入式系统中的计数器,通过工作标志、时序控制和信号同步,确保在fSK调制和数据传输中避免混乱。涵盖了rdy信号的保护作用,以及根据datasheet规范设置的精确时序操作。通过实例展示了work_flag、sk、cs和data信号的变化逻辑,并结合测试模块进行验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

890

890

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?