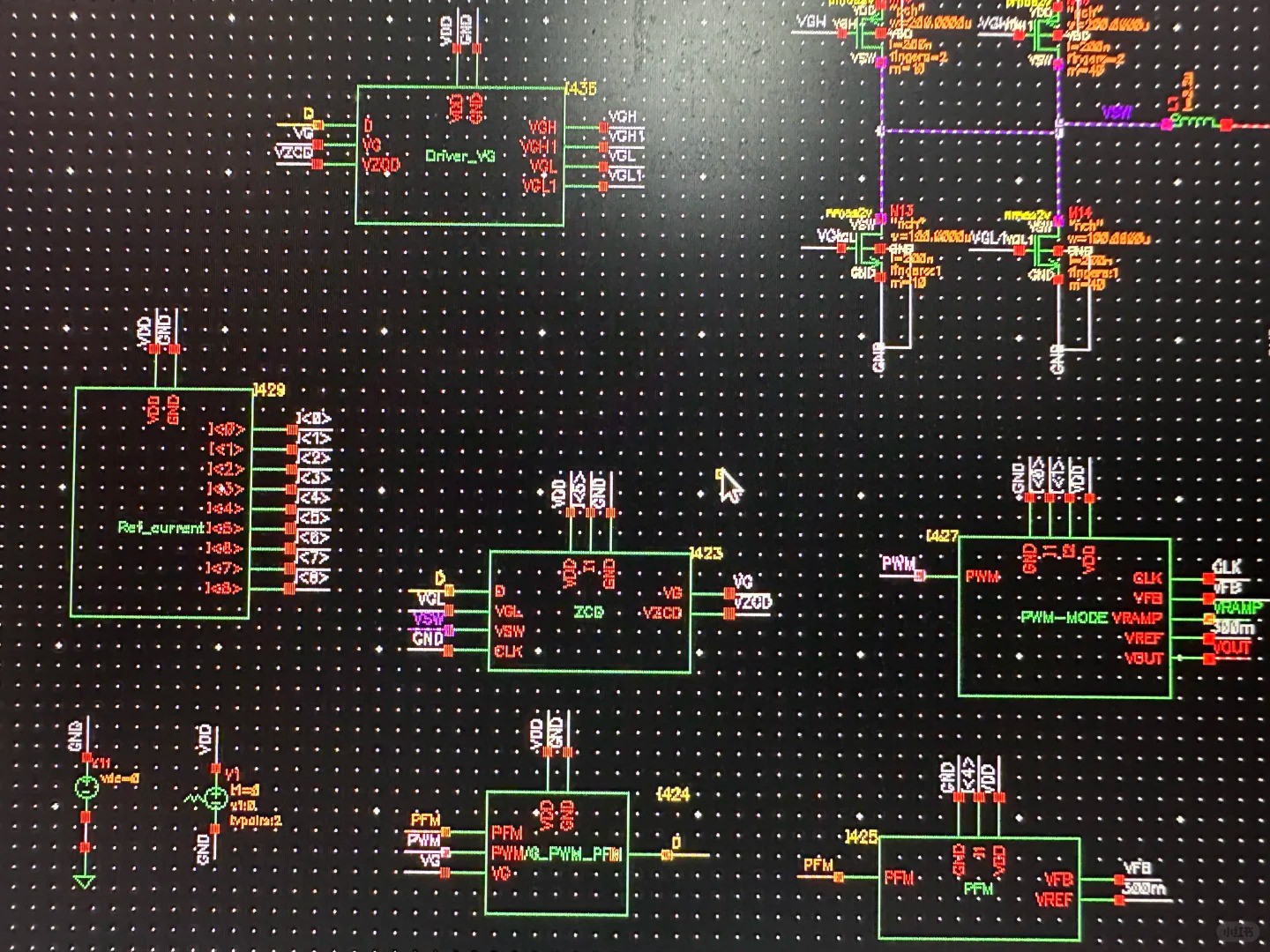

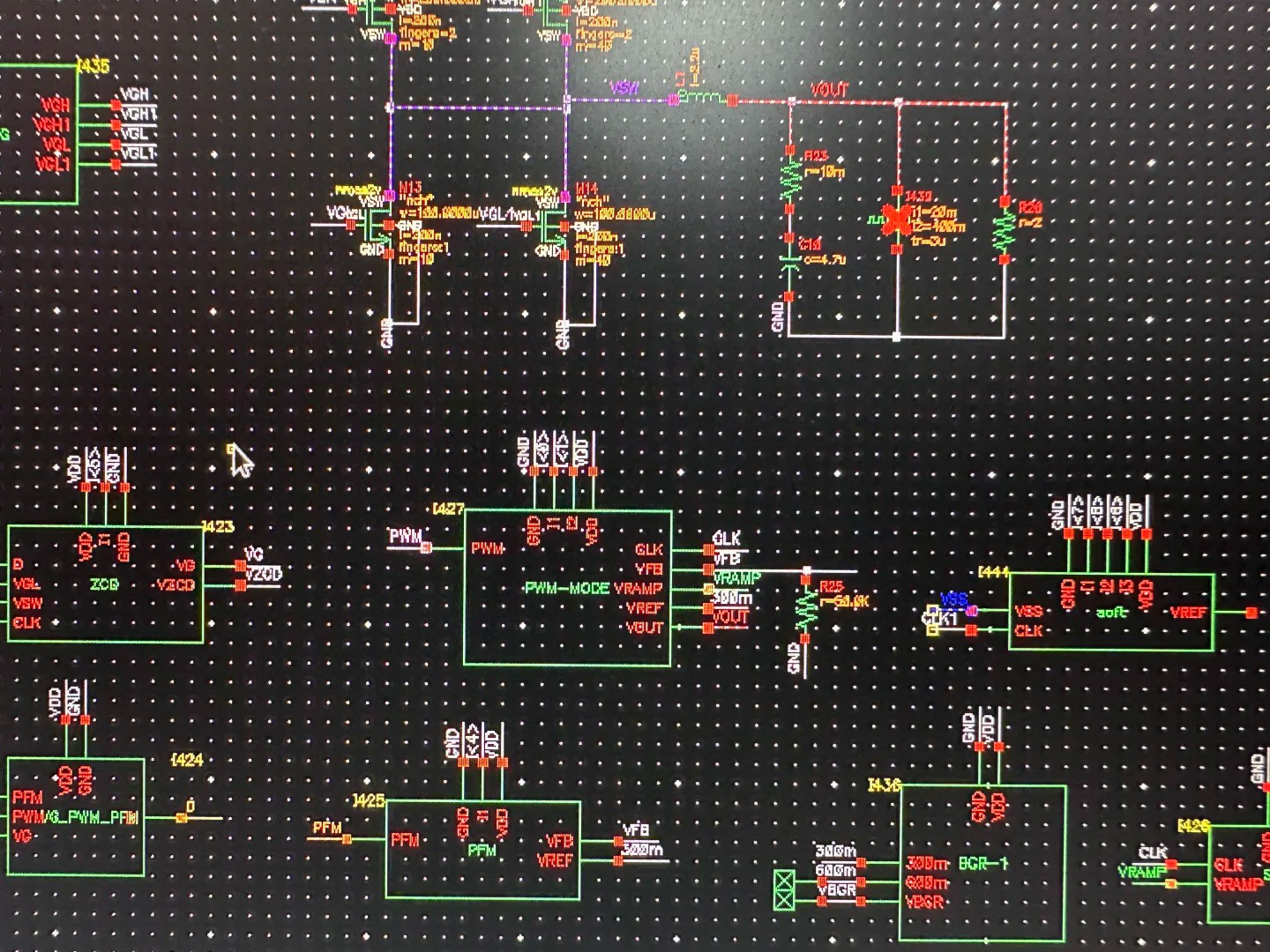

DCDC电路,模拟ic设计,集成电路设计,tsmc0.18um工艺,正向设计,PWM+PFM混合调制。 有比较详细的设计仿真报告,重载PWM,轻载PFM。 输入电压1.6-1.8V,输出电压0.4-1.2V。 有基准电流模块,基准电压模块,PWM模块,PFM模块,振荡器,比较器,误差放大器,零电流检测电路,斜坡补偿电路等等模块。

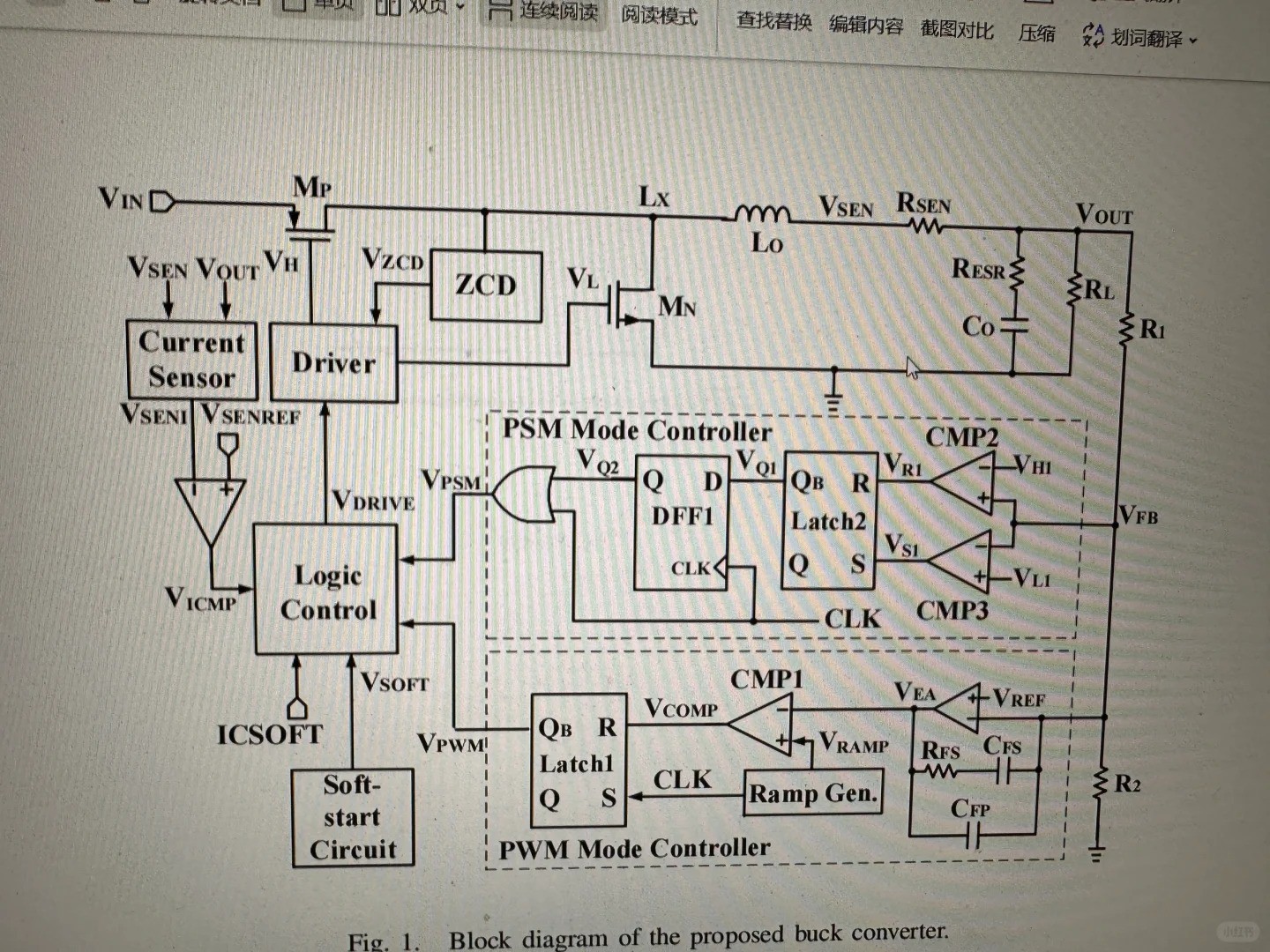

最近在TSMC 0.18um工艺上折腾了个有意思的DCDC电路,输入电压最低能到1.6V(两节干电池快没电的状态),输出却要稳定在0.4-1.2V可调。这玩意儿最让人头秃的就是如何在重载和轻载时自动切换PWM和PFM模式——就像给电路装了个智能节油开关,负载重时猛踩油门,负载轻时挂空挡滑行。

先说基准模块,这相当于整个系统的定海神针。用了个改进型beta-multiplier结构做基准电流源,关键代码长这样:

// Beta-multiplier核心代码

MN1 3 3 0 0 NMOS W=2u L=0.5u

MN2 4 3 0 0 NMOS W=20u L=0.5u

R1 3 4 10k这个结构的巧妙之处在于利用电阻R1和MOS管尺寸差异生成稳定电流。仿真时发现温度系数能做到±25ppm/°C,比某些商业IP还稳。不过要注意TSMC18工艺的栅氧漏电问题,尤其在高温下需要加个补偿电流镜。

斜坡补偿是PWM模式的灵魂伴侣。传统三角波发生器容易受工艺角影响,这里用了电流饥饿型振荡器配合动态镜像:

Vctrl 7 0 DC=0.8V

Mcap 7 8 9 9 PMOS W=4u L=0.18u

Cramp 8 0 2p

Icharge 9 0 10u这个电路生成的斜坡电压斜率与Vctrl成反比,实测在1.6V输入时斜率变化范围刚好覆盖负载突变需求。有个坑爹的发现:当PFM模式激活时,必须给斜坡电容加隔离开关,否则轻载时斜坡电压会像漏气的气球一样掉下来。

零电流检测电路用了三级动态比较器链,前两级做失调校准,最后一级上动态锁存器。关键参数是这个:

.param I_zcd_thresh = 50nA当电感电流低于50nA时触发关断,实测能把轻载效率从72%拉到89%。不过要小心比较器的传播延迟,在layout阶段必须把检测电阻到比较器的路径缩到最短,否则延迟会让实际关断电流变成负数——别问我怎么知道的,烧过两个芯片才明白。

混合控制逻辑用了个状态机,核心判断条件很简单:

always_comb begin

if (load_current > 20mA) mode = PWM;

else if (vout_error > 30mV) mode = PWM;

else mode = PFM;

end但实际操作中发现纯电流阈值判断会有乒乓效应,后来加了滞回比较:切换到PFM需要负载持续低于15mA超过5个时钟周期。这招把模式切换时的输出电压纹波压住了3mV左右。

测试阶段最魔幻的是效率曲线——在10mA负载时PFM模式效率82%,当负载升到25mA切PWM后效率反而飙到91%。这说明两种模式的效率交叉点选择比找对象还讲究,得盯着仿真波形反复调教切换阈值。

最后流片回来实测数据:1.8V输入下输出1.0V/50mA时,峰值效率93.7%;待机功耗做到720nA,拿在手里芯片都不发热。不过有个未解之谜:每次上电时误差放大器都会先抖三抖,后来发现是基准电压启动时的毛刺在作妖,加了个软启动电容才搞定。

这项目让我明白,混合调制就像川菜里的麻辣平衡——PWM是辣椒,PFM是花椒,调得好是水煮牛肉,调不好就是工业酒精勾兑。下次打算试试在PFM模式里加入burst模式,看看能不能把轻载效率再顶上去两个点。

12万+

12万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?