设计示例

本章展示了前几章中提到的设计实现。内容包括完整的可综合状态机设计、多种不同的滤波器设计、FIFO 以及异步串行接口,还包含针对这些设计的一些测试程序。

状态机

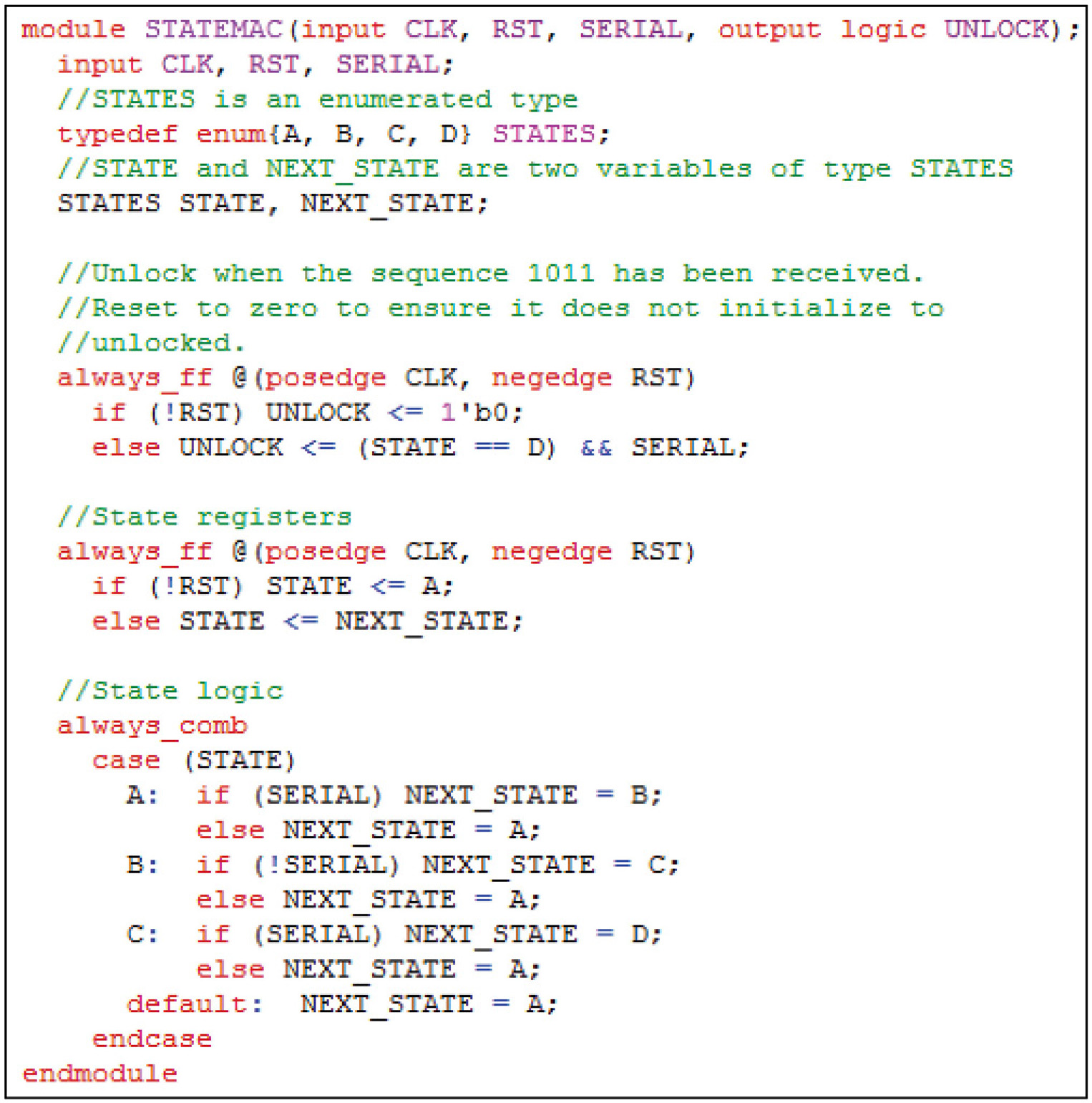

以下设计示例说明了如第4章所述,采用状态机创建设计的一种典型方式。状态向量在顺序代码块中被锁存到寄存器中。状态逻辑在组合逻辑块中实现。

图12.1中所示的设计是一个序列检测器。当检测到串行输入序列1011(最左边的位最先到达)时,它将使“解锁”输出在一个时钟周期内置为高电平。为了确保无论串行输入数据有任何延迟,解锁信号都能保持一个完整周期的有效状态,因此对解锁信号进行了寄存,这是模块输出中普遍接受的做法。

此设计示例使用枚举类型表示STATE,尽管在此情况下相比采用二进制编码的设计并无明显优势。输入序列必须在连续的时钟周期内提供。一个实际的数字锁会更复杂,因为它需要检测按键的按下和释放按钮,以及去抖动机电开关的复杂性,且仅在检测到有效的按钮按下时才推进STATE。

使用了两个具有相同敏感度的顺序块。这样做是为了突出状态机的结构。UN_LOCK 输出同样可以合并到状态向量赋值块中。这两个块都通过异步复位信号进行初始化,以便在上电后将设备置于一个已知且安全的状态。

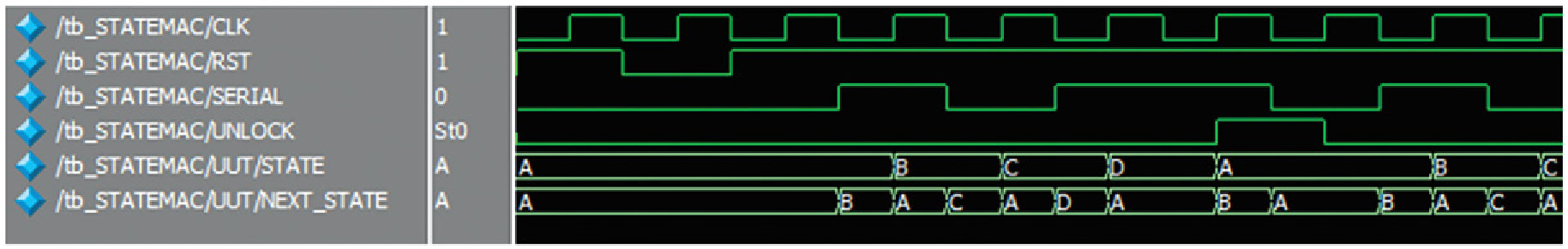

在仿真中,NEXT_STATE 变量的变化速度似乎是 STATE 变量的两倍。这是因为串行输入数据在时钟下降沿到达,而 STATE 变量只能在时钟上升沿发生变化。由于状态逻辑的组合逻辑电路对串行数据输入和状态都敏感,因此它可以在时钟周期内改变其值。这不仅不是问题,反而说明了同步设计的一个优势:组合输入可能在时钟周期内的不同时间到达,但只要它们有足够的时序余量以满足设计中触发器的时序参数,状态向量和输出将在整个时钟周期内保持稳定。

设计这种或其他任何序列检测器的方法还有很多。

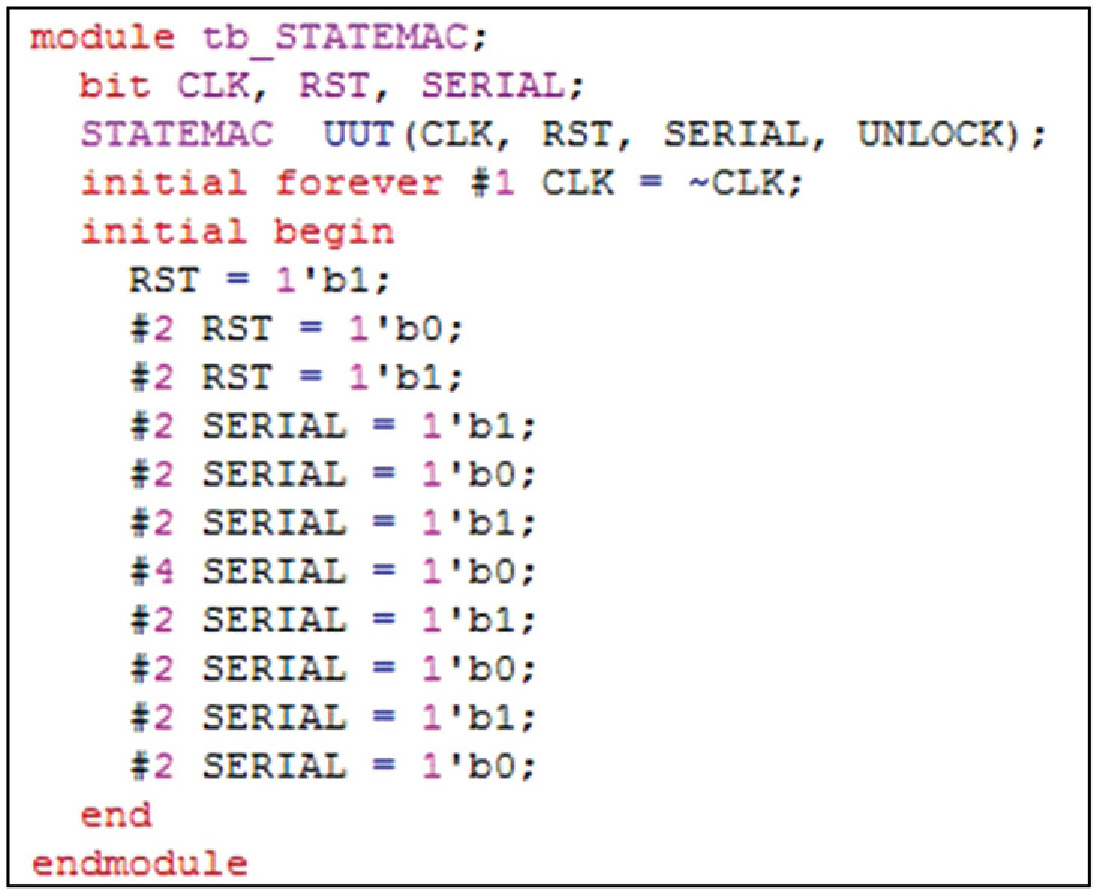

图12.1设计的一个小型且非全面的测试装置如图12.2所示。

图12.1 和 12.2 仿真的波形如所示。图12.3。

FIR滤波器

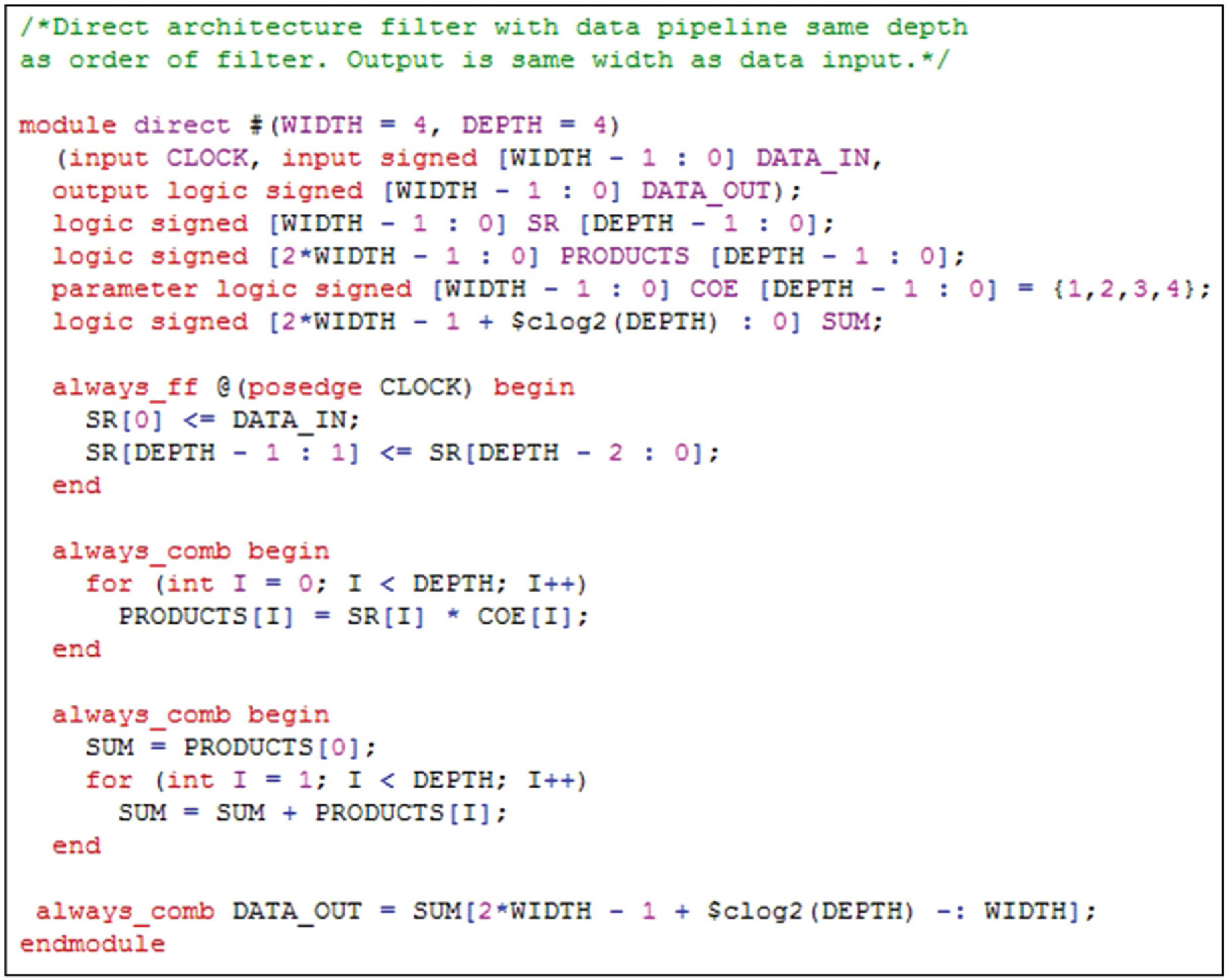

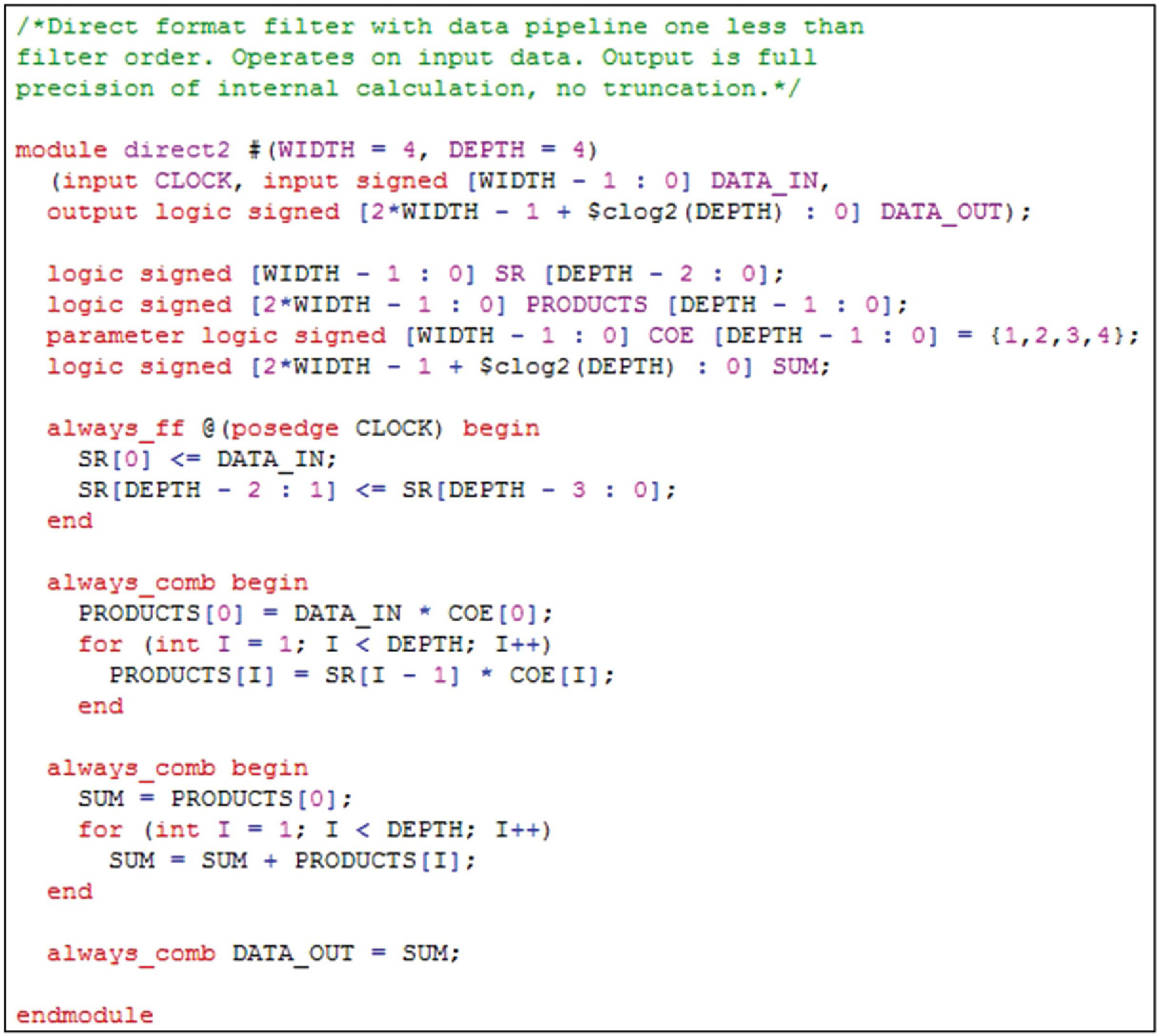

图12.4展示了最简单的直接型有限冲激响应 (FIR) 滤波器。它是图9.12中所示架构的一种实现。在此实现中,输出为

与输入相同的宽度。计算中使用的较低有效位被截断。滤波器系数在声明为参数时被赋值。在此演示中,它们被赋值为1、2、3和4。

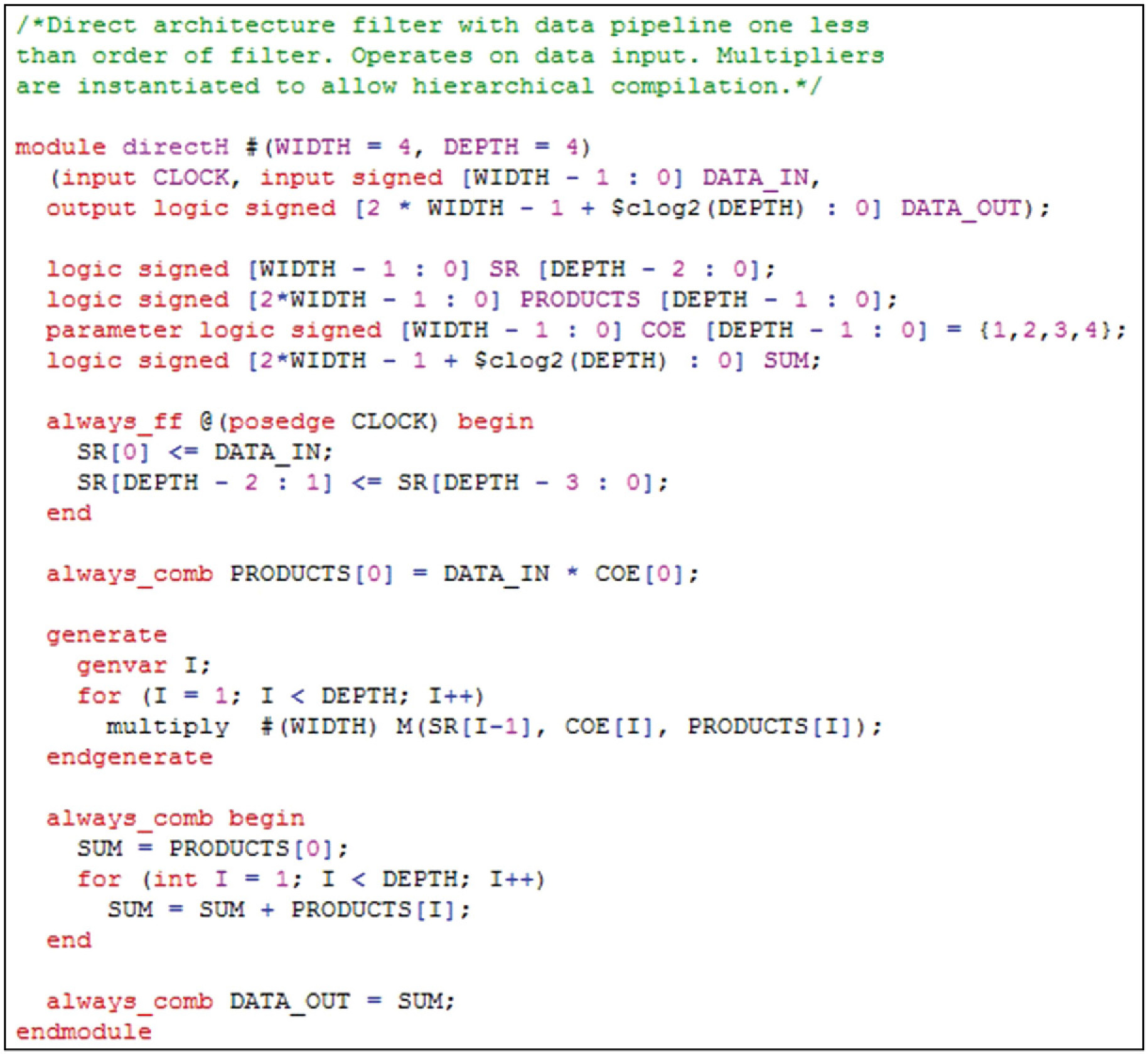

图12.5展示了图12.4设计的一些微小变化。在此实现中,数据流水线少了一个字,第一次乘法运算在输入数据时即进行数据。另一个变化是不进行数据截断。用于生成乘积和的所有位都会被输出。

图12.6 与 图12.5 相同,只是乘法器位于单独的模块中,并被实例化而非推断。这允许分层编译,当滤波器阶数较大时,这一点变得必要。

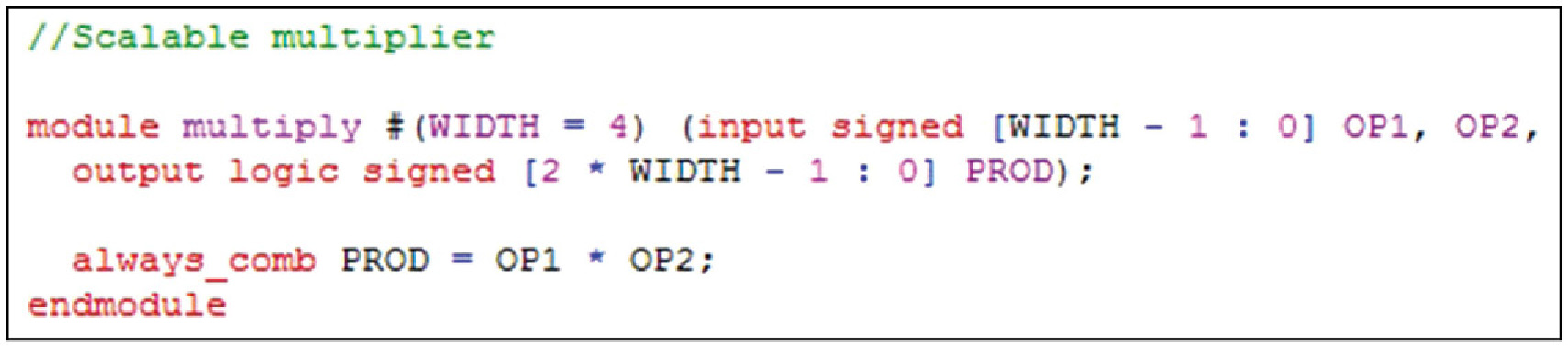

实例化乘法器如图12.7所示。

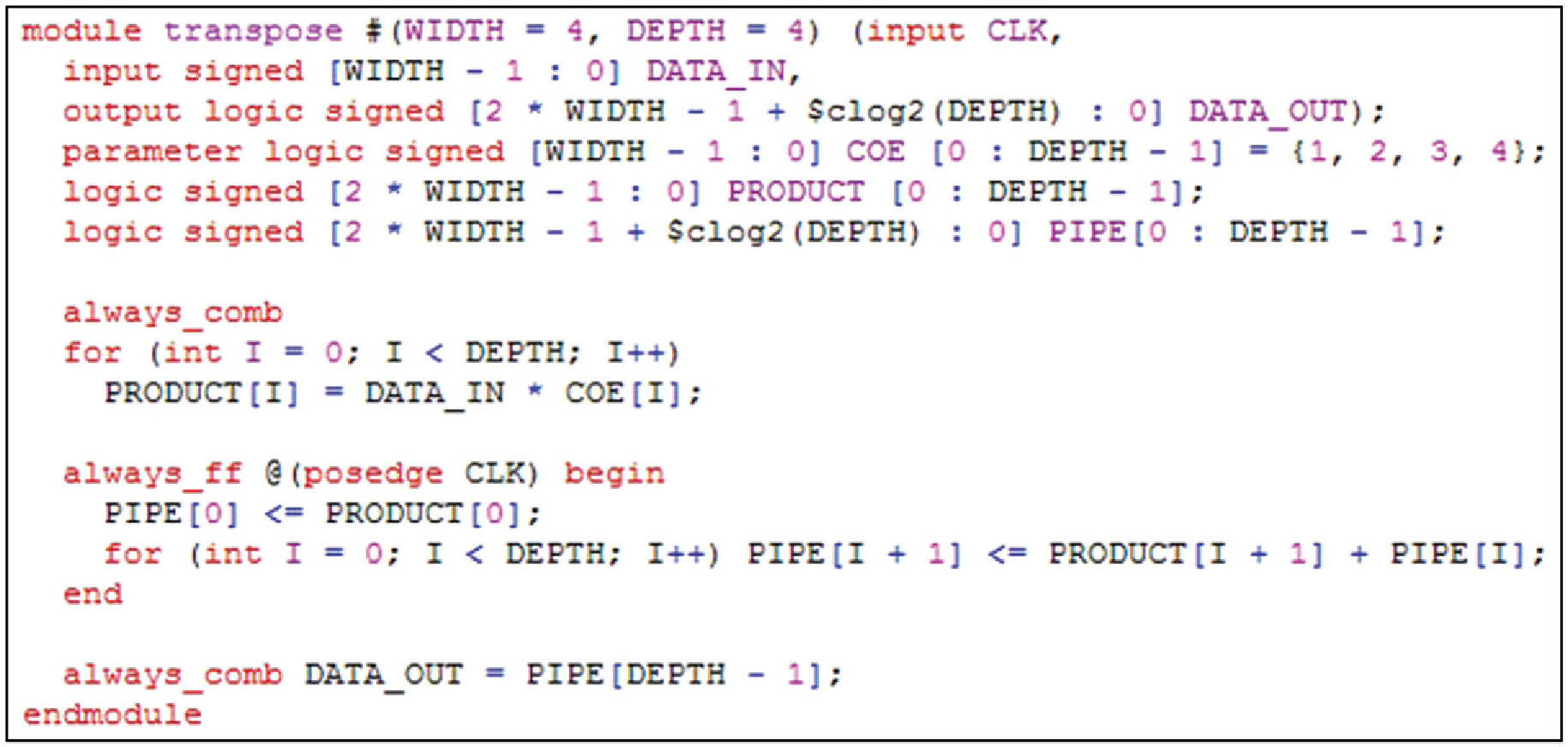

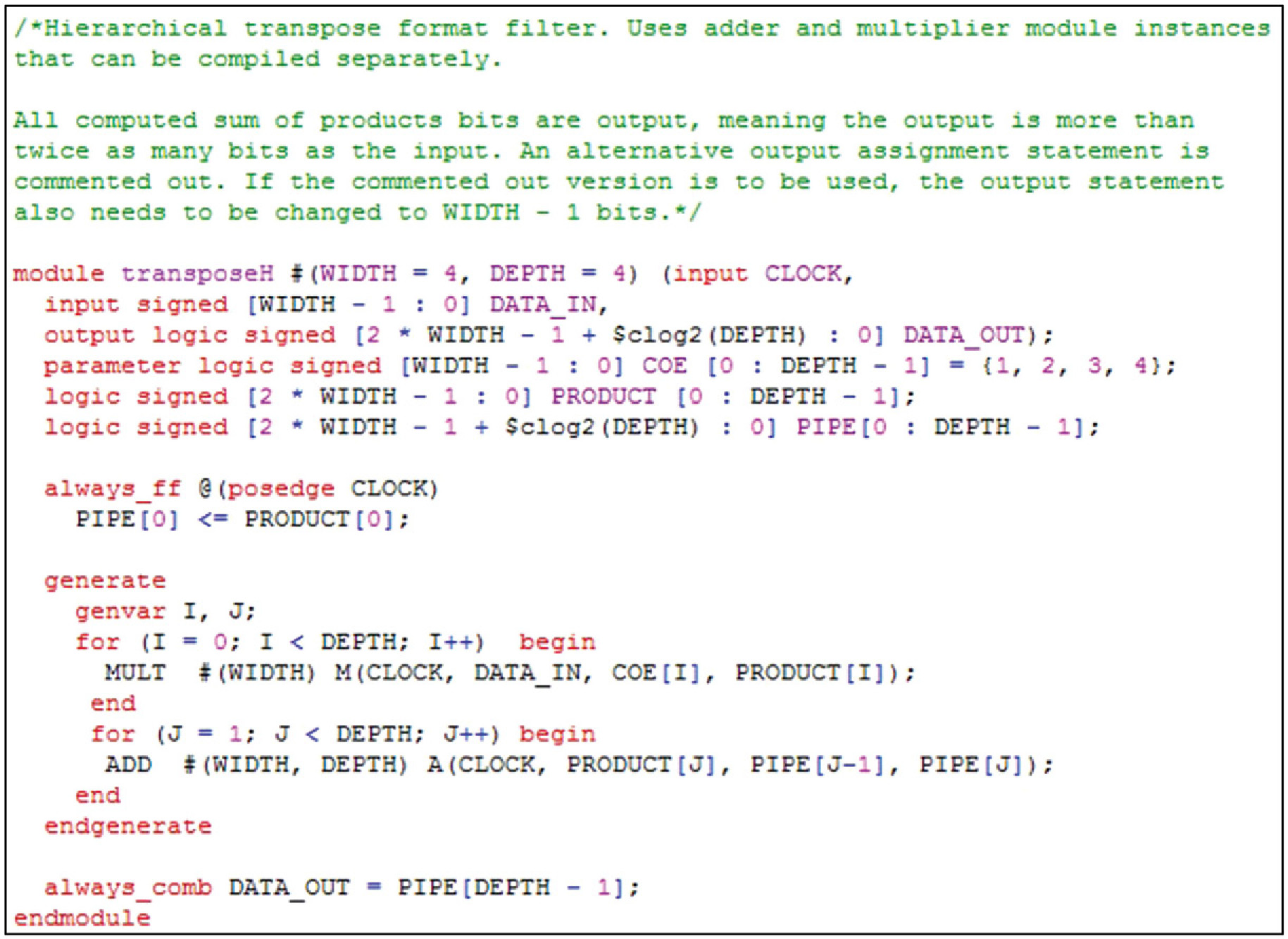

转置结构架构的模板如图9.13所示。该架构的可扩展实现如图12.8所示。

为了允许合成大型滤波器,图12.8的设计已在图12.9中进行了修改,将算术运算分解为可单独合成的独立模块。在这种设计风格中,内部操作数随着滤波器的级数增加而增长,因此加法器的规模需要大于输入数据大小的两倍。通过使用对数上取整函数来增加加法器的规模,以满足最坏情况下的操作需求。该设计对乘法器和加法器的输出都进行了寄存。这样做的目的是提高工作速度,但代价是增加了面积、功耗和延迟。

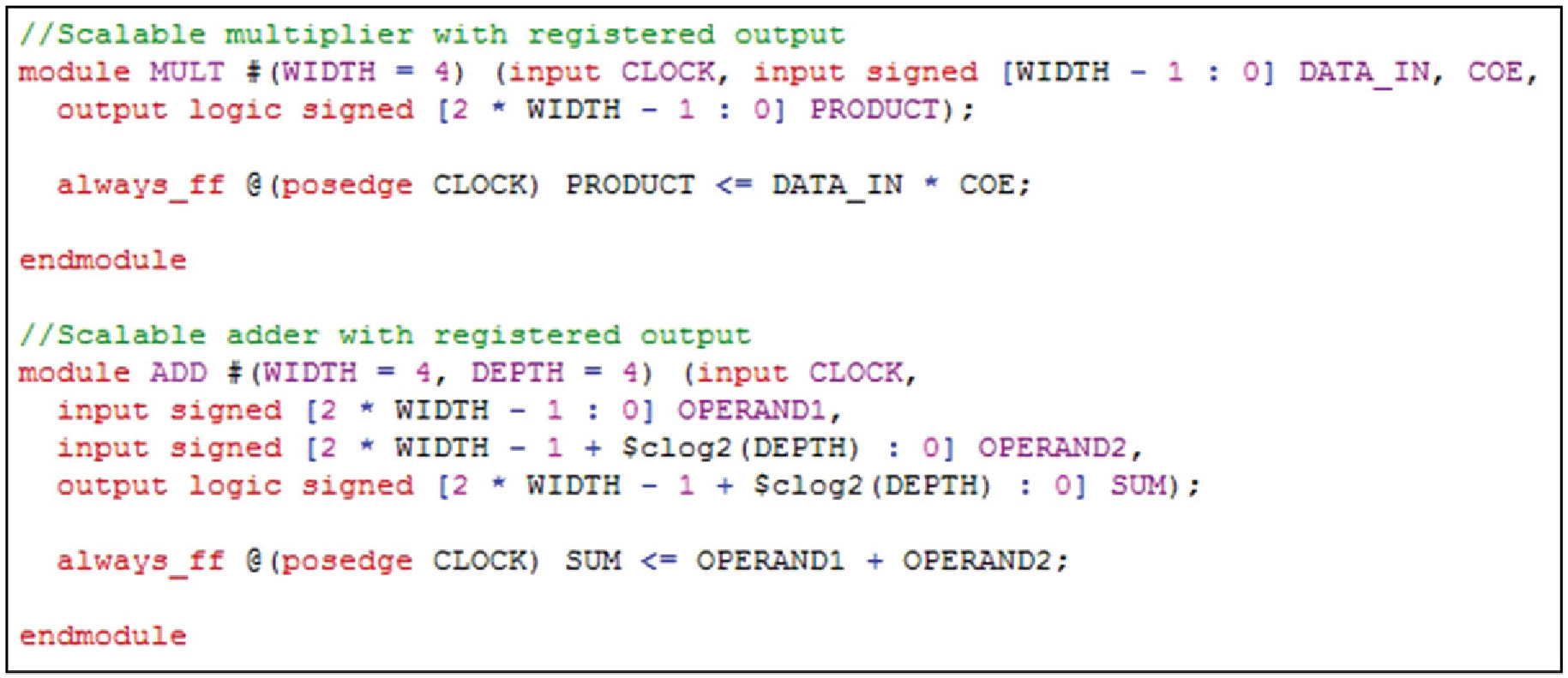

图12.10展示了分层转置结构滤波器设计中使用的寄存器输出加法器和乘法器,该设计见于图12.9。

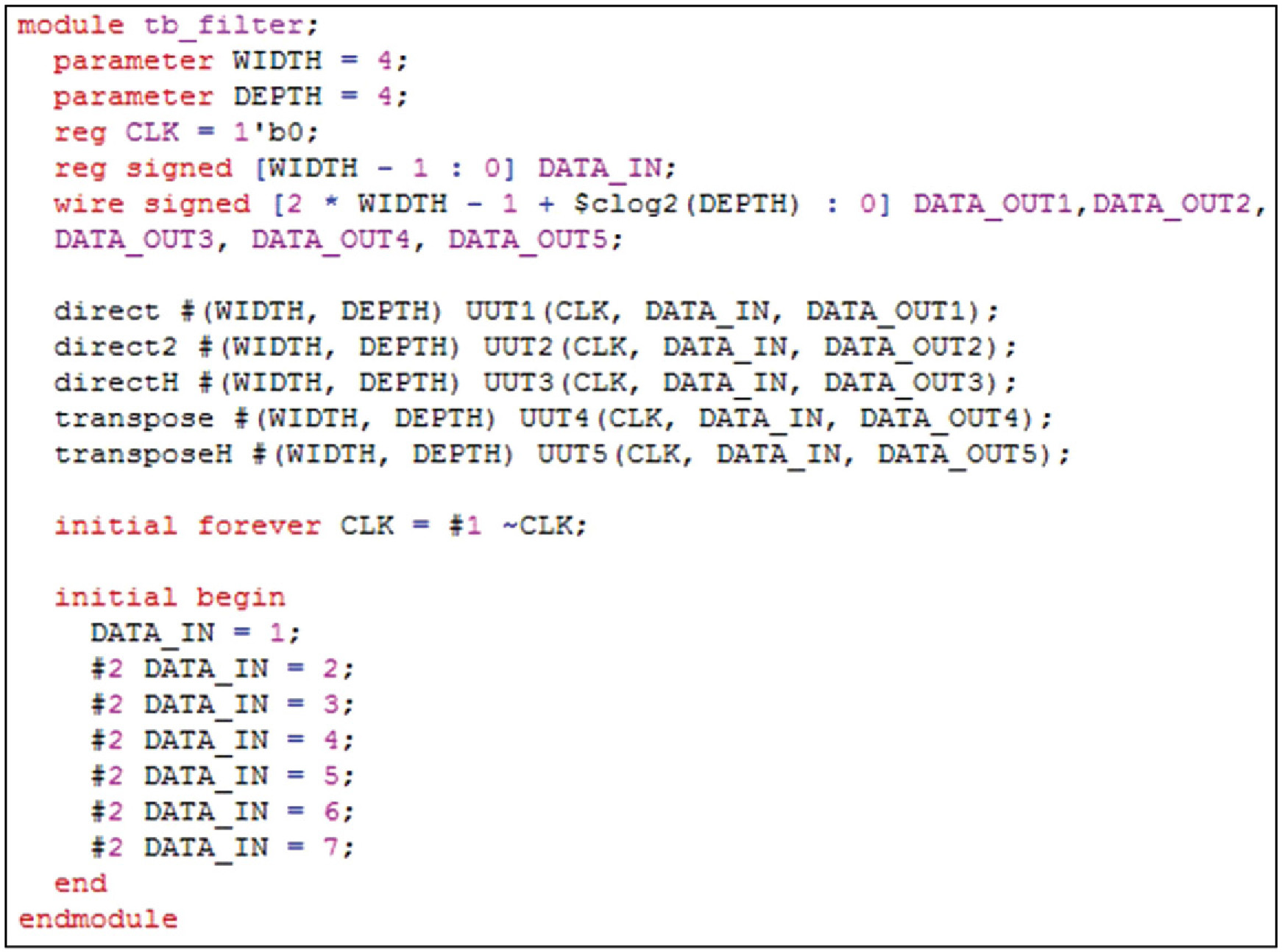

图12.11展示了一个小型测试装置,用于并行运行上述所有滤波器模型。在该测试装置中,所有输出均设置为全精度,而不是像图12.4中那样使用截断。由于不同实现方案的流水线级数不一致,五个滤波器的输出之间最多可能存在三个时钟周期的偏移。直接对输入数据进行操作的实现方案,其输出跳变可能也比那些在使用前先寄存数据输入的方案更多。对于这些实现方案(直接型和直接H型,图12.5和图12.6),输出数据可能在整个时钟周期内并不总是有效。这是由于未对输出进行寄存,且测试装置在时钟下降沿而非上升沿改变数据输入所导致的。此类设计技术并非在所有工作环境中都可接受。将这些模块中的最终always_comb语句改为always_ff @(posedge CLOCK)可以寄存输出,从而消除虚假的临时输出值,但代价是增加一个时钟周期的延迟、更大的面积和更高的功耗。

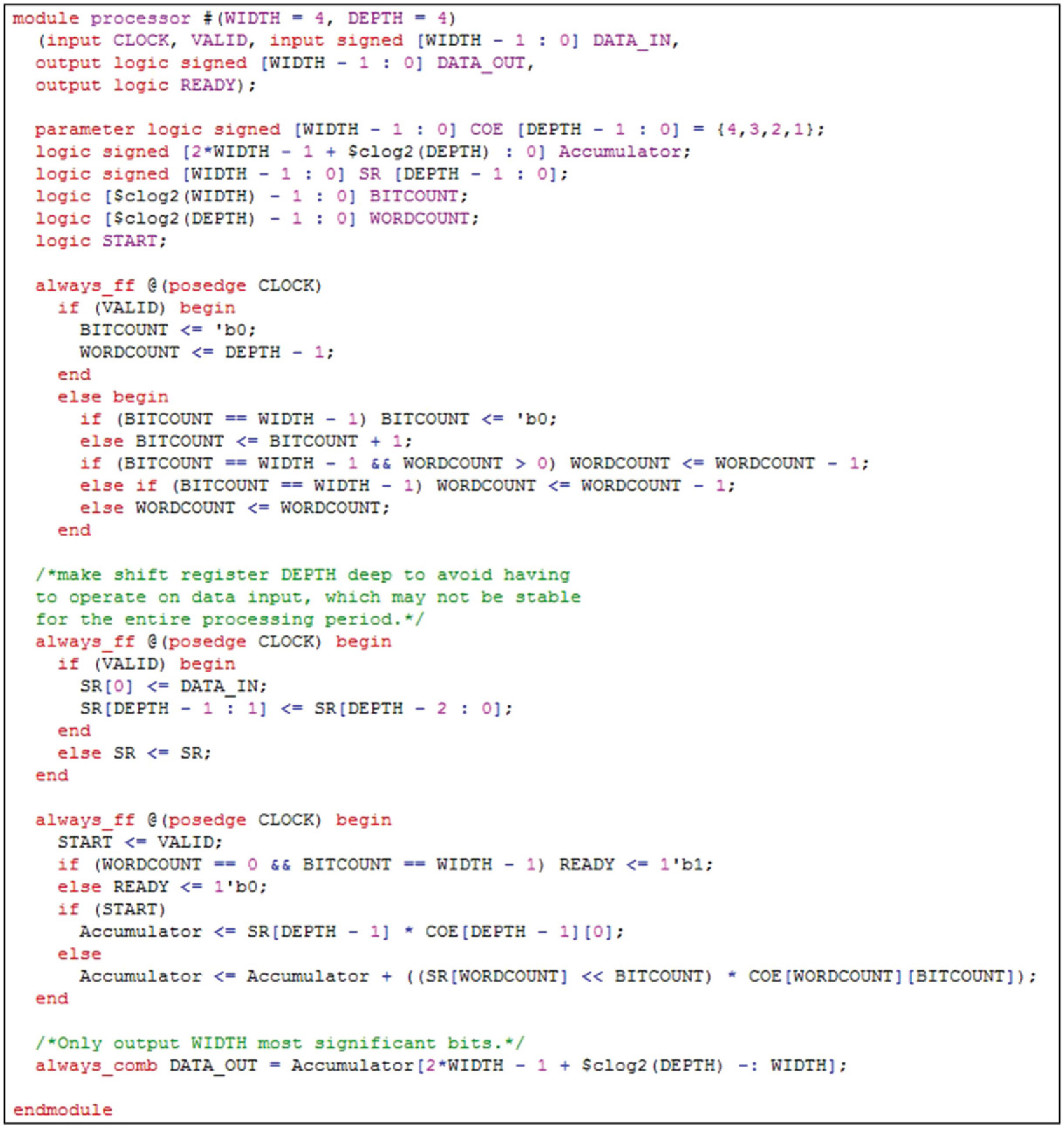

如图9.14所示的可扩展处理器架构滤波器的一种实现如图12.12所示。它对所有算术功能仅使用一个加法器,因此处理每个数据字需要 WIDTH × DEPTH 个时钟周期。之前的 所有实现在单个时钟周期内完成操作。

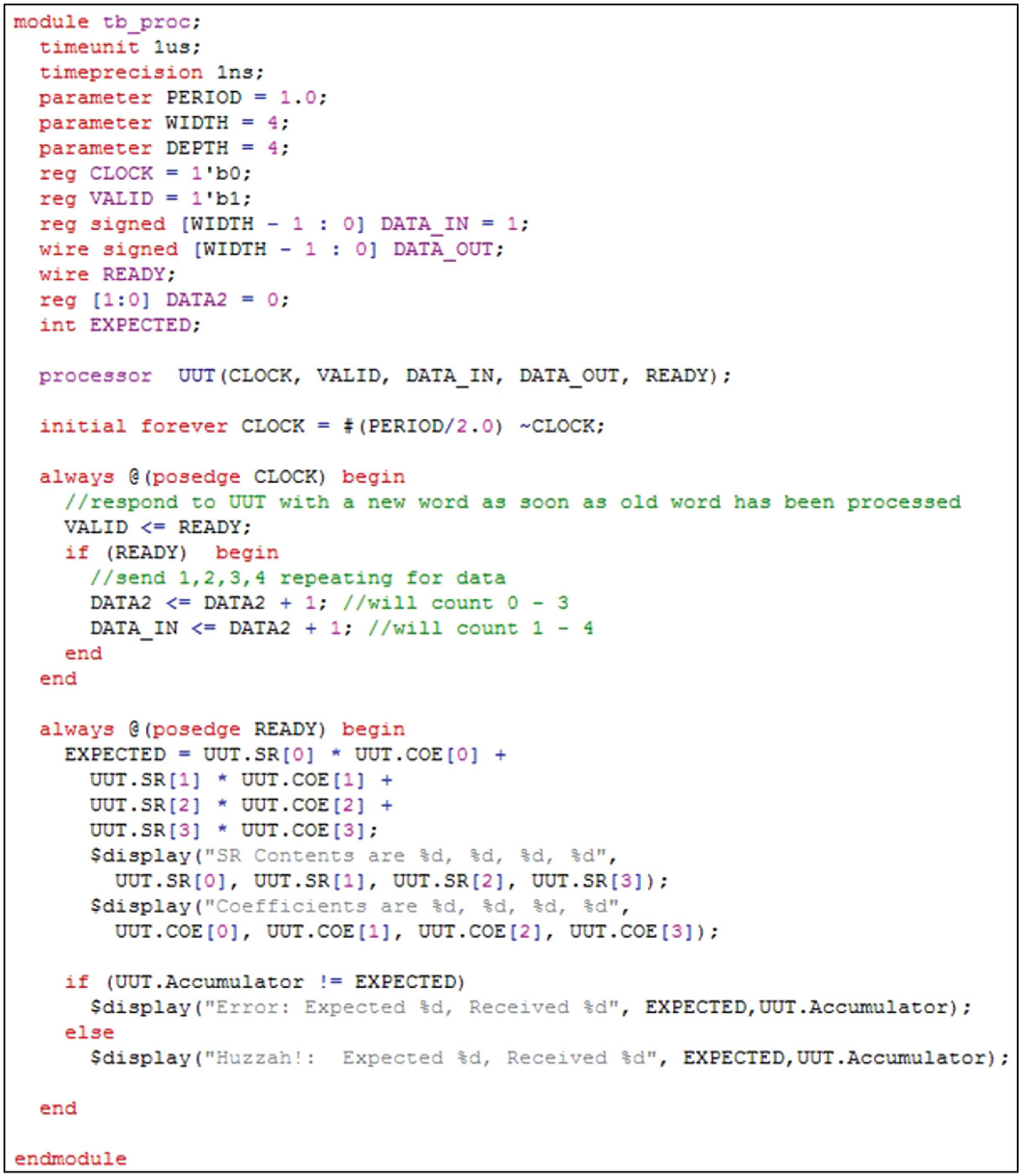

处理器风格滤波器的测试装置如图12.13所示。使用提供的测试数据时,输出始终为零,因为只有乘积和的最高有效位连接到输出,且系数和测试数据均使用了较小的数值。包含的调试语句表明正在计算正确的值。

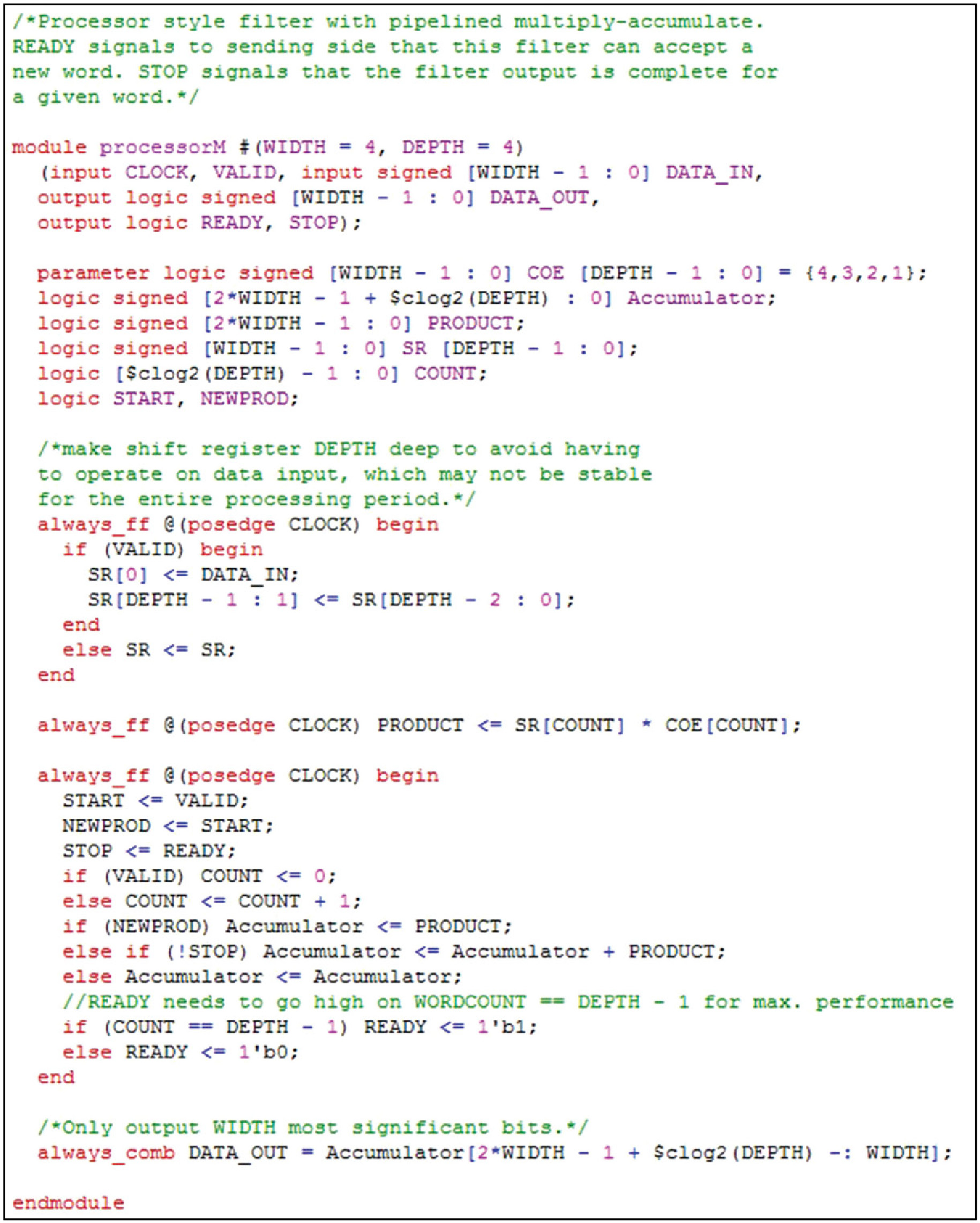

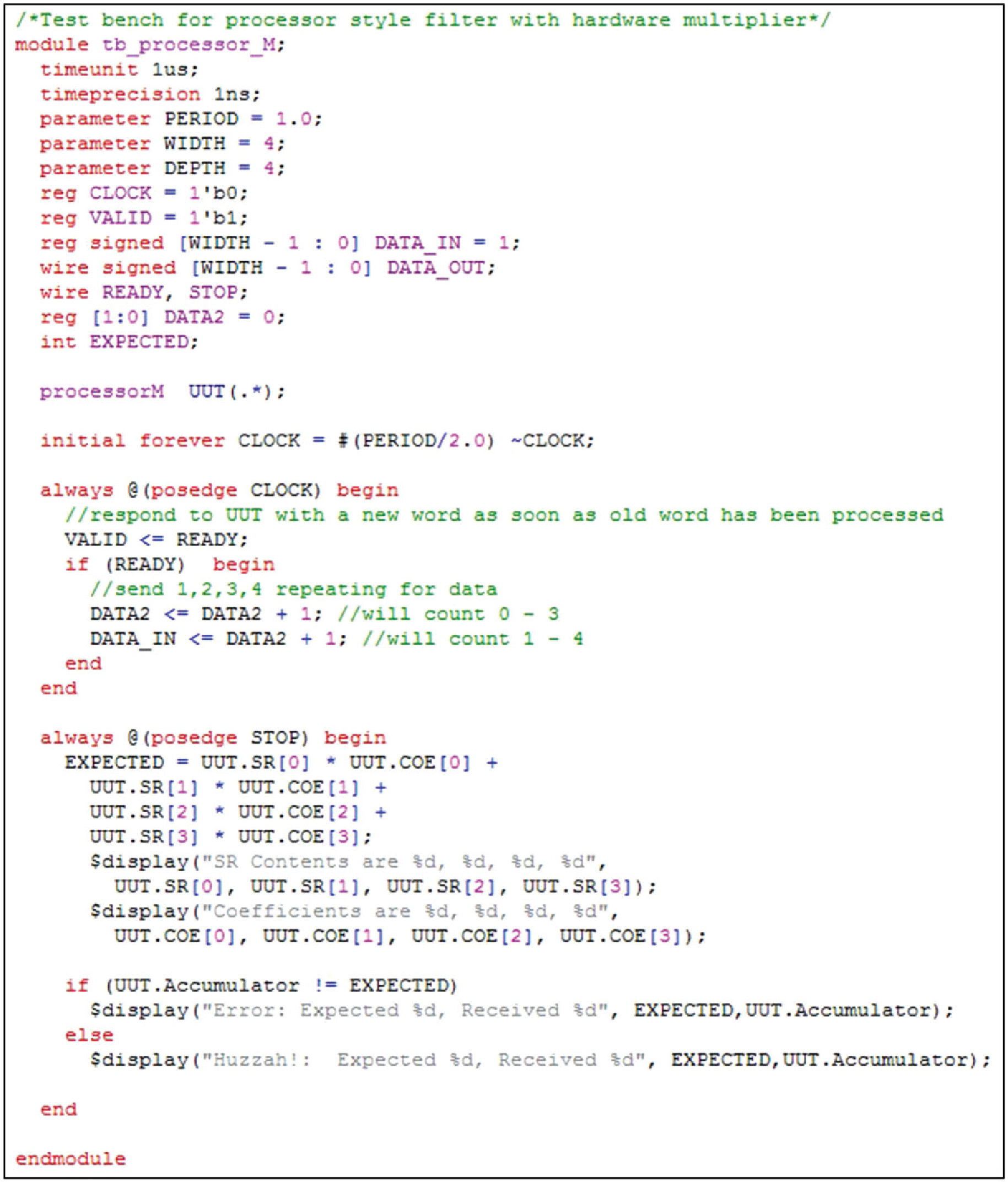

图9.15所示处理器架构的硬件乘法器滤波器的可扩展代码如图12.14所示。该设计每个数据字需要 DEPTH 个时钟周期进行处理。其测试装置如图12.15所示。

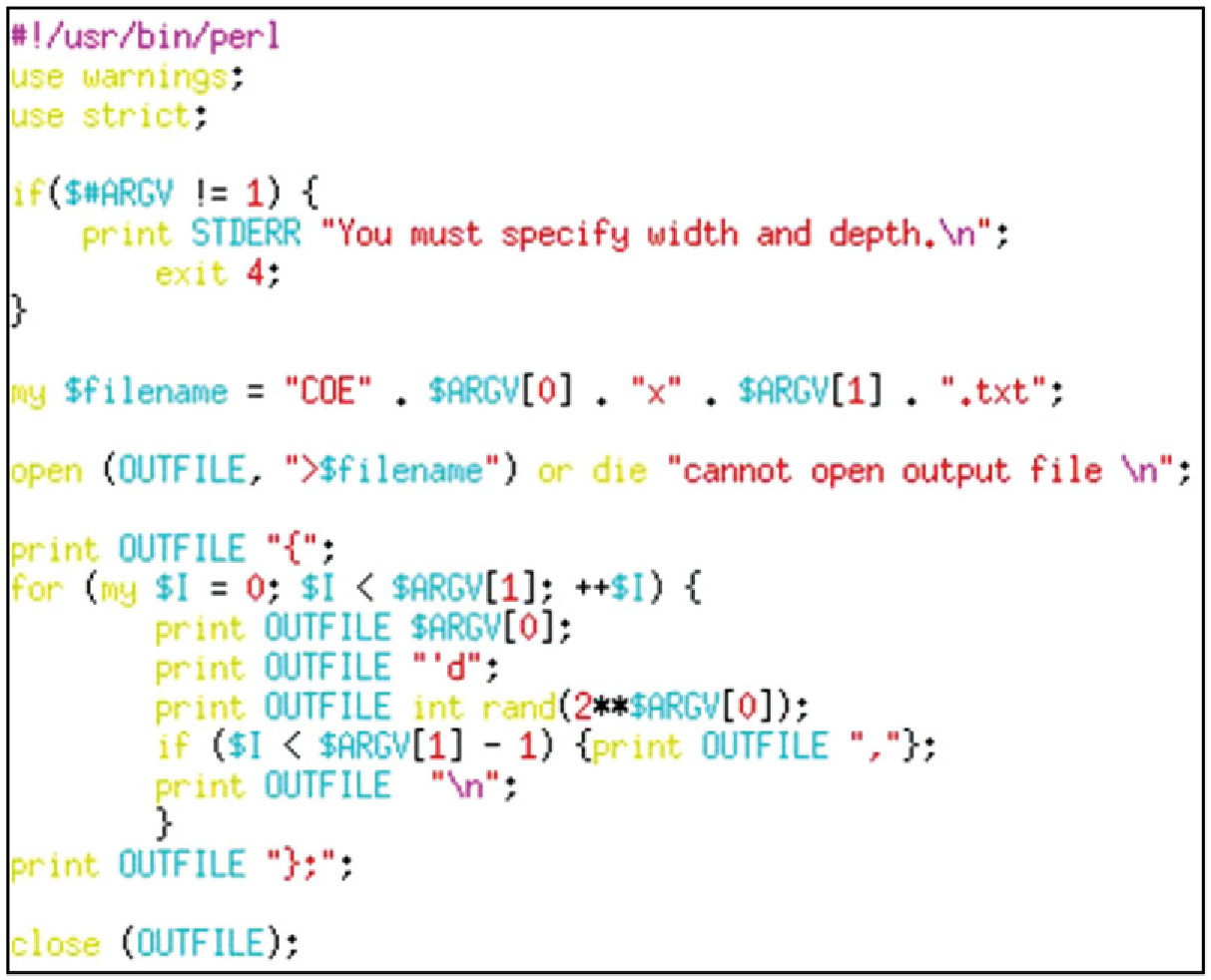

在数据采集中,使用了具有不同滤波器宽度和深度的伪随机滤波器系数。用于生成系数的Perl脚本如图12.16所示。虽然Perl不是Verilog的一部分,但许多ASIC工程师发现使用它来生成代码以及解析计算机生成的输出(例如综合报告)是一种便捷的方法。

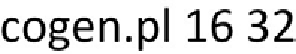

调用时需要提供两个参数,宽度和深度。这些数值将用于创建一个名为COEWxD.txt的文本文件,其中W是第一个参数,D是第二个参数。如果该文件保存为cogen.pl,则以下命令将生成一个名为COE16x32.txt的文件。

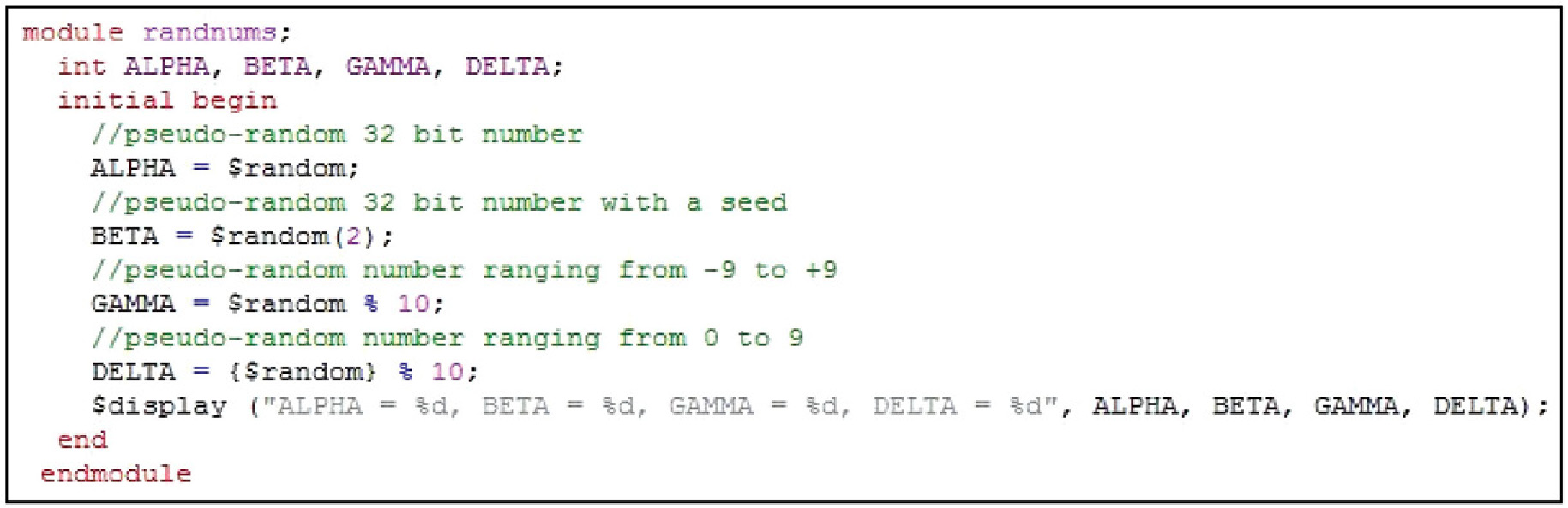

Verilog 具有内置伪随机数生成器 $random,可用于替代 图12.16 中的 Perl脚本。图12.17 展示了使用该内置生成器的四种不同选项。ALPHA 将是一个有符号的 32 位数量。BETA 也将是一个有符号的 32 位数量,但它被赋予了一个初始种子值,因此序列将是确定性的。每次运行时都会产生相同的序列。GAMMA 使用取模运算符将生成的数字范围限制在 −9到 +9。DELTA 使用拼接操作符强制生成的数字为无符号数,从而将范围有效缩小至 0–9。

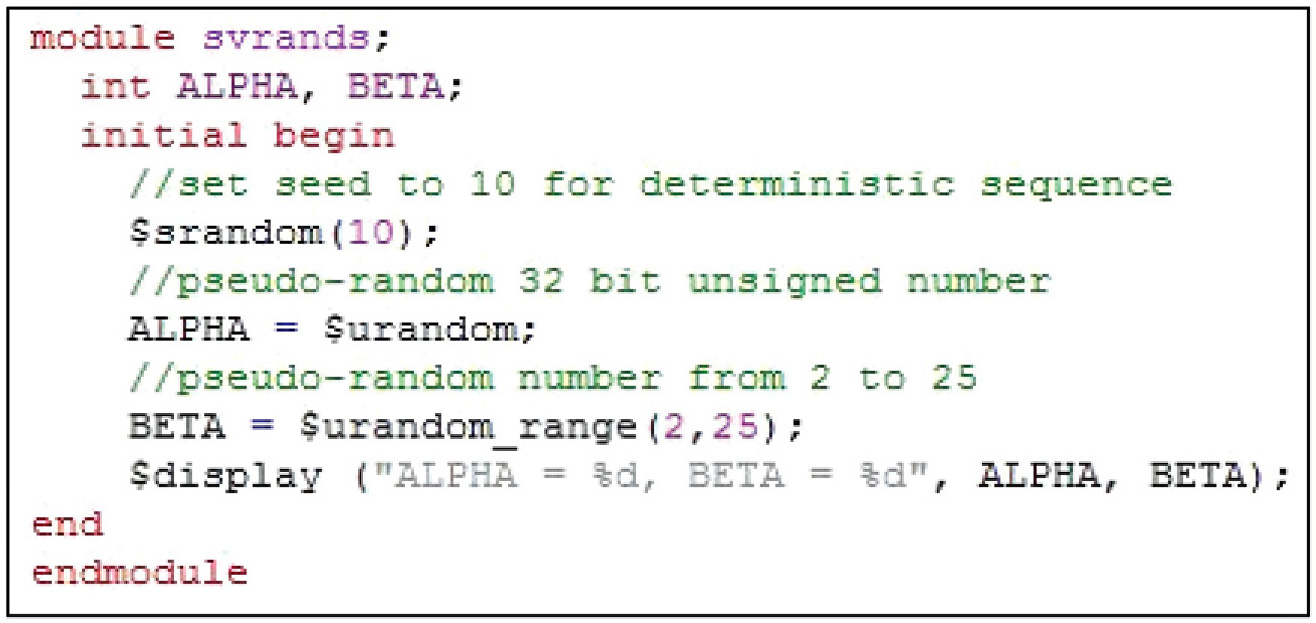

SystemVerilog 扩展了伪随机数生成功能,新增了任务 $urandom,用于生成无符号数,以及 $urandom_range(X,Y),用于在 X 和 Y 之间(包含端点)生成一个无符号伪随机数。$urandom 和 $urandom_range 均可与 SystemVerilog 的种子任务 $srandom 配合使用。$random、$urandom 和 $urandom_range 的示例如 图12.18 所示。如果 $urandom_range 只使用一个参数,则另一个参数将被默认为零。

没有任何随机数任务是可综合的。

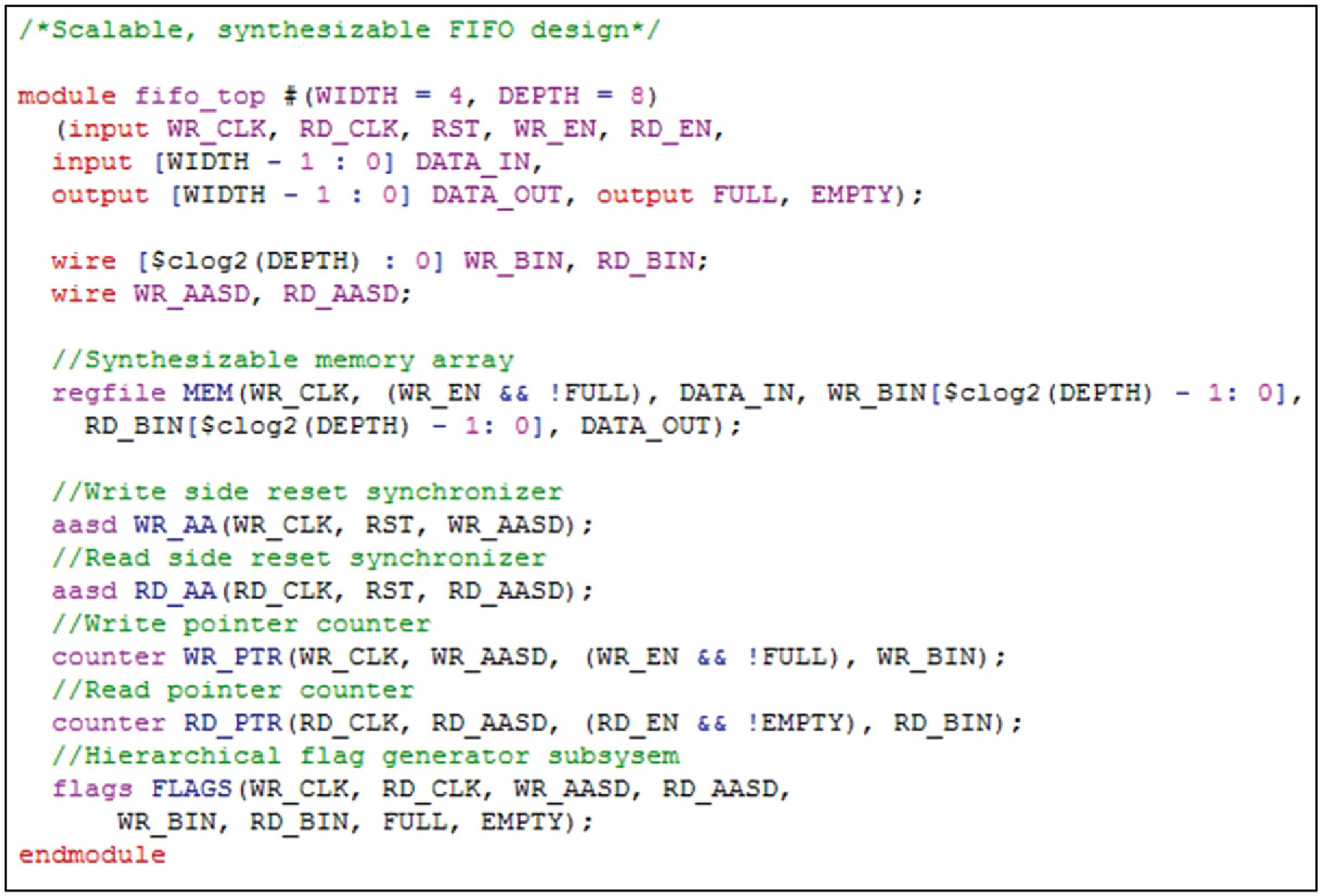

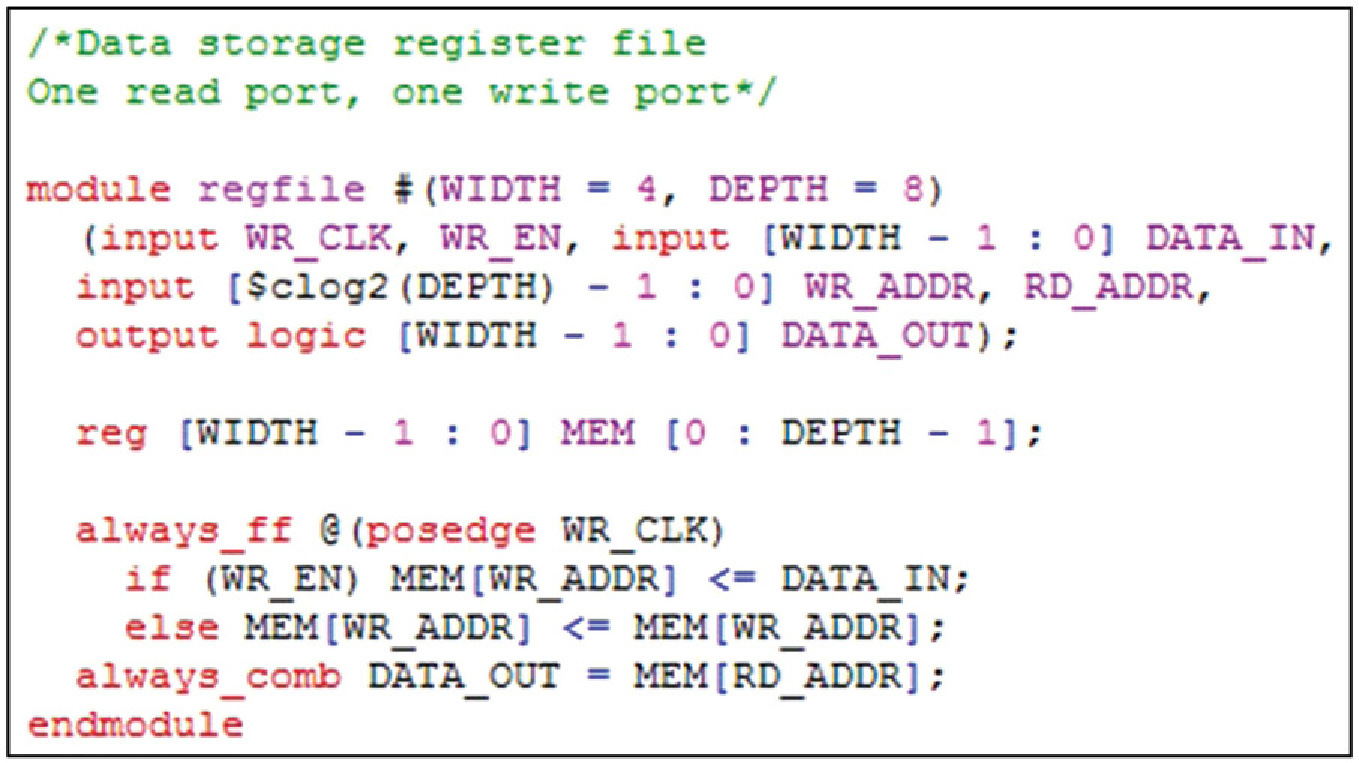

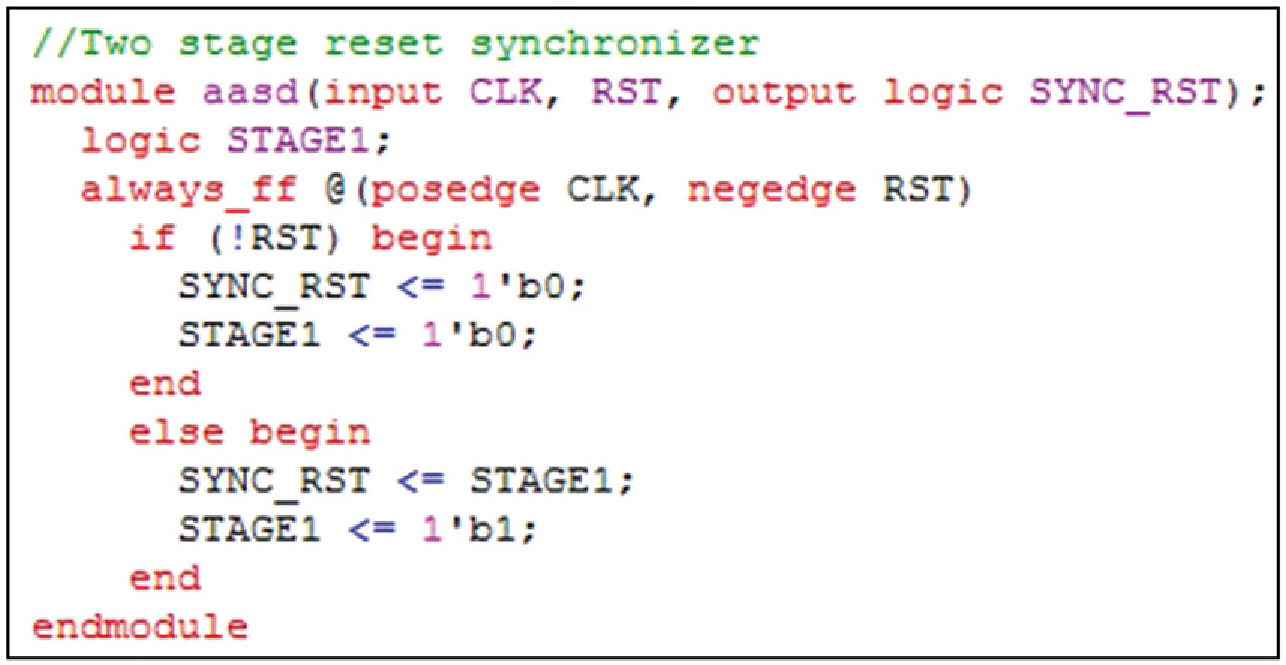

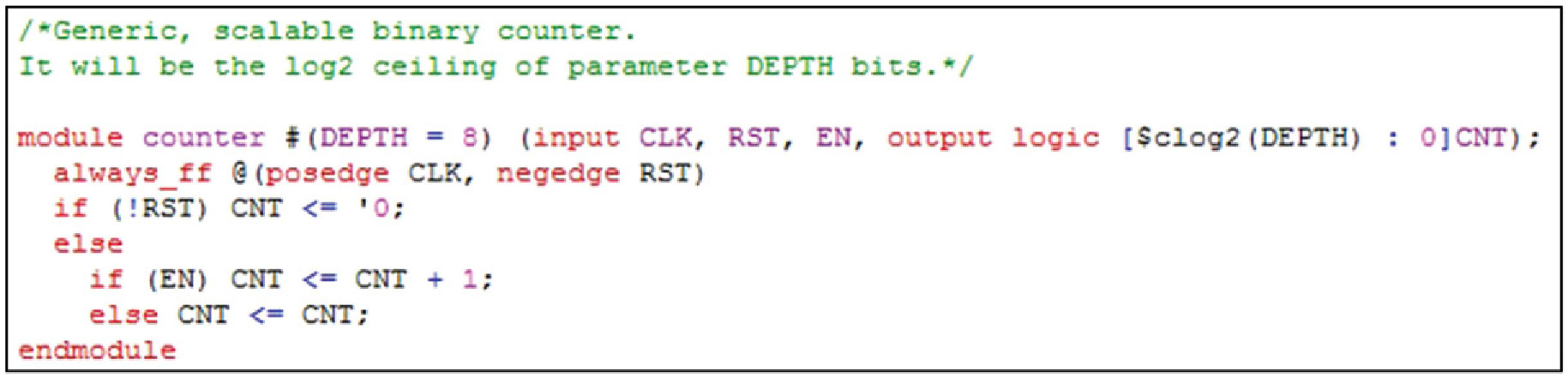

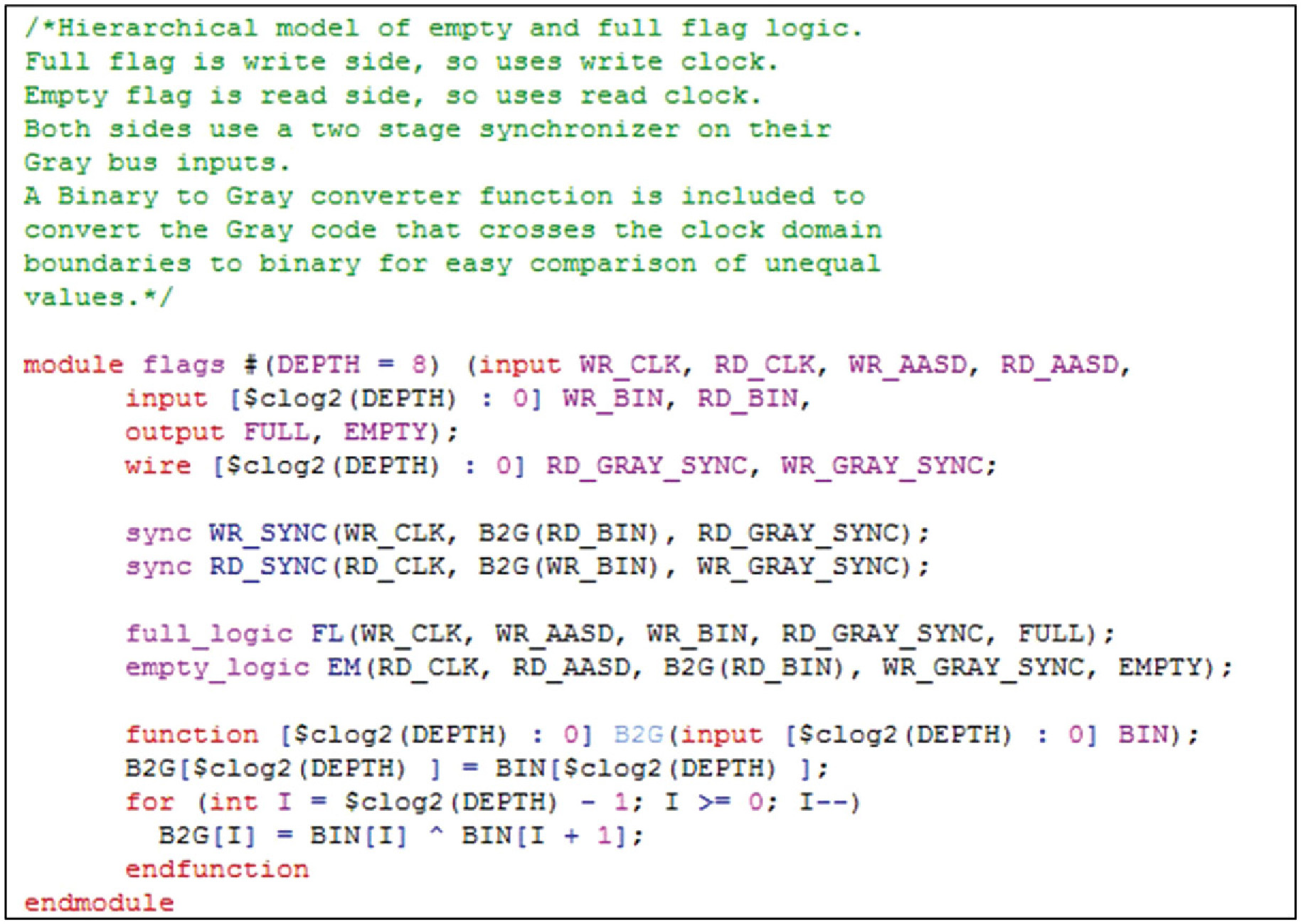

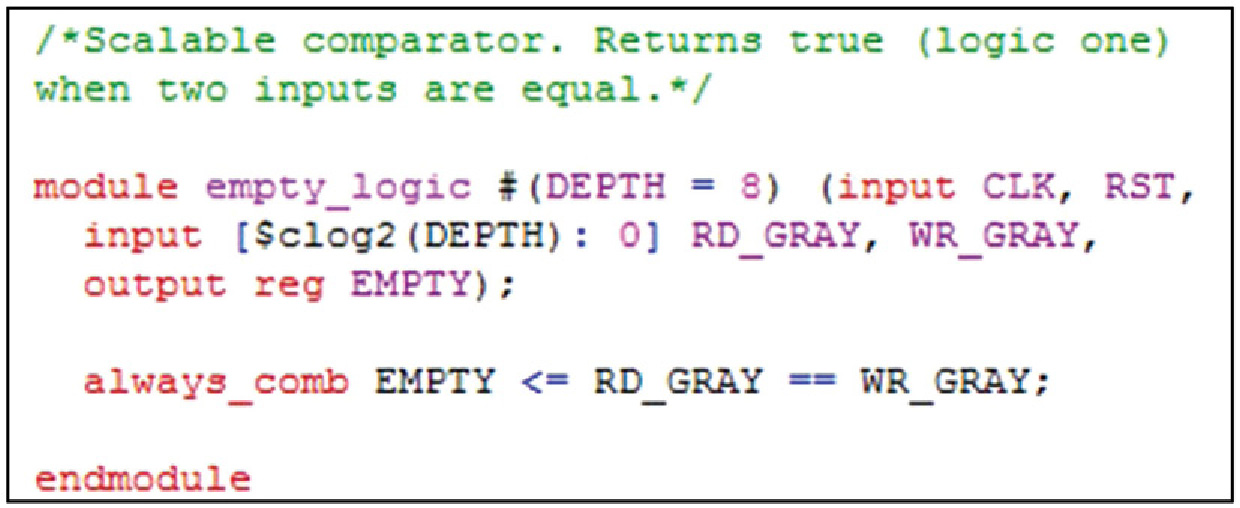

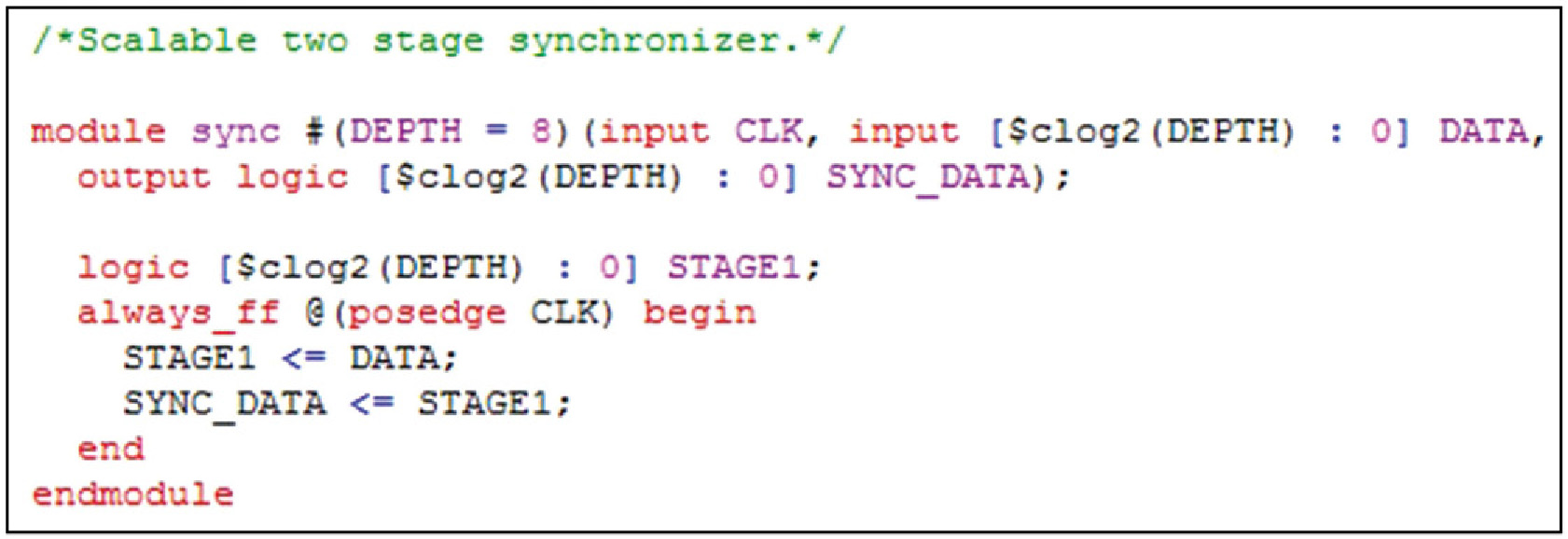

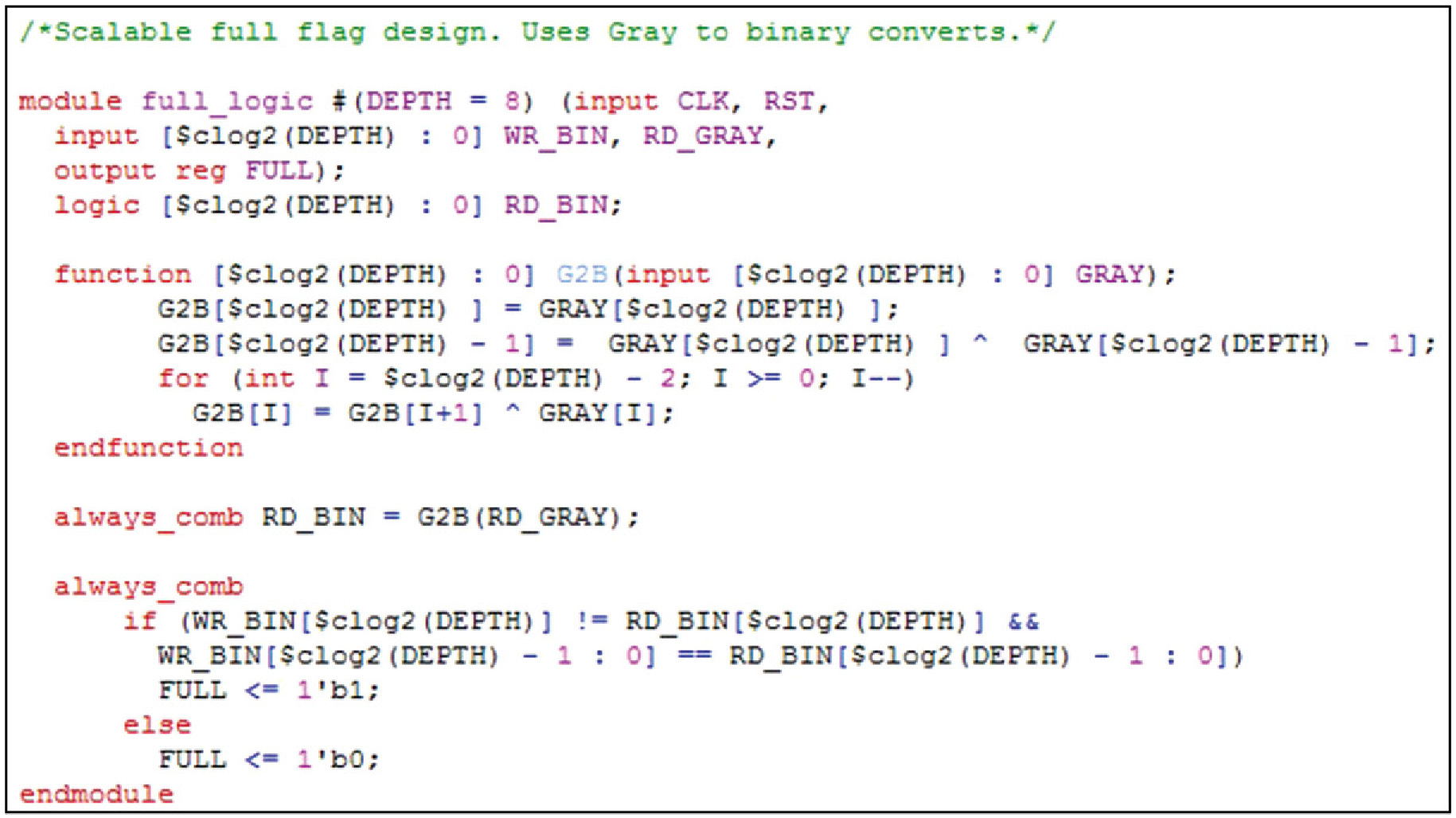

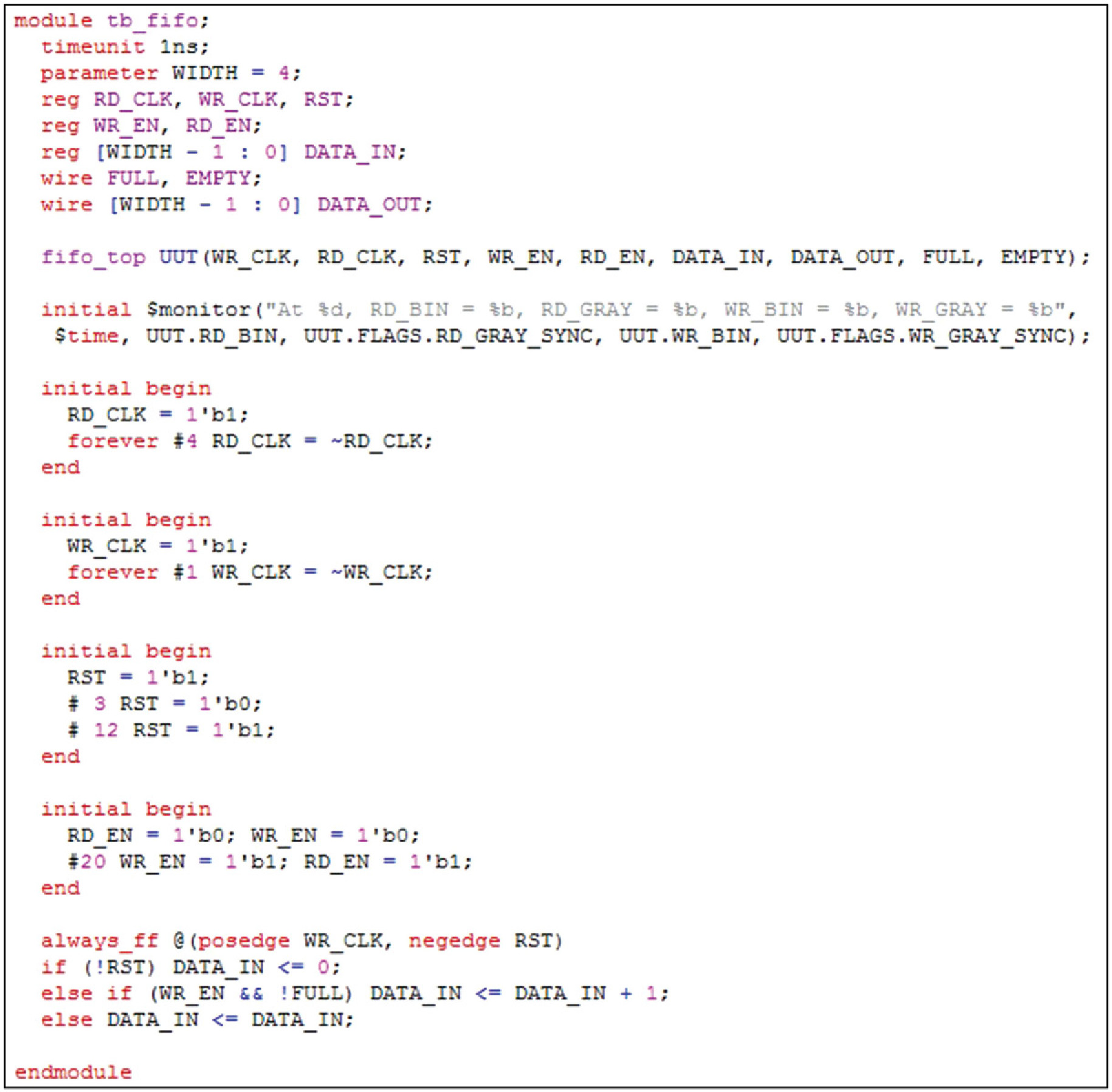

FIFO

第7章中开发的FIFO的分层代码如图12.19–12.27所示。完整设计的小型测试装置如图12.28所示。

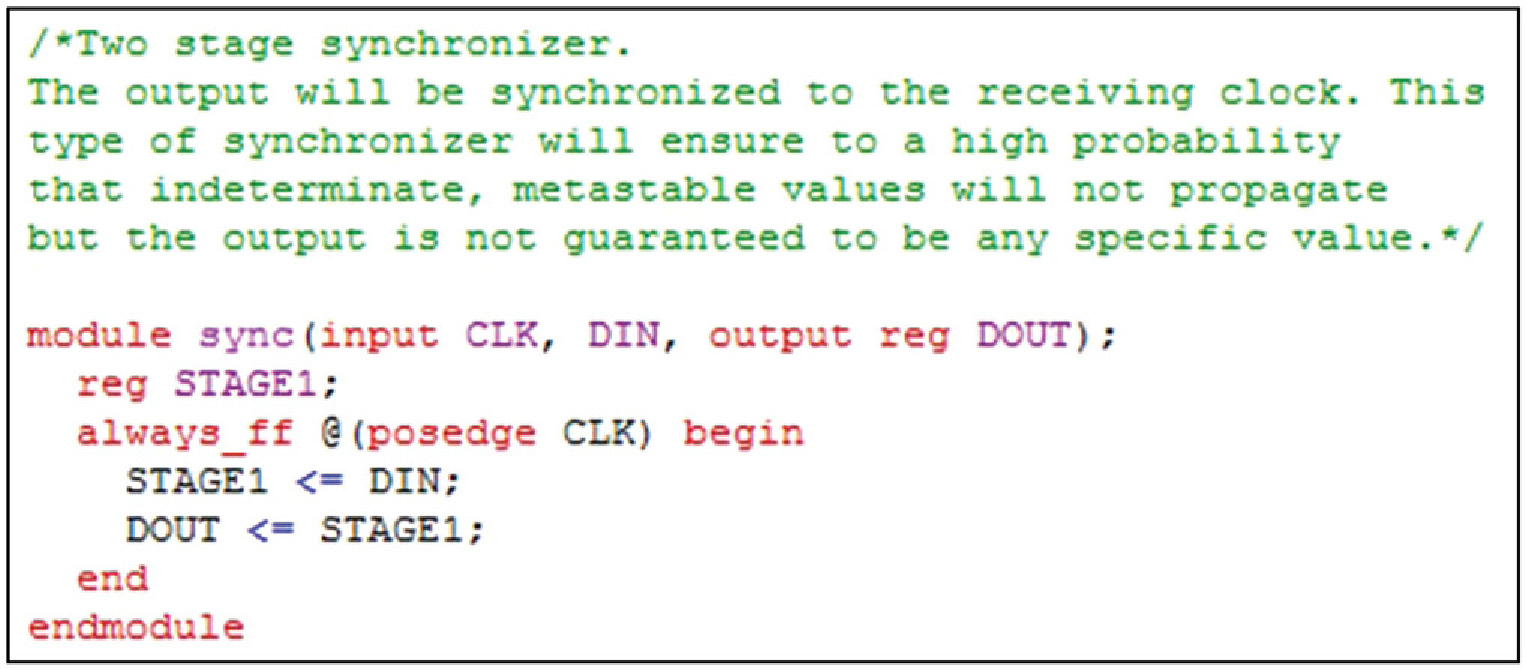

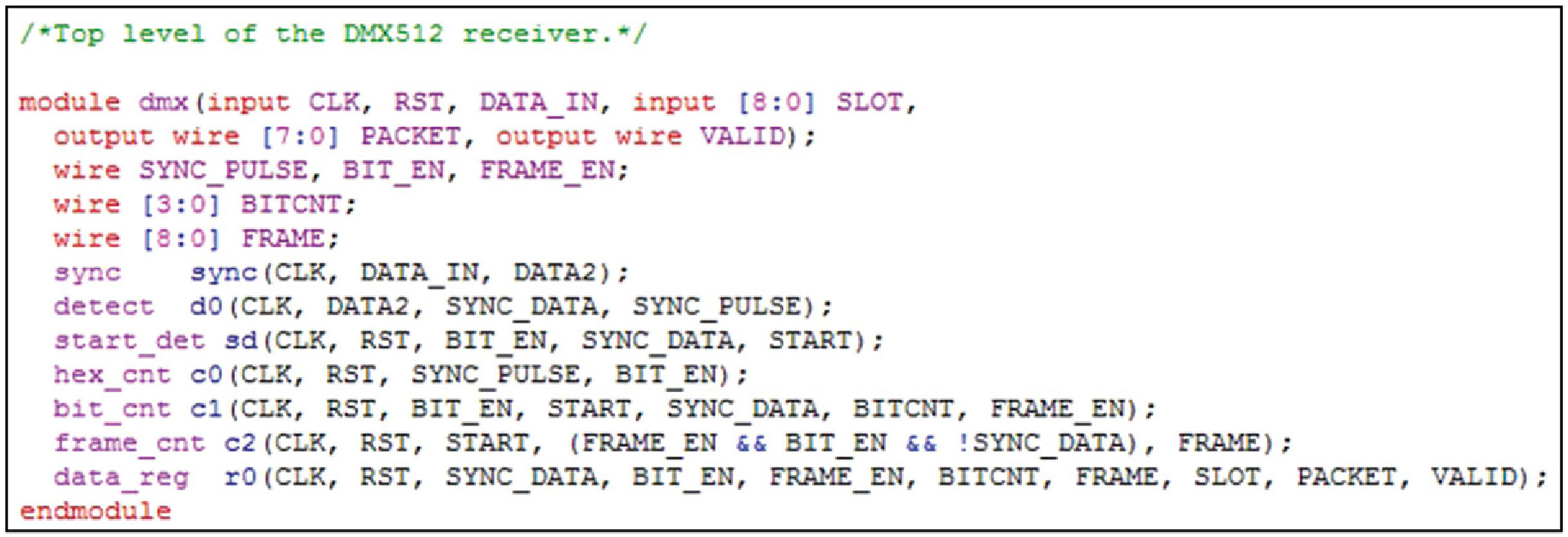

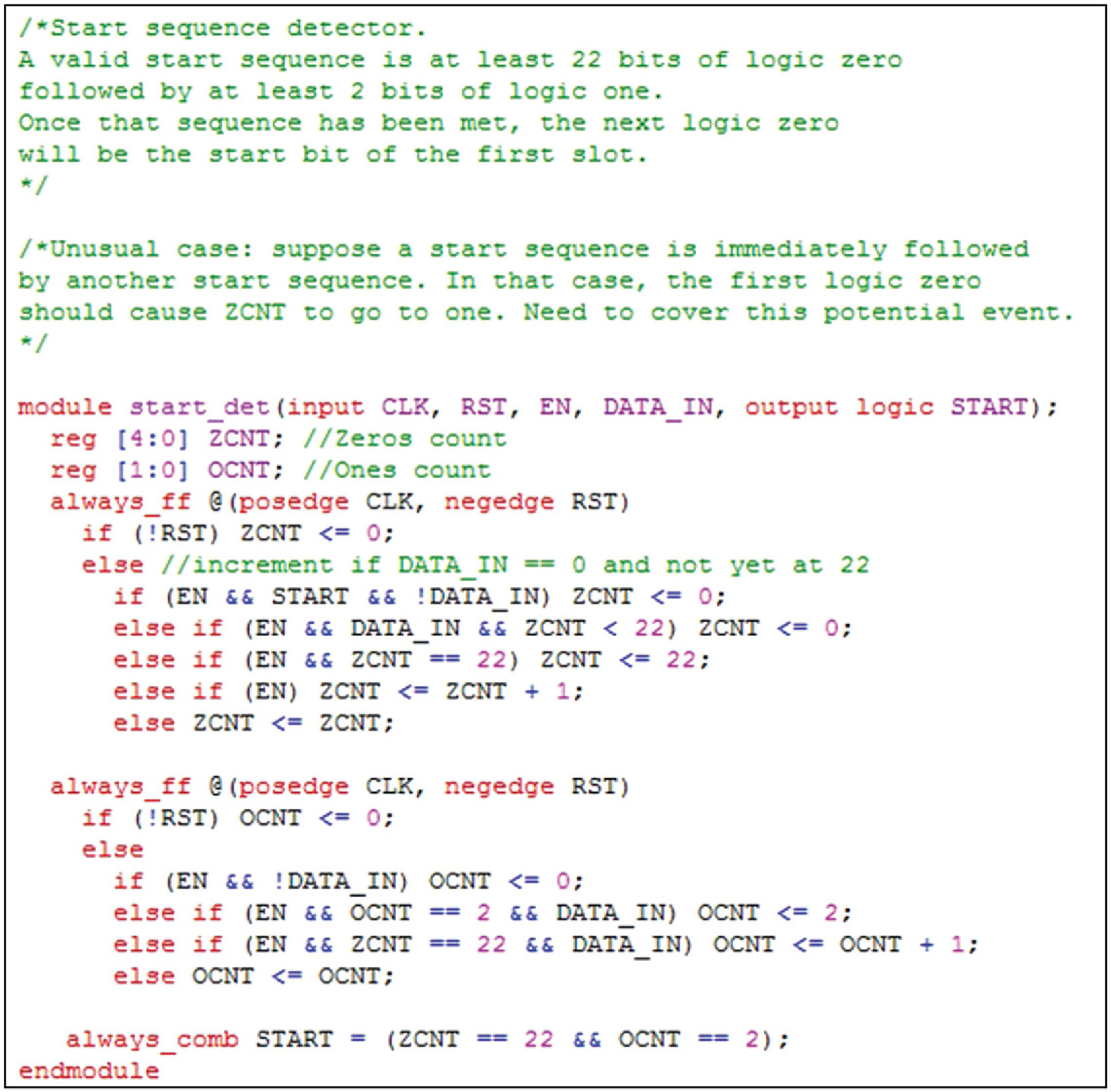

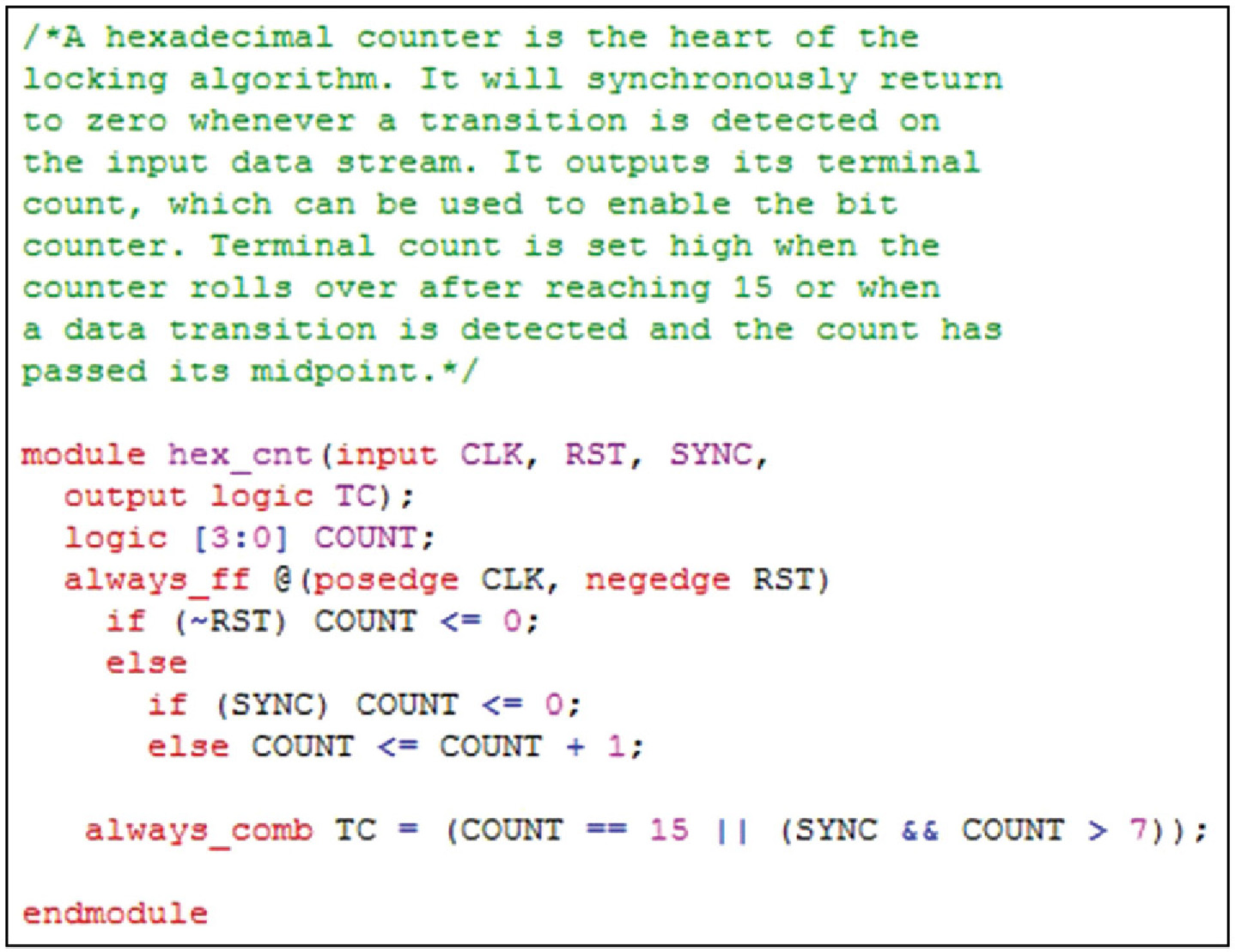

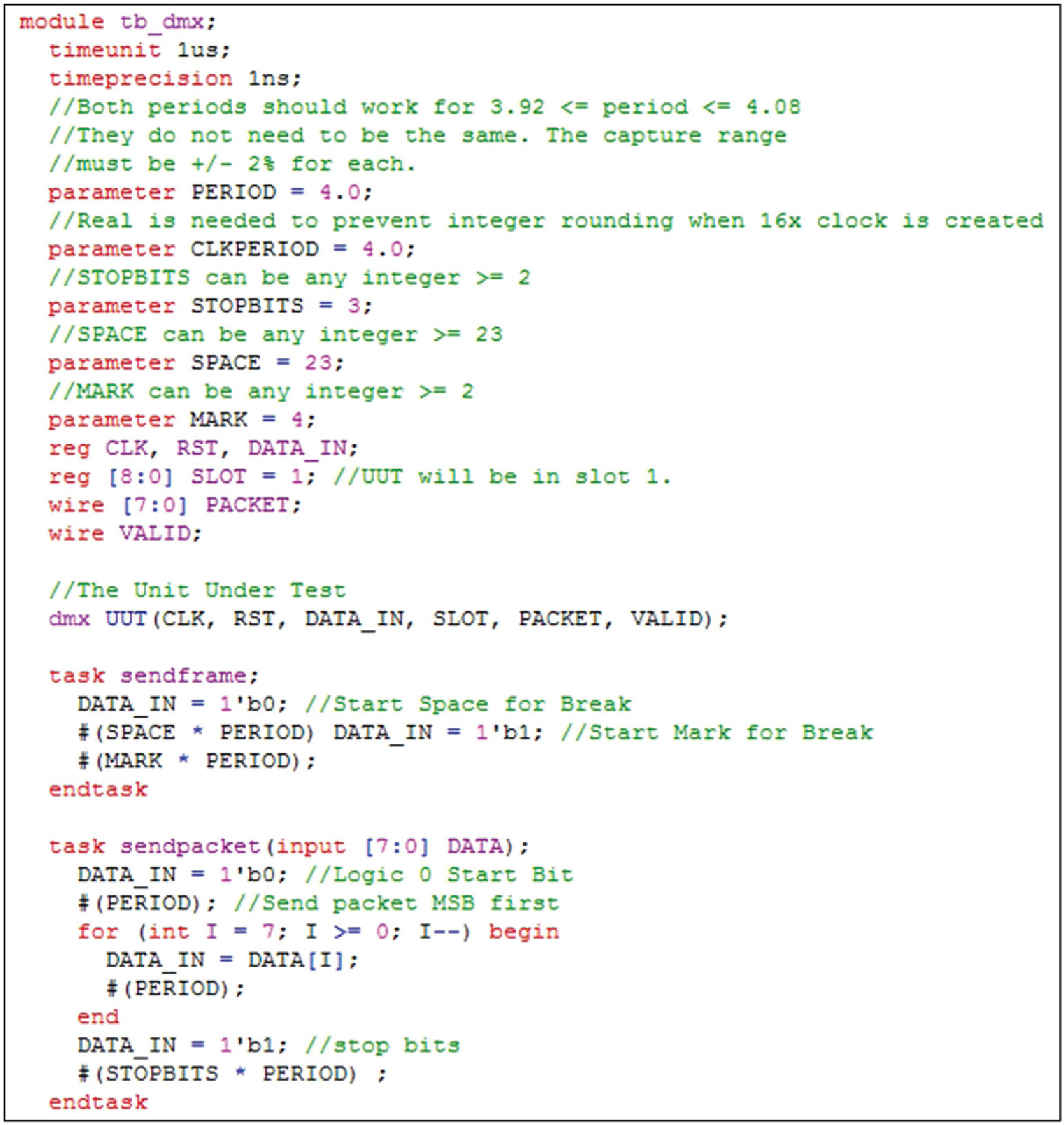

DMX接收器

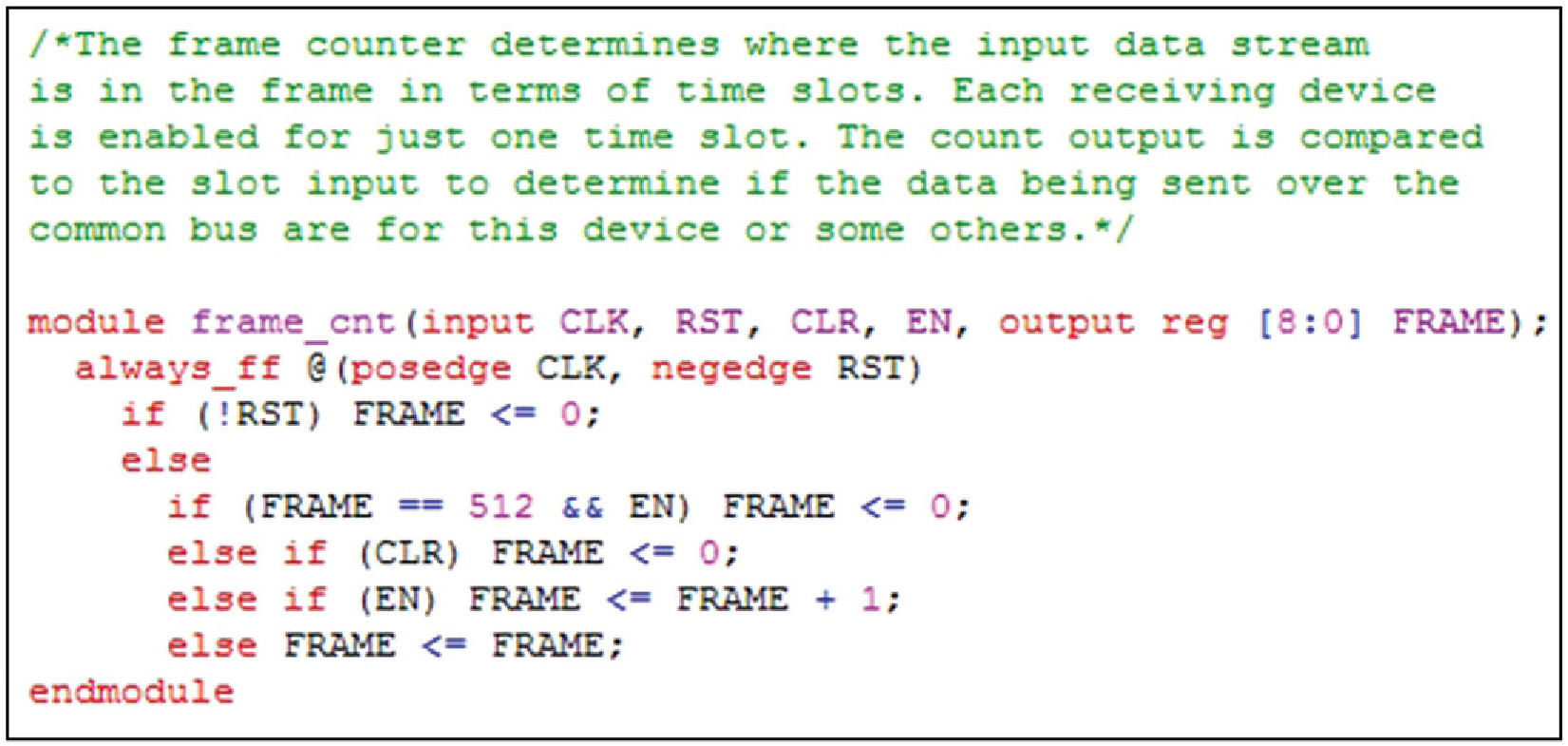

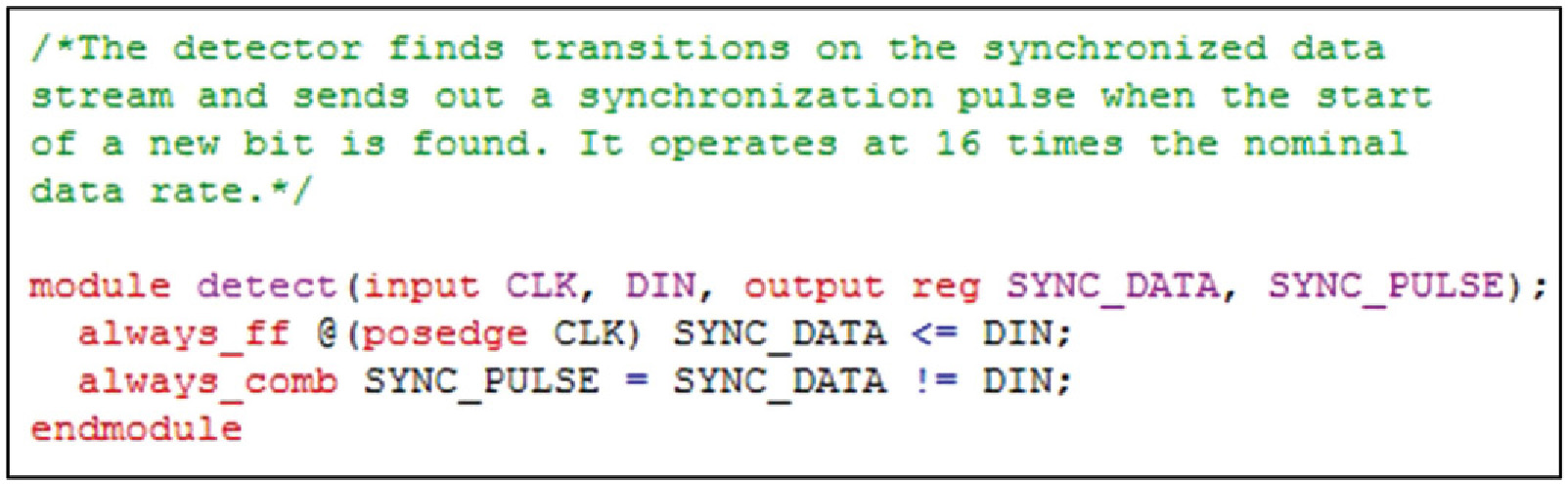

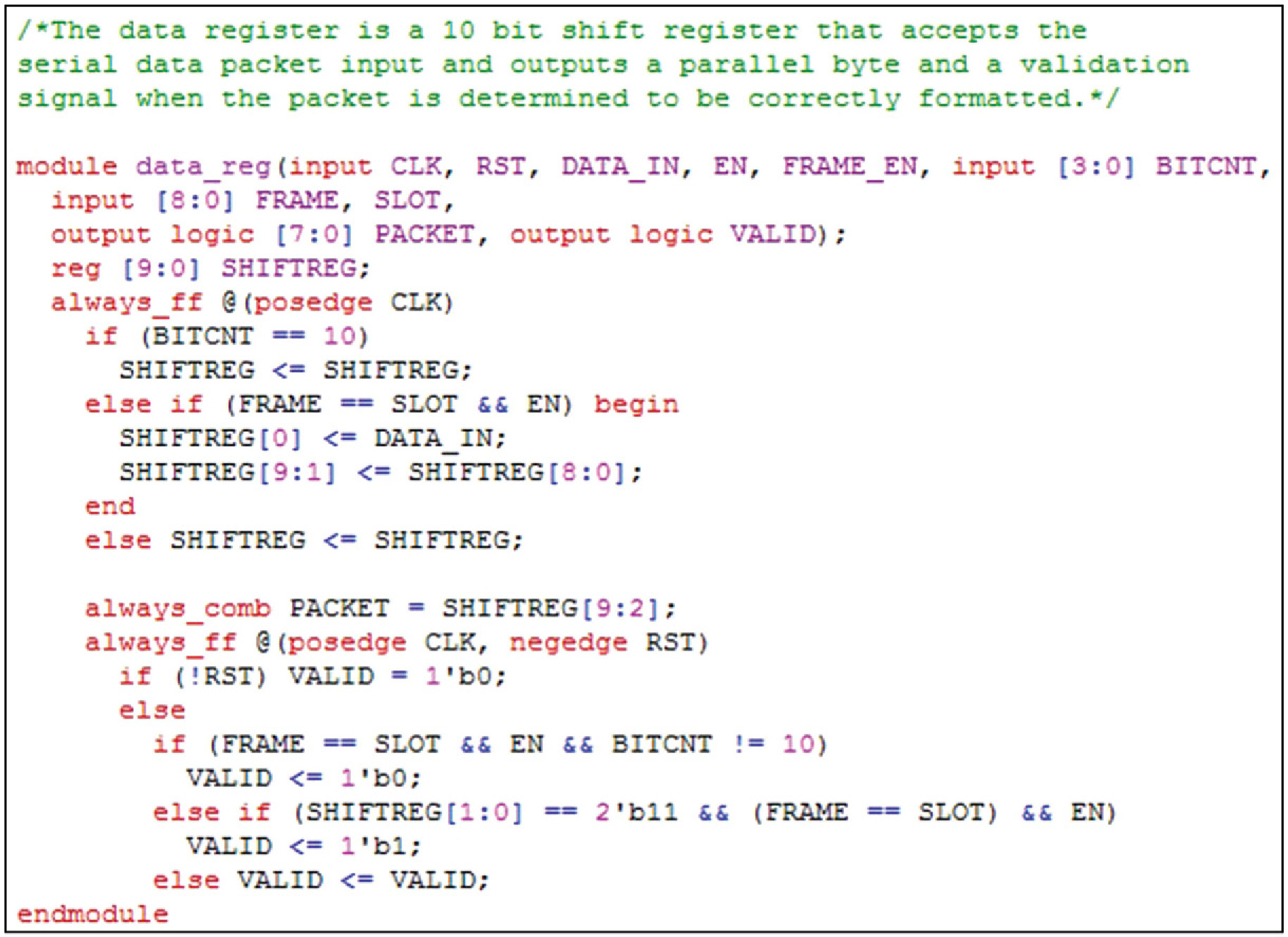

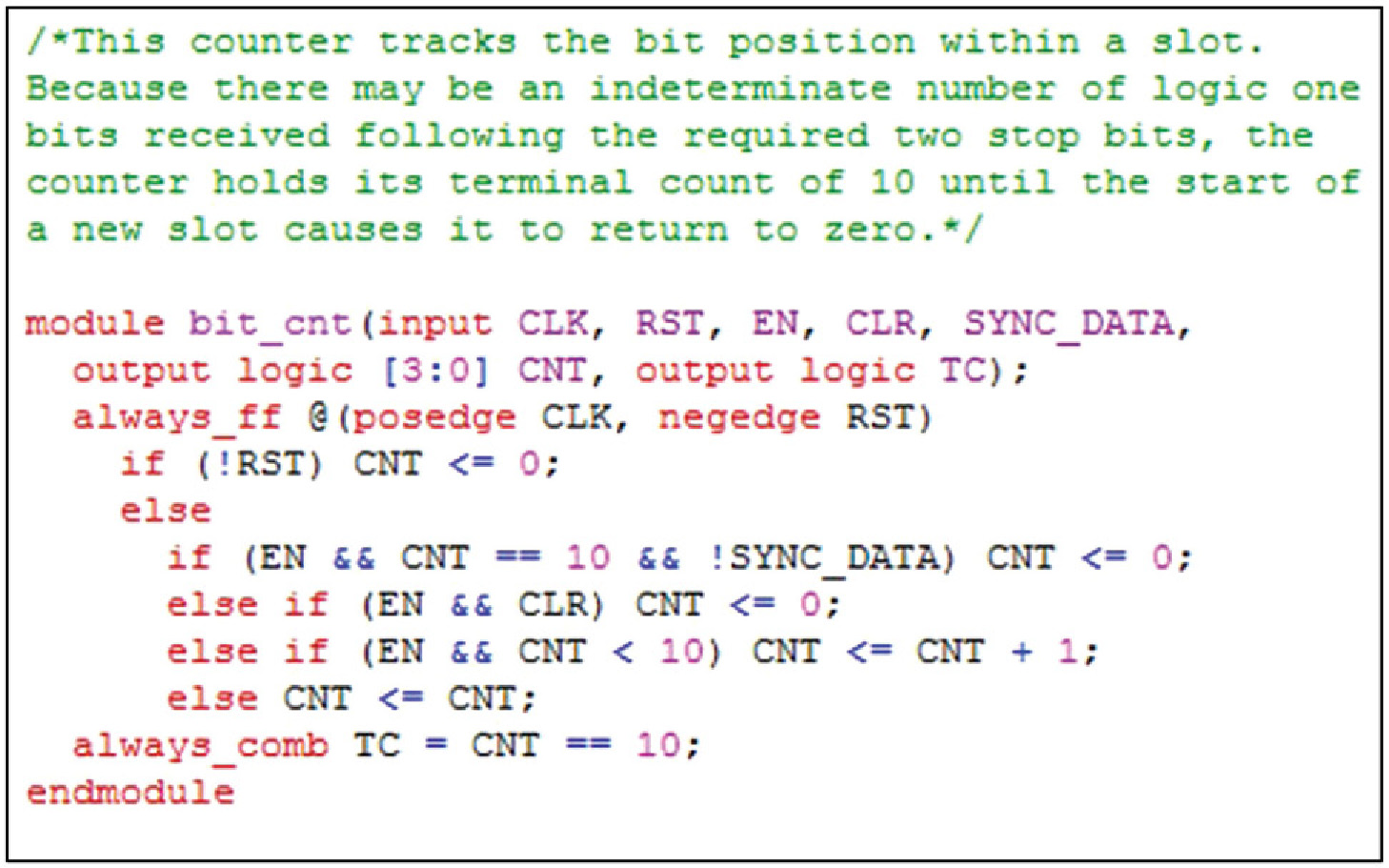

图12.28–12.37 展示了第7章中所述的DMX512接收器和测试装置的分层实现。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?