(一)驱动设计的硬件基础

一、体系结构

中央处理器的体系结构分为两类:冯诺依曼(普林斯顿)体系结构和哈佛体系结构。

-

冯诺依曼体系结构:

程序存储器和数据存储器合并在一起,程序指令存储器地址和数据存储器地址指向同一存储器的不同物理位置,

因此程序指令和数据的宽度相同。 -

哈佛体系结构:

程序指令和数据分开存储,指令和数据可以有不同的宽度。采用独立的程序总线和数据总线,分别作为CPU与每

个存储器之间的专用通信路径,具有较高执行效率。- 改进的哈佛体系结构

具有独立的地址总线和数据总线,两条总线由程序存储器和数据存储器分时复用。

- 改进的哈佛体系结构

二、数字信号处理器(DSP)

数字信号处理器(DSP)针对图像、通信、语音和视频处理等领域的算法而设计。其包含独立的硬件乘法器。DSP的

乘法指令一般在单周期内完成,且优化了卷积、数字滤波、快速傅里叶变换(FFT)、相关矩阵运算等算法中的大量

重复乘法。

DSP分为两大类:

- 定点DSP:只能用于定点运算模拟浮点运算。

- 浮点DSP:用硬件实现,可在单周期内完成。其浮点运算能力高于定点DSP。

三、存储器

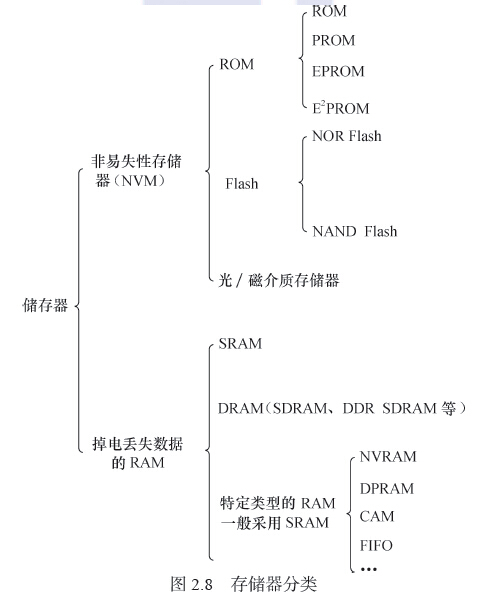

存储器主要分为只读存储器(ROM)、闪存(Flash)、随机存取存储器(RAM)、光/磁介质存储器。

ROM

- 不可编程ROM

- 可编程ROM(PROM)

- 可擦除可编程ROM(ERPOM)

- 电可擦除可编程ROM(EEPROM):完全用软件擦写。

Flash

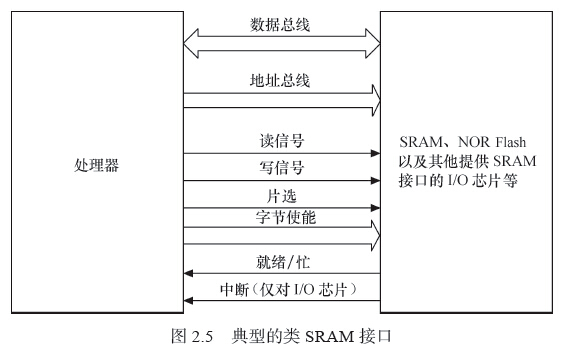

-NOR(或非)Flash

与CPU采用典型的类SRAM接口,无需增加额外控制电路。可芯片内执行(eXecute In Place, XIP),程序可以直接在

NOR Flash中运行。

-NAND(与非)Flash

与CPU的接口必须由相应的控制电路进行转换,也可以通过地址线或GPIO产生的NAND Flash信号。NAND Flash以块

方式进行访问,不支持芯片内执行。

公共闪存接口(Common Flash Interface, CFI)是一个从NOR Flash器件中读取数据的公开、标准接口。它可以使系

统软件查询已安装的Flash器件的各种参数,包括器件阵列结构参数、电气和时间参数以及器件支持的功能等。如果芯片

不支持CFI,就需使用JEDEC(Joint Electron Device Engineering Council,电子电器设备联合会)了。JEDEC规范的NOR

则无法直接通过命令来读出容量等信息,需要读出制造商ID和设备ID,以确定Flash的大小。

与NOR Flash的类SRAM接口不同,一个NAND Flash的接口主要包含如下信号。

-

I/O总线:地址、指令和数据通过这组总线传输,一般为8位或16位。

-

芯片启动(Chip Enable,CE#):如果没有检测到CE信号,NAND器件就保持待机模式,不对任何控制信号做出响应。

-

写使能(Write Enable,WE#):WE#负责将数据、地址或指令写入NAND之中。

-

读使能(Read Enable,RE#):RE#允许数据输出。

-

指令锁存使能(Command Latch Enable,CLE):当CLE为高电平时,在WE#信号的上升沿,指令将被锁存到NAND指令寄存器中。

-

地址锁存使能(Address Latch Enable,ALE):当ALE为高电平时,在WE#信号的上升沿,地址将被锁存到NAND地址寄存器中。

-

就绪/忙(Ready/Busy,R/B#):如果NAND器件忙,R/B#信号将变为低电平。该信号是漏极开路,需要采用上拉电阻。

NAND Flash较NOR Flash容量大,价格低;NAND Flash中每个块的最大擦写次数是100万次,而NOR的擦写次数是10万次;

NAND Flash的擦除、编程速度远超过NOR Flash。由于Flash固有的电器特性,在读写数据过程中,偶然会产生1位或几位

数据错误,即位反转,NAND Flash发生位反转的概率要远大于NOR Flash。位反转无法避免,因此,使用NAND Flash的同时,

应采用错误探测/错误更正(EDC/ECC)算法。

Flash的编程原理都是只能将1写为0,而不能将0写为1。因此在Flash编程之前,必须将对应的块擦除,而擦除的过程就是把

所有位都写为1的过程,块内的所有字节变为0xFF。另外,Flash还存在一个负载均衡的问题,不能老是在同一块位置进行

擦除和写的动作,这样容易导致坏块。

IDE(Integrated Drive Electronics)接口可连接硬盘控制器或光驱,人们通常也把IDE接口称为ATA(Advanced Technology Attachment)

接口,固态硬盘使用的SATA(Serial ATA)接口。

RAM

RAM也可再分为静态RAM(SRAM)和动态RAM(DRAM)。

- DRAM

DRAM存储单元由1个晶体管和1个电容器组成,以电荷形式进行存储,数据存储在电容器中。由于电容器会因漏电而出现

电荷丢失,所以DRAM器件需要定期刷新。 - SRAM

SRAM是静态的,只要供电它就会保持一个值,SRAM没有刷新周期。每个SRAM存储单元由6个晶体管组成。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?