VCS仿真dump波形

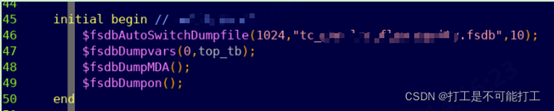

需要fsdb在.v中使用,如上图所示,下面详解各函数参数意义:

1.$fsdbDumpfile("abc.fsdb",1000):

"abc.fsdb"为波形名称,后面的数字1000就表示1000M,表示限定这个fsdb最大1000M就不dump了

2. $fsdbAutoSwitchDumpfile(200,"abc.fsdb",5):

表示dump 5个最大200M的fsdb,最后得到的应该是5个 abc***.fsdb,如不超过200M即为一个abc0.fsdb文件

3. $fsdbDumpvars

$fsdbDumpvars(1,top,"+fsdbfile+abc.fsdb"): dump top这一层到abc.fsdb这个文件里

$fsdbDumpvars(0,top.cpu,"+fsdbfile+cd.fsdb") :dump top.cpu全部到cd.fsdb里面

$fsdbDumpvars("+power") dump power相关信息,用于low power case debug

4. $fsdbDumpMDA(xx.mem)

记录二维数组mem的值,便于在verdi中查找mem内部信号,参数空缺即dump所有mem内部信号

5. $fsdbDumpflush

在仿真过程中强制将信号值加载到波形中,便于在仿真过程中查看波形

6. 指定时间dump,:

当你的pattern已经跑过一次之后,加入你只想从1ms才开始dump,

initial begin

#1000_000;

$fsdbDumpvars("aa.fsdb");

end

7. 可以在先关闭dump,#delay 多少时间之后使用打开dump命令,来断断续续的dump

$fsdbDumpon - 打开 FSDB dumping

$fsdbDumpoff - 关闭 FSDB dumping

349

349

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?