在高速 PCB(通常指信号频率≥100MHz 或传输速率≥1Gbps,如服务器 DDR5、5G 基站射频板、工业 PCIe 5.0 设备)中,阻抗控制是保障信号完整性的 “生命线”。与低速 PCB(≤50MHz)不同,高速信号在传输过程中对阻抗变化极其敏感 —— 哪怕 0.1Ω 的阻抗偏差,都可能引发信号反射、串扰加剧,导致数据传输误码率从 10⁻¹² 飙升至 10⁻⁸,甚至设备死机。若忽视阻抗控制,即便元件选型再优、布线再规整,高速信号也无法稳定传输。今天,我们从基础入手,解析高速 PCB 阻抗控制的定义、核心价值、关键阻抗类型及应用场景,帮你建立系统认知。

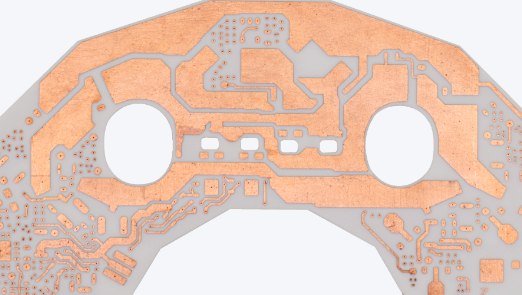

首先,明确高速 PCB 阻抗控制的核心定义:指在高速 PCB 设计与生产中,通过精准设计走线结构(线宽、间距)、叠层参数(介质厚度、介电常数)与工艺控制(蚀刻精度、铜厚均匀性),使信号传输线的阻抗值稳定在目标范围(如特性阻抗 50Ω±10%、差分阻抗 85Ω±10%),减少信号在传输过程中的反射、衰减与串扰,确保高频信号完整到达接收端。

高速 PCB 为何必须重视阻抗控制?核心原因在于高频信号的 “传输线效应”—— 当信号频率升高,走线不再是简单的 “导线”,而是兼具电阻、电容、电感的 “传输线”,信号在传输线上的行为遵循 “波传输理论”:若传输线阻抗处处一致(阻抗匹配),信号会全部被接收端吸收,无反射;若阻抗突变(如线宽突然变窄、过孔设计不当),部分信号会反射回发送端,与后续信号叠加形成 “信号过冲” 或 “振铃”,导致逻辑电平误判。例如,某 DDR5 内存 PCB 的数据线阻抗从设计的 85Ω 突变至 100Ω,反射信号导致内存读写误码率从 10⁻¹² 升至 10⁻⁷,服务器频繁蓝屏;优化阻抗后,误码率恢复正常。

高速 PCB 中需重点控制的三类核心阻抗,其定义与应用场景差异显著:

1. 特性阻抗(Z₀):单端高速信号的 “基准阻抗”

特性阻抗是单端高速信号(如射频信号、SPI 信号、低速控制信号)在传输线上的阻抗,核心参数为 “单位长度的电感与电容比值”(Z₀=√(L/C)),常见目标值为 50Ω、75Ω,需控制偏差≤±10%(高频场景≤±5%)。

-

50Ω 特性阻抗:适用于绝大多数高速数字信号(如 PCIe、Ethernet、USB 3.2)与射频信号(如 5G 基站 28GHz 射频),是行业默认的 “通用阻抗标准”——50Ω 能平衡信号衰减与功率容量,避免信号过冲过大。例如,某 5G 手机的射频走线设计为 50Ω 特性阻抗,偏差控制在 ±3%,信号接收灵敏度达 - 95dBm,比无阻抗控制的设计提升 3dB;

-

75Ω 特性阻抗:主要用于视频信号(如 HDMI 2.1、DisplayPort)与同轴电缆传输,75Ω 阻抗的信号衰减比 50Ω 低(10GHz 频段每米衰减约 0.8dB vs 1.2dB),适合长距离传输(如显示器与主机的 2 米连接线)。

2. 差分阻抗(Zdiff):高速差分信号的 “平衡阻抗”

差分阻抗是高速差分信号(如 DDR 内存、USB4、Thunderbolt)两根传输线的总阻抗,需控制为 “两倍特性阻抗” 的近似值(如 85Ω、100Ω),偏差≤±10%。差分信号通过 “两根反向传输的信号线” 抵消共模噪声(如电磁干扰),差分阻抗的平衡度直接决定抗干扰能力 —— 若两根线的阻抗偏差超 5%,共模噪声无法完全抵消,会导致信号串扰加剧。

-

85Ω 差分阻抗:专属 DDR 内存系列(DDR4、DDR5),DDR5 的时钟信号与数据信号均需 85Ω 差分阻抗,且两根线的阻抗偏差需≤±3%,否则内存带宽会从 4800Mbps 降至 4000Mbps。例如,某服务器 DDR5 内存 PCB 的差分阻抗偏差达 8%,内存测试时出现 “位错误”,调整线宽与间距后,偏差降至 2%,带宽恢复正常;

-

100Ω 差分阻抗:适用于 USB4、Thunderbolt、PCIe 5.0 等差分信号,100Ω 阻抗能平衡抗干扰能力与布线空间 ——100Ω 差分线的间距(通常 0.2-0.3mm)比 85Ω(0.15-0.2mm)大,更易布线,且共模抑制比(CMRR)≥40dB,能有效抵御工业环境的电磁干扰。

3. 共模阻抗(Zcm):差分信号的 “干扰阻抗”

共模阻抗是差分信号两根线对地的共模阻抗,需与差分阻抗匹配(通常 Zcm=2×Zdiff),偏差≤±20%。共模阻抗失衡会导致差分信号转化为共模信号,引发电磁辐射(EMI)超标 —— 例如,某工业 PCIe 5.0 设备的共模阻抗偏差达 30%,EMI 辐射值从 35dBμV/m 升至 45dBμV/m,超出 EN 55022 Class B 标准(≤40dBμV/m);调整共模阻抗后,辐射值降至 38dBμV/m。

高速 PCB 阻抗控制是 “高频信号稳定传输的前提”,需根据信号类型(单端 / 差分)选择对应阻抗目标,通过精准设计与工艺控制,避免阻抗突变与失衡。只有理解这些基础特性,才能在后续设计中精准把控,确保高速设备性能达标。

830

830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?