最近有小伙伴经常给我私信说:我该如何进大厂,需要准备些什么?我把我的经验分享给大家,同时我也总结了一份非常棒的视频资料给大家。

进 BAT 其实没有想象的那么难,但是需要认真准备,编程基础肯定是要扎实,然后并发、中间件、架构的知识需要了解了解,还有个很重要的点:就是数据结构和算法,大厂面试肯定要手撕代码的。

鉴于此,我特地给大家准备了一套非常完备的视频资料,帮助大家早日实现大厂梦,看完 100% 有收获!我还制作了一份海报,可以更加直观的看到。直接长按海报关注公众号,回复“BAT”即可领取,无套路,不用转发不用分享。

这还没完,有小伙伴就问了,这些资料都是优质资料,有没有那些面试相关的面试题总结呢?要非常全的那种,看完了视频再结合面试题复习复习,肯定效果更好。

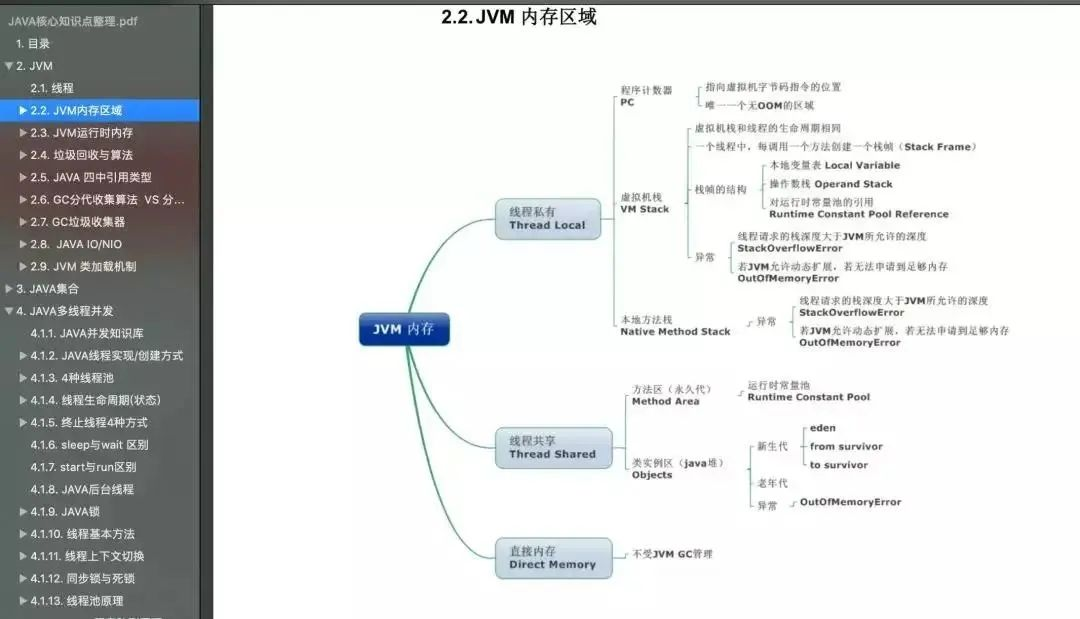

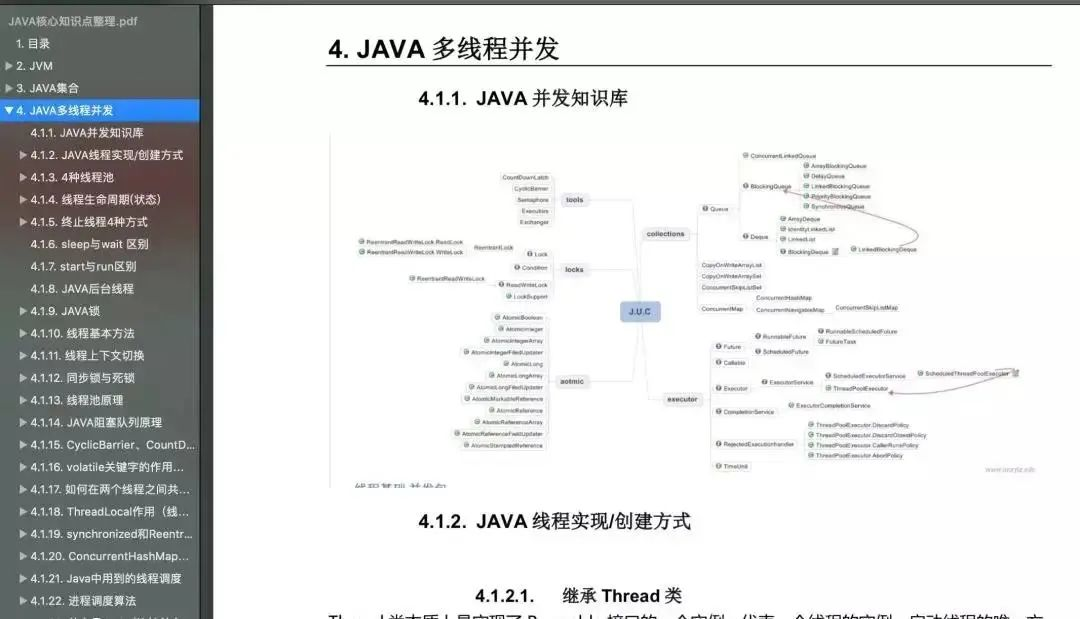

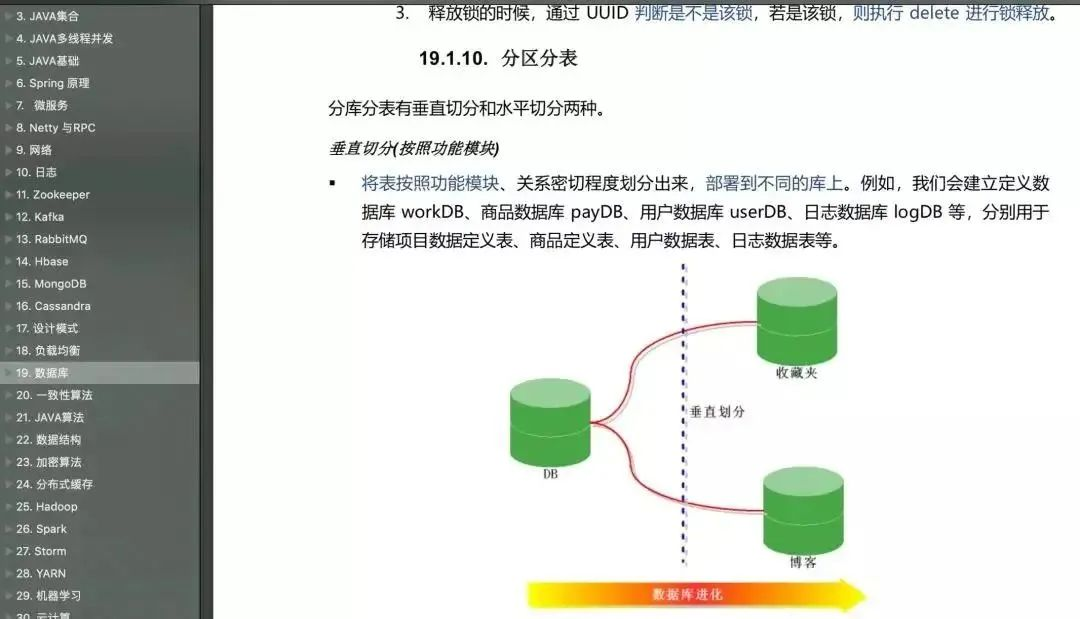

针对这些问题,我也给小伙伴们总结了一份超优质超全的最新 Java 面试题,部分截图如下:

领取方式如下:

1. 扫描下方二维码关注:Java开发宝典

2. 回复“面试题”,即可领取,无任何套路!

这些资料都是我精心挑选准备的,如果觉得对你有帮助,可以分享给更多的小伙伴,谢谢大家,祝大家每日进步一点点。

点赞是最大的支持

本文分享了进入BAT等大厂所需准备的知识点,包括编程基础、并发、中间件、架构及数据结构算法,并提供视频资料及Java面试题,助力读者实现大厂梦。

本文分享了进入BAT等大厂所需准备的知识点,包括编程基础、并发、中间件、架构及数据结构算法,并提供视频资料及Java面试题,助力读者实现大厂梦。

1061

1061

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?