目录

1.Makefile的优势

只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发的效率。

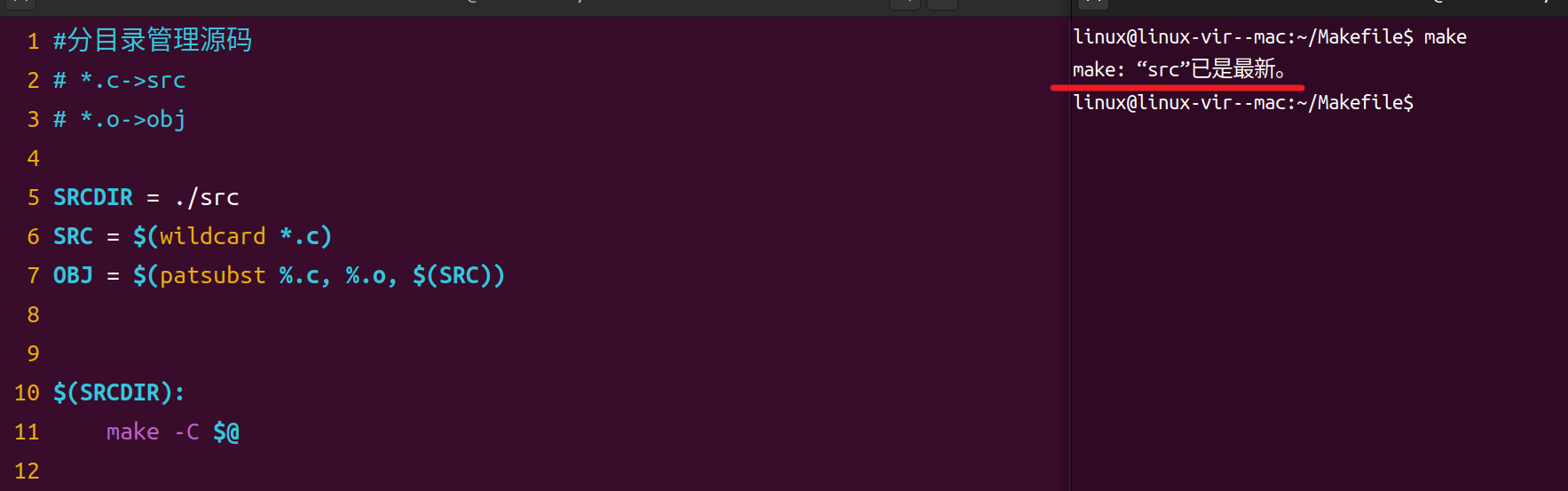

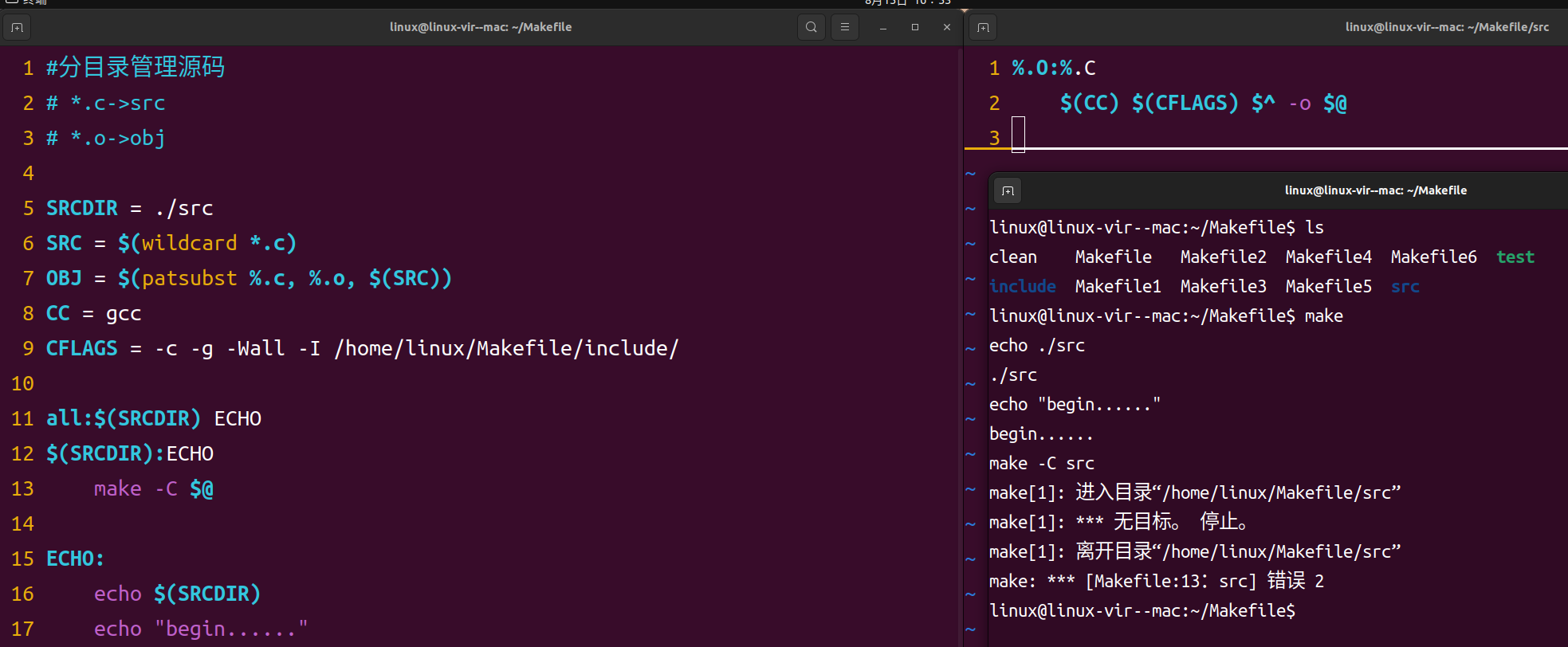

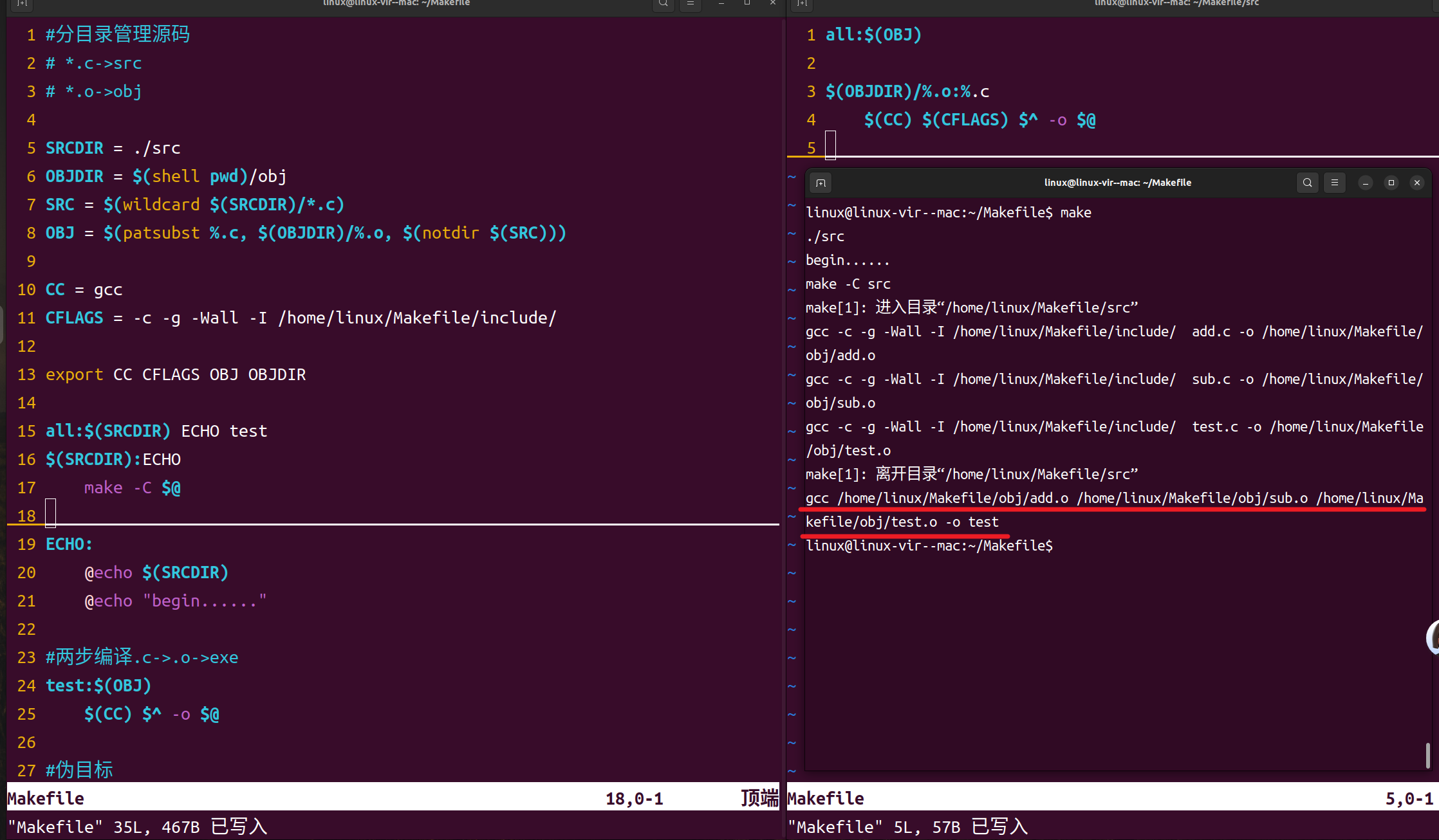

2.分目录管理源码

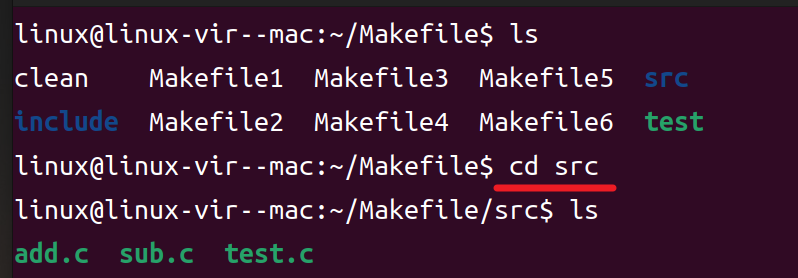

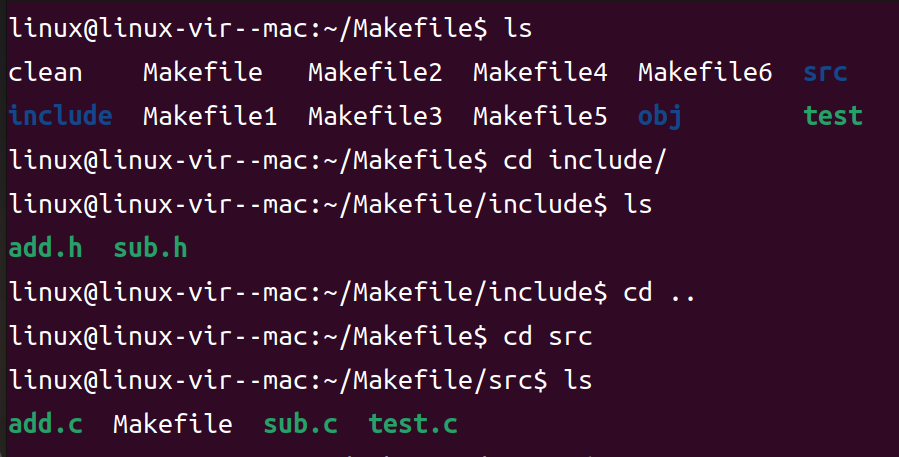

在本次项目中,我将使用src目录存放.c文件,obj目录存放生成的.o文件。我使用的是两步编译法,即.c->.o->.exe

可以看到,我已经将所有的.c文件放到了src目录里

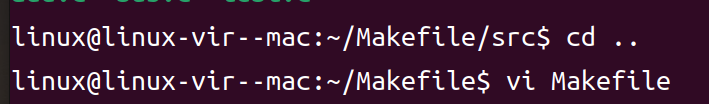

下面,开始写Makefile文件:

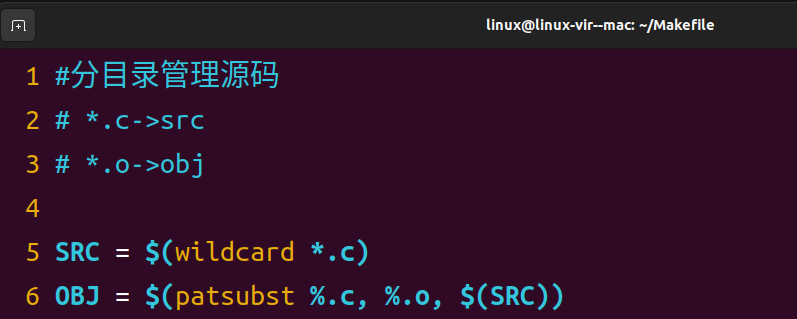

Makefile常用的函数:

$(wildcard PATTERN):列出当前目录下所有符合模式“PATTERN”格式的文件名。

$(patsubst <pattern>,<replacement>,<text>):在<text>,将<pattern>替换为<replacement>。

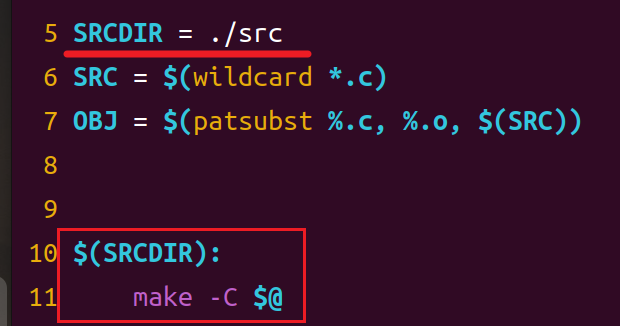

通过变量SRCDIR来存放.c文件的路径(.c文件存放在/home/linux/Makefile/src),我们只需要使用变量就可以,方便后期涉及多个目录时只改变变量内容,而不是进行大规模代码变动。

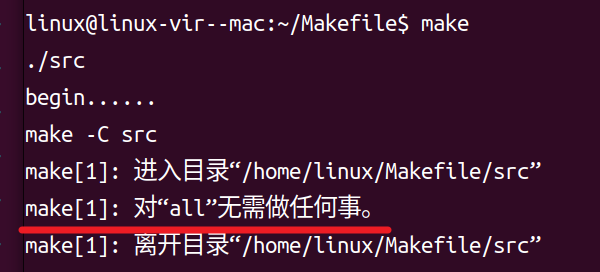

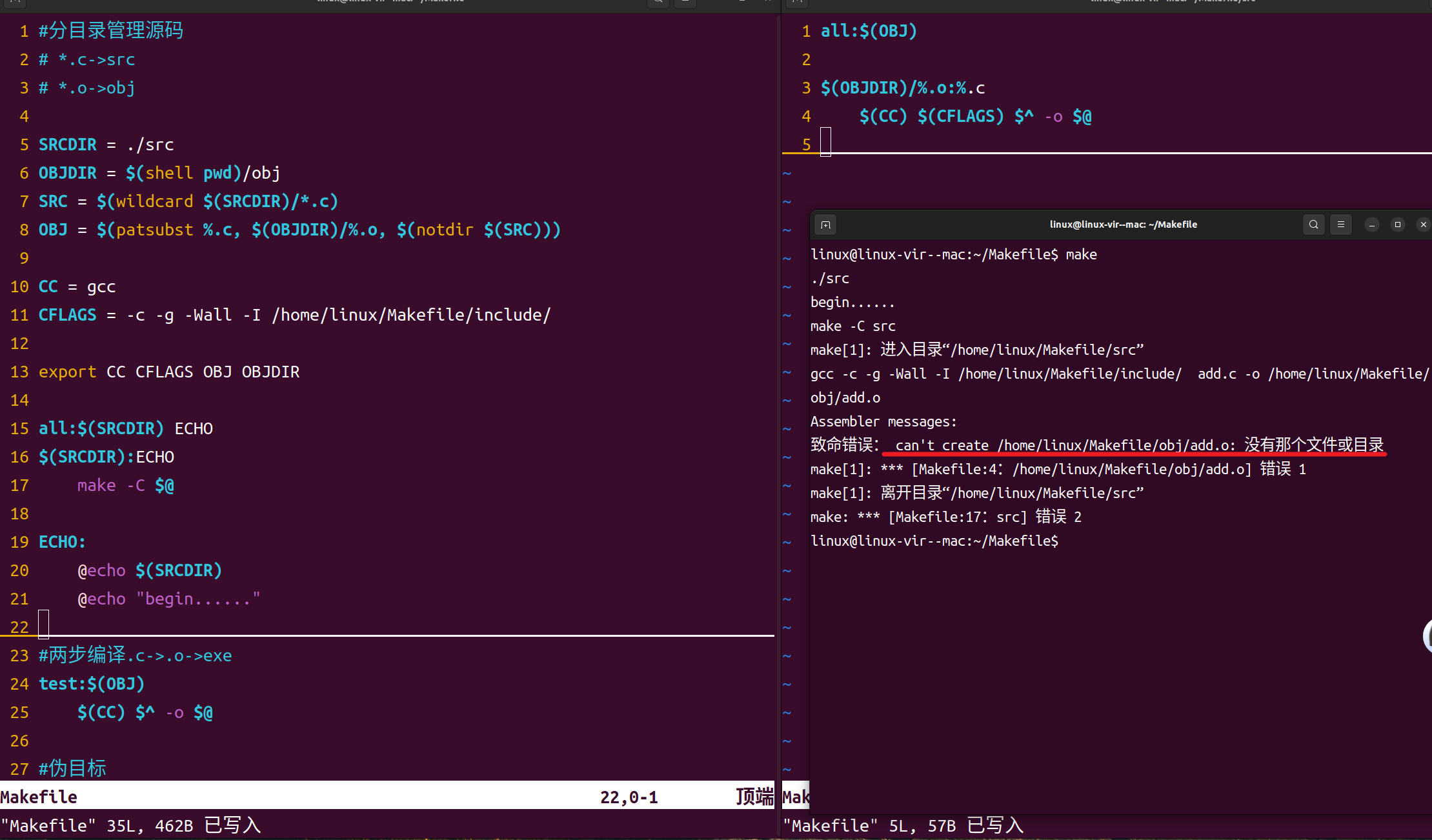

写到这,在Makefile文件中打开另外一个目录下的Makefile结构就大体成型了,主要使用的就是make -C 目录

问题1:

因为这个目录并不是我们真实的目标,因此会出现这种问题,如何解决?

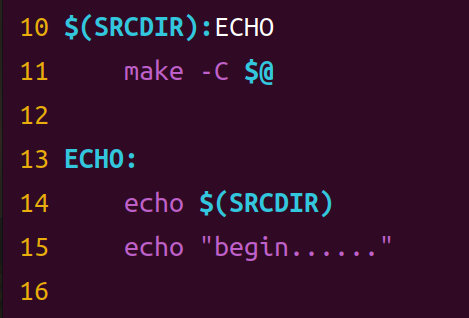

加入依赖,ECHO,让这段代码“有事做”,通过ECHO打印出所在路径以及begin提示,我们可以看到代码进行到了哪里。

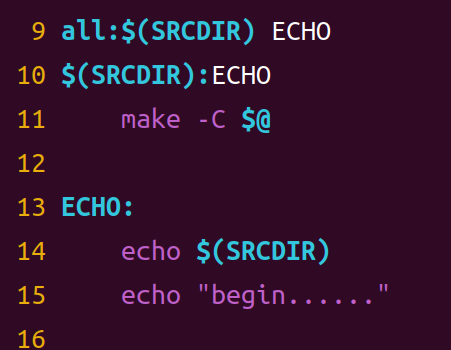

因为有两个目标,所以我们需要再前面添加伪目标all

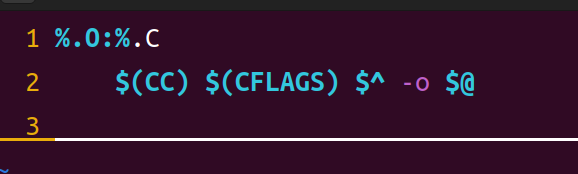

伪代码,在src中的Makefile文件,采用通配符实现.c->.o

问题2:

进入了src目录,但是没有进行真正的编译,这又是什么问题?

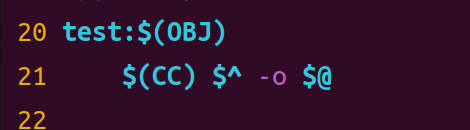

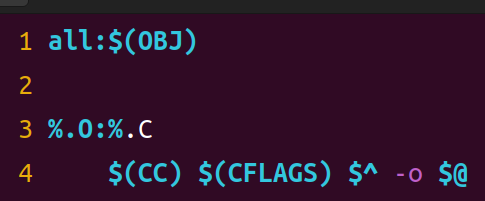

在src的Makefile中,采用%.o:%.c的写法存在问题,因为缺少目标

就如:

在这里如果缺少了test这个目标,那么就会报错,因此我们需要在通配符前添加目标

问题3:

现在进入后显示红线,问题是什么如何解决?

我们在src的Makefile中使用的变量并没有定义过,因此需要使用export声明

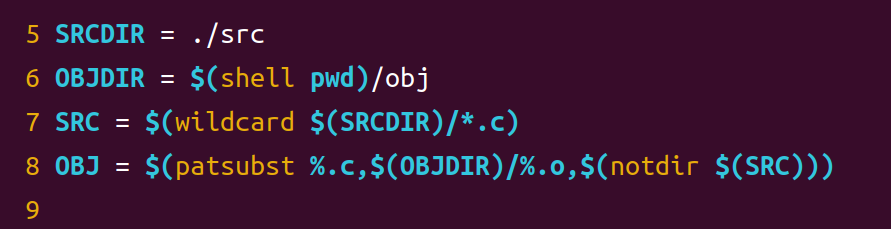

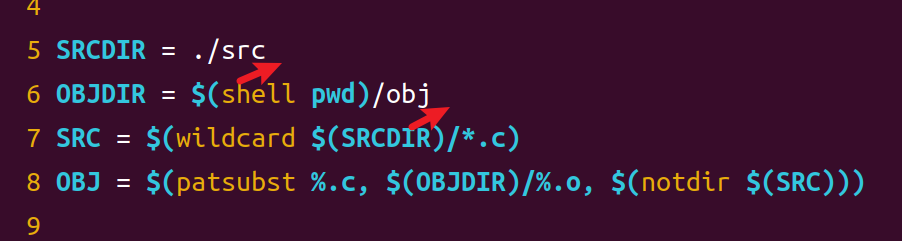

我们再对之前函数中文件的所在位置进行修改,.c文件在src目录下,.o文件也需要生成到obj目录下

![]()

该写法默认.c文件在当前目录下

$(SRC)获取的是包含路径名称的.c文件,我们需要去掉它的路径名

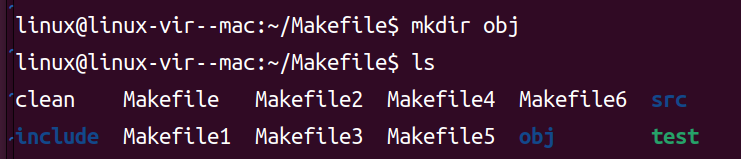

问题4:

解决方法:提前创建好obj目录,不然生成的.o文件没有地方存放

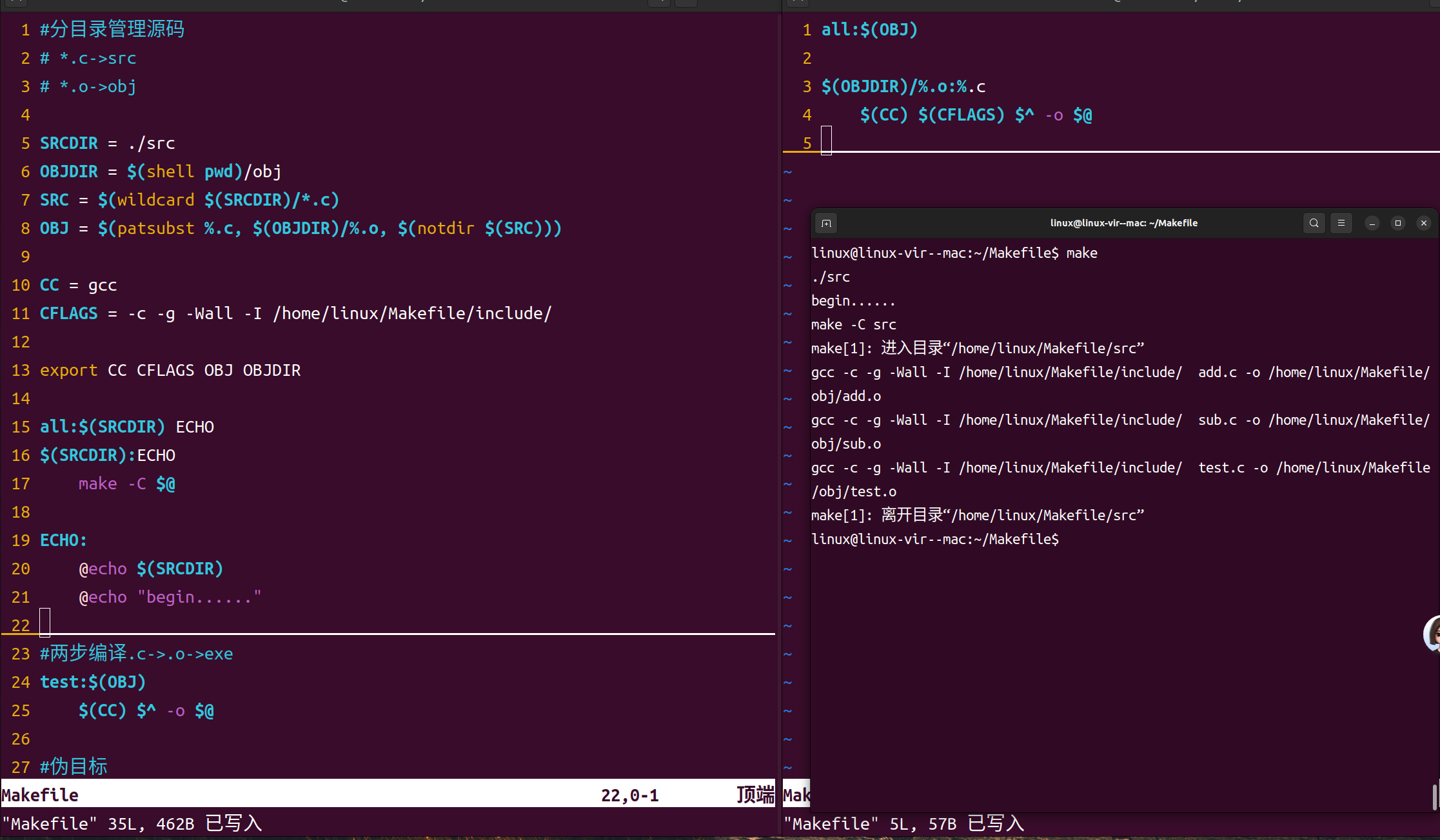

上面显示成功在obj目录生成.o文件

最后,在all添加目标test,即可生成可执行文件

常见问题:

箭头后面不能有空格

ps:就因为这个问题,搞到凌晨2点都没找出错误

3.源码展示:

#主Makefile代码:

#分目录管理源码

# *.c->src

# *.o->obj

SRCDIR = ./src

OBJDIR = $(shell pwd)/obj

SRC = $(wildcard $(SRCDIR)/*.c)

OBJ = $(patsubst %.c, $(OBJDIR)/%.o, $(notdir $(SRC)))

CC = gcc

CFLAGS = -c -g -Wall -I /home/linux/Makefile/include/

export CC CFLAGS OBJ OBJDIR

all:$(SRCDIR) ECHO test

$(SRCDIR):ECHO

make -C $@

ECHO:

@echo $(SRCDIR)

@echo "begin......"

#两步编译.c->.o->exe

test:$(OBJ)

$(CC) $^ -o $@

#伪目标

.PHONY:clean

clean:

$(RM) *.o

#src目录下的Makefile代码:

all:$(OBJ)

$(OBJDIR)/%.o:%.c

$(CC) $(CFLAGS) $^ -o $@

1139

1139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?