对vcs需要掌握的东西:

一、使用vcs做仿真

二、使用vcs进行debug

三、使用vcd+file进行后仿

四、检测仿真不匹配

五、快速RTL级仿真

六、快速门级仿真

七、代码覆盖率

一、使用vcs做仿真

1、基础知识

vcs仿真分为两个步骤:1、编译;2、仿真

vcs编译命令格式:vcs sourcefile [compile_time_option]

sourcefile:包含所有的verilog/SV格式的DUT和testbench文件,文件之间以空格分开

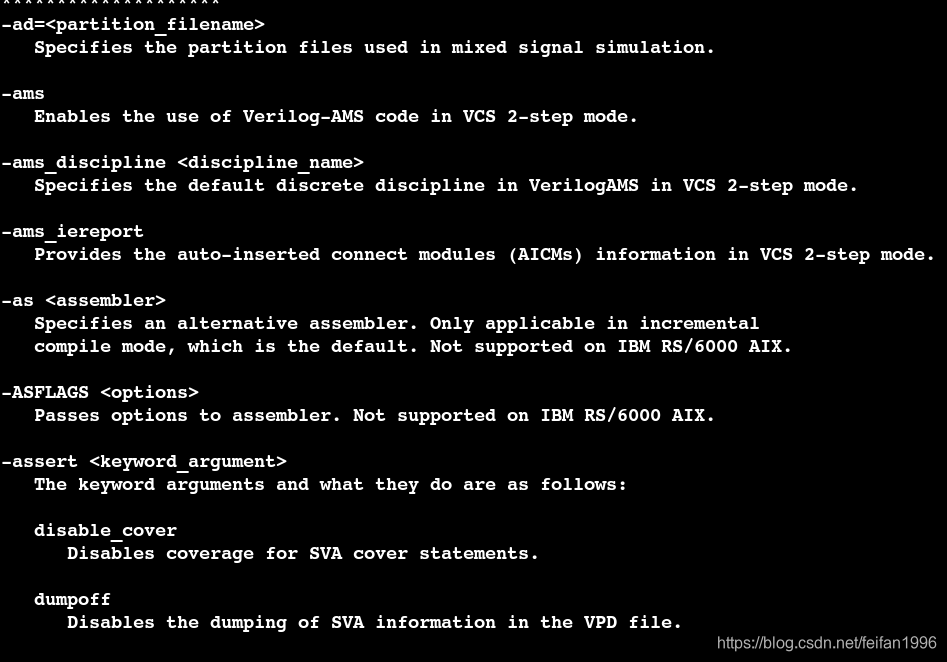

compile_time_option:vcs仿真时的控制指令

vcs -help:列出所有的编译选项,运行时间选项和环境变量

&nb

本文介绍了如何使用VCS进行异步FIFO的仿真,包括VCS的基础操作、编译选项、仿真命令以及如何查看波形。通过详细解释编译过程和运行时选项,如增量编译、日志文件、库目录和宏定义,帮助读者理解VCS仿真流程。同时,展示了文件组织结构和makefile的编写,以实现自动化编译和仿真。

本文介绍了如何使用VCS进行异步FIFO的仿真,包括VCS的基础操作、编译选项、仿真命令以及如何查看波形。通过详细解释编译过程和运行时选项,如增量编译、日志文件、库目录和宏定义,帮助读者理解VCS仿真流程。同时,展示了文件组织结构和makefile的编写,以实现自动化编译和仿真。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3987

3987

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?