高速先生成员:周伟

上一篇文章 过孔Stub对ddrx地址信号的影响 提到过后面会有stub对数据信号的影响,今天我们就一起来看看吧。

前文通过几个仿真例子看到,长stub对3200Mbps以内的DDRx地址信号来说有一定的好处,对于速率不是那么高的信号(不超过8Gbps),如DDR4、DDR5甚至LPDDR5,我们是否可以把这个结论再扩展到速率更高的数据信号上呢?于是我们又做了如下一些仿真来看看长短stub在更高速率的数据上的一些对比。

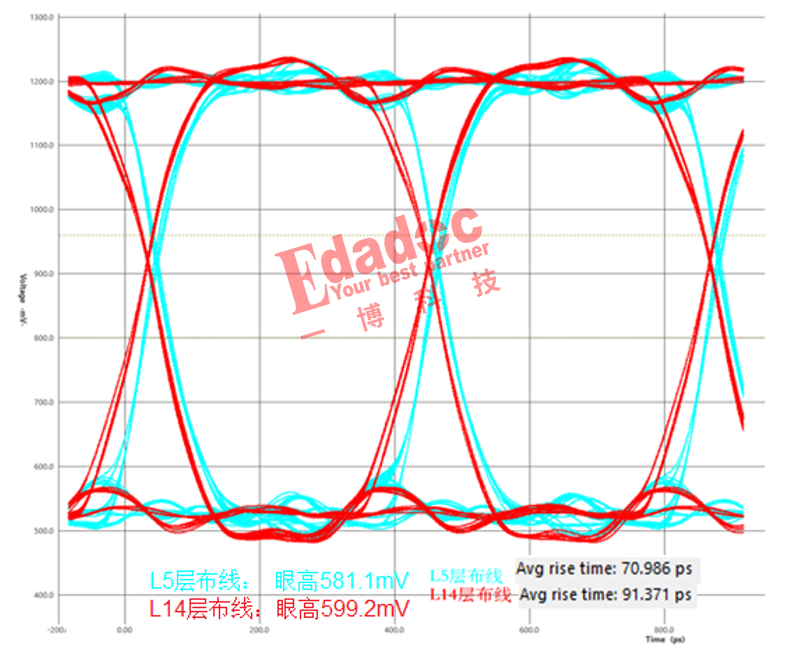

还是上文同样的叠层和驱动,接收采用ODT60,在数据率为2400Mbps的时候仿真出来的数据眼图如下图1所示。

图1 速率2400Mbps时数据信号写眼图

红色L14层走线的眼图看起来眼高更高,jitter也小点,对应的斜率也大一点,说明长stub对数据信号在2400Mbps的速率下基本没什么影响,甚至还会稍微好点。进一步把速率提高到3200Mbps,其他不变的情况下长短stub的眼图仿真结果如下图2所示。

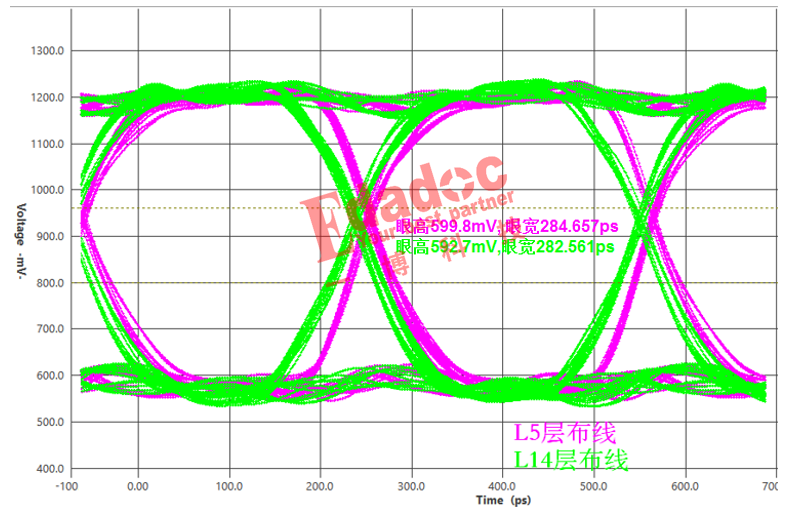

图2 速率3200Mbps时数据信号写眼图

可以看到速率上来之后,短stub的优势慢慢开始体现出来了,眼高和眼宽都稍微比长stub的布线层信号要好。

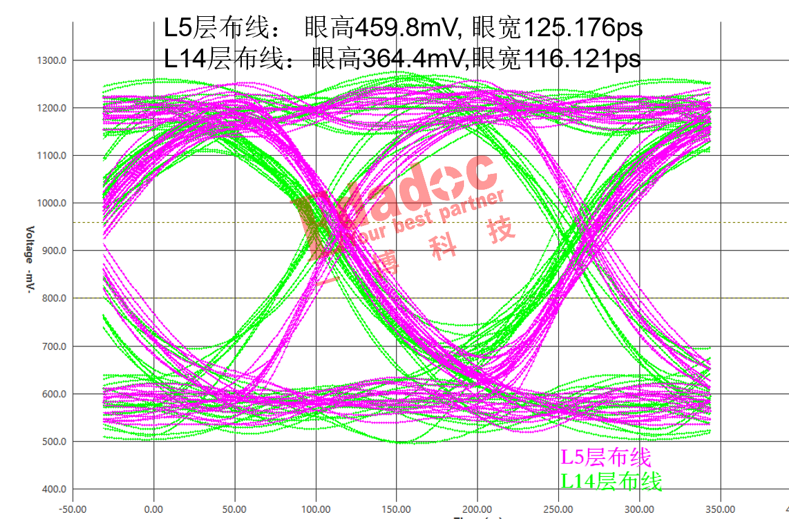

我们接下来再看看DDR5 6400Mbps速率的情况,于是其他条件都不变,只是将速率提升到6400Mbps,颗粒模型也换成支持DDR5的,仍然采用ODT60的端接,仿真后波形如下图3所示。

图3 速率6400Mbps时数据信号写眼图

从仿真结果可以看出,速率提升到6400Mbps时,长stub的L14层走线信号眼图急剧变差,眼高和眼宽都明显小于短stub的L5层走线,说明DDR5的数据信号还是要适当考虑stub的影响,PCB设计时就要考虑stub较短的层面。

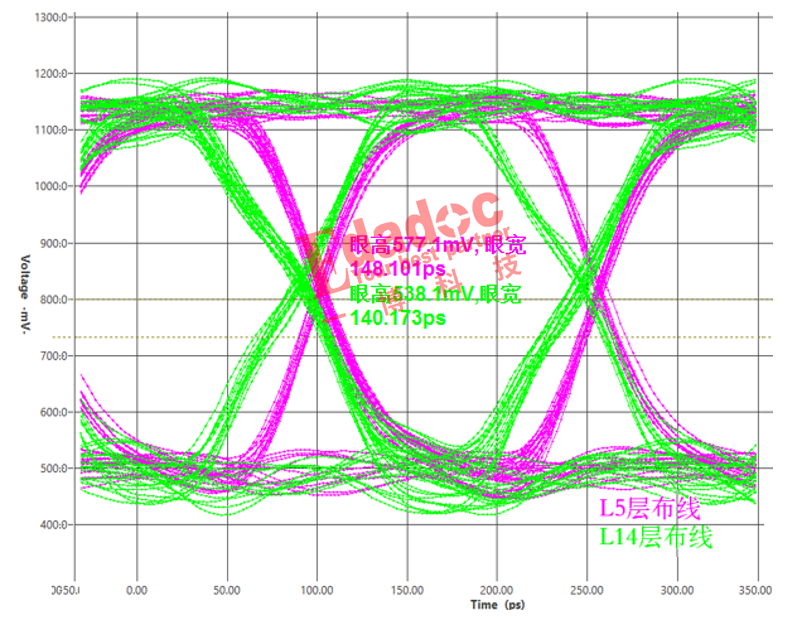

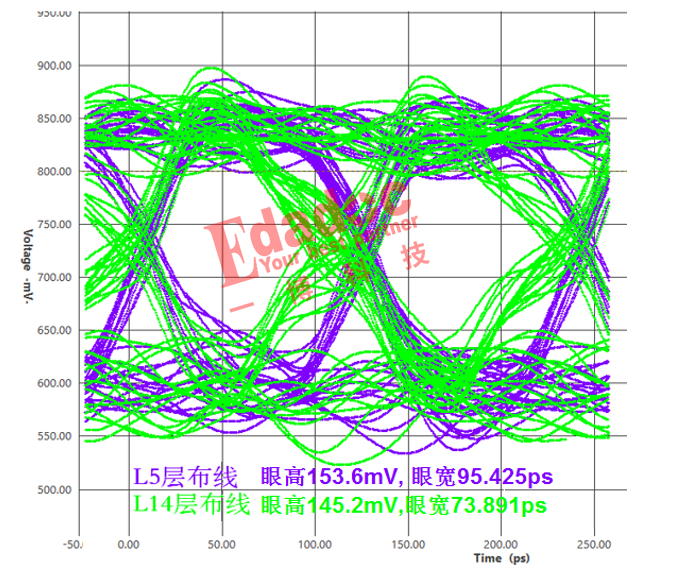

同时我们又验证了某广泛使用的FPGA支持DDR5信号的模型,在其他不变的情况下只是换了主控的模型,仿真结果如下图4所示。

图4 另一驱动速率6400Mbps时数据信号写眼图

换了驱动后,仿真结论还是一样的,长stub的信号沿变缓了很多,导致眼高和眼宽都变小了。

考虑到现在LPDDR5的应用也越来越多了,且我们也已经仿真过很多啦,接下来我们就用LPDDR5模型再来验证一下长短Stub的影响。拓扑还是不变,驱动和接收换成支持LPDDR5的模型,在数据速率8533Mbps 时不开均衡的仿真对比结果如下图5所示。

图5 速率8533Mbps时数据信号写眼图

可以看到有长stub的L14层信号的眼图急剧变差,jitter变大了很多,比短stub的L5层走线的信号眼高和眼宽都小了,裕量相对变少,说明速率越高后stub的影响还是比较大,此时尽量保持短stub层走线,至于是否一定要背钻,还是要看情况,大多数情况下还是可以不用的,毕竟背钻需要额外增加成本,可以优先走stub短的层。如果实在避免不了长stub的层,我们还是可以参考高速信号stub长度的经验,当stub长度(单位mil)超过1.5倍的300/信号速率(单位Gbps),尽量或必须背钻。不考虑成本的情况下,当stub长度(单位mil)超过300/信号速率(单位Gbps)时就可以做背钻了。

说到长stub就想到了背钻,大家一起来说说国内板厂经背钻后的stub长度还剩多少?欢迎吐槽

关于一博:

一博科技成立于2003年3月,深圳创业板上市公司,股票代码: 301366,专注于高速PCB设计、SI/PI仿真分析等技术服务,并为研发样机及批量生产提供高品质、短交期的PCB制板与PCBA生产服务。致力于打造一流的硬件创新平台,加快电子产品的硬件创新进程,提升产品质量。

一博PCB板厂位于深圳及珠海,提供2-120层高速、高品质、快交期的PCB生产服务。我司现已在深圳、珠海、上海、成都、长沙、天津设立六家PCBA工厂,厂房面积15万平米,现有60余条SMT产线,专注高品质的研发快件、批量的SMT贴片、后焊、组装等服务。

276

276

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?