SPI(Serial Peripheral Interface--

串行外设接口)总线系统是一种同步串行外设接口,它可以使

MCU与各种外围设备以串行方式进行通信以交换信息。SPI有三个

寄存器分别为:

控制寄存器SPCR,

状态寄存器SPSR,

数据寄存器SPDR。外围设备包括FLASHRAM、网络控制器、LCD显示驱动器、

A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线NSS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

-

中文名

- 串行外设接口 外文名

- Serial Peripheral Interface(SPI)

-

简 称

- SPI 类 别

- 接口

目录

SPI接口的全称是"Serial Peripheral Interface",意为串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM、FLASH、

实时时钟、AD

转换器,还有

数字信号处理器和数字信号解码器之间。

信号线少,协议简单,相对数据速率高。

(1)MOSI – 主器件

数据输出,从器件数据输入

(2)MISO – 主器件数据输入,从器件数据输出

(3)SCLK –

时钟信号,由主器件产生,最大为fPCLK/2,从模式频率最大为fCPU/2

(4)NSS – 从器件使能信号,由主器件控制,有的IC会标注为CS(Chip select)

在

点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。

SPI接口在内部硬件实际上是两个简单的

移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如下图所示,在SCLK的上升沿上数据改变,同时一位数据被存入移位寄存器。

最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。

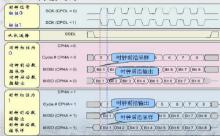

SPI有四种工作模式,各个工作模式的不同在于SCLK不同, 具体工作由CPOL,CPHA决定

CPOL: (Clock Polarity),时钟极性

当CPOL为0时,时钟空闲时电平为低;

当CPOL为1时,时钟空闲时电平为高;

CPHA:(Clock Phase),时钟相位

当CPHA为0时,时钟周期的前一边缘采集数据,时钟周期的后一边缘输出数据;

当CPHA为1时,时钟周期的后一边缘采集数据,时钟周期的后一边缘输出数据;

CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:

四种工作模式现如下:

2137

2137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?