一、 查看node

CXL type3设备,通过NUMA node来管理扩展内存,查看NUMA node是否生成可以通过命令查看:

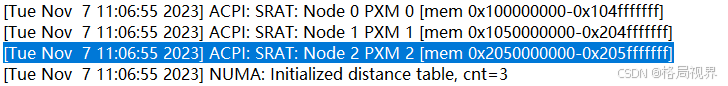

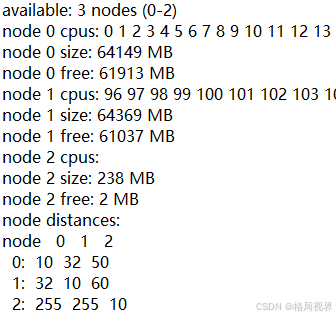

numactl -H

从上图可以看到除了本地node 0 、1外,新增了node 2

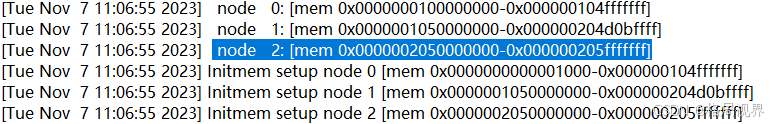

通过dmesg查看启动信息:

可以看到node信息,可以看到node 2对应的memory分配的地址范围。

二、 通过lspci查看CXL设备信息:

lspci | grep CXL

三、 查看ACPI表信息

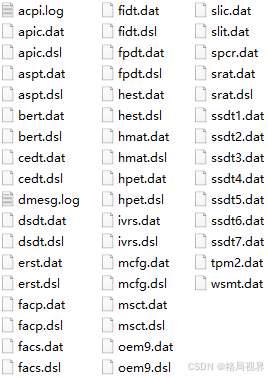

ACPI node信息是系统生成NUMA node的必要条件,为排查CXL type3设备在BIOS启动过程中,是否正常获得ACPI表,可以通过以下命令查看,

1. acpidump > acpi.log

2. acpixtract -a acpi.log

3. iasl -d *.dat

会看到一下文件:

在hmat.dsl, srat.dsl等文件中可以看到domain node 2相关的信息。

四、 性能测试

使用mlc工具测试cxl memory性能和时延:

mlc --bandwidth_matrix

mlc --latency_matrix

mlc更多用法:

默认是顺序读,或顺序写,可以指定大小,命令可以参考如下:

一、大块内存顺序读带宽测试

1. 基础顺序读(全读,默认顺序访问)

- 命令:mlc --bandwidth_matrix -R -b<size>

或 mlc --peak_injection_bandwidth -R -b<size>

或 mlc --max_bandwidth -R -b<size> - 参数说明:

- -R:强制生成 100% 读流量,确保纯顺序读测试;

- -b<size>:指定大块缓冲区大小(支持k/m/g后缀,如-b2g表示 2GB),需满足 “单线程缓冲区≥100MB + 单插槽所有线程缓冲区总和>该插槽末级缓存(L3)总大小”,确保访问目标为内存而非缓存;

- --bandwidth_matrix/--peak_injection_bandwidth/--max_bandwidth:分别对应 “跨插槽带宽矩阵”“核心满速峰值带宽”“自动调优最大带宽” 场景,按需选择。

- 示例:mlc --peak_injection_bandwidth -R -b4g

含义:以 4GB 大块缓冲区,测试核心满速请求下的 100% 顺序读内存带宽(默认顺序访问)。

2. 单 NUMA 节点大块顺序读

- 命令:mlc --memory_bandwidth_scan -j<node> -b<size>

- 参数说明:

- --memory_bandwidth_scan:按 1GB 块粒度扫描指定 NUMA 节点的全内存范围,默认顺序访问;

- -j<node>:指定目标 NUMA 节点(如-j0表示 NUMA 节点 0);

- -b<size>:指定大块缓冲区,确保覆盖内存区域(如-b10g)。

- 示例:mlc --memory_bandwidth_scan -j1 -b8g

含义:扫描 NUMA 节点 1 的全内存,以 8GB 大块缓冲区测试各 1GB 块的顺序读带宽,输出带宽分布直方图。

二、大块内存顺序写带宽测试

仅支持 “100% 非临时写”(文档未提及普通全写,需通过-W6参数指定非临时写),命令需结合缓冲区大小与写模式参数:

1. 基础顺序非临时写

- 命令:mlc --bandwidth_matrix -W6 -b<size>

或 mlc --peak_injection_bandwidth -W6 -b<size> - 参数说明:

- -W6:生成 100% 非临时写流量(顺序访问),对应内存控制器视角的纯写操作;

- -b<size>:指定大块缓冲区(如-b2g),满足 “单线程缓冲区≥100MB + 单插槽总缓冲区>L3 总大小”,确保写操作目标为内存。

- 示例:mlc --bandwidth_matrix -W6 -b3g

含义:以 3GB 大块缓冲区,测试跨插槽的 100% 顺序非临时写内存带宽矩阵。

三、大块内存顺序读写交替测试

通过-Wn参数定义读写比(内存控制器视角),实现顺序读写交替,默认顺序访问:

1. 常用读写比命令模板

- 命令:mlc --<测试模式> -W<n> -b<size>

- 参数说明:

- -W<n>:定义读写比,如-W2(2 读 1 写)、-W3(3 读 1 写)、-W5(1 读 1 写),均为顺序交替;

- <测试模式>:同前,可选--bandwidth_matrix/--peak_injection_bandwidth等;

- -b<size>:指定大块缓冲区(如-b2g)。

- 示例 1(1 读 1 写交替):mlc --peak_injection_bandwidth -W5 -b2g

含义:以 2GB 大块缓冲区,测试核心满速下 1 读 1 写顺序交替的内存带宽。 - 示例 2(2 读 1 写交替):mlc --loaded_latency -W2 -b1g -T

含义:以 1GB 大块缓冲区,测试 2 读 1 写顺序交替的内存带宽(-T仅测带宽不测延迟)

QA:

调试CXL设备时,当系统无法启动,可以禁止系统对CXL memory的自由使用,如通过reserve memory的方式,soft reserve可以保留node而hard reserve看不到node,但是可以访问对应的物理地址。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?