Hyperlynx DDR SI 仿真分析技术 | IBIS 模型适配

1. 技术简介

随着电子技术水平不断提高,元器件运行速度不断上升,设计复杂程度越来越高,PCB的高速效应成为普遍现象,信号失真问题也越来越严重,这包括:过冲/欠冲、振铃、毛刺、串扰和时序问题。当失真问题严重到一定程度的时候,系统中的逻辑就会出现误判。而且,当今的 PCB 设计通常面对的是一个非常复杂的数模混合电路工程。因此,当今电子电路的设计,通常会面对来自信号完整性、电源完整性、热、电磁兼容等问题的挑战。基于产品可靠性要求的考虑,应当引入仿真验证的手段。

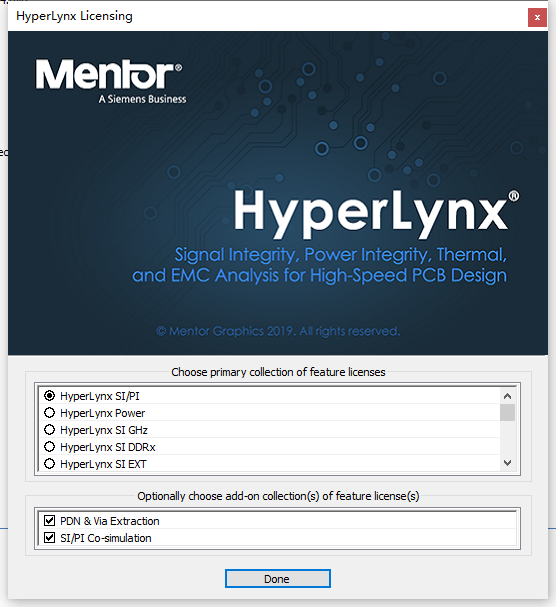

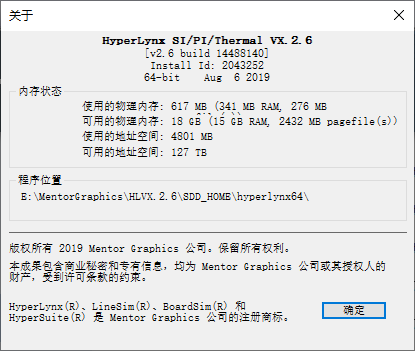

HyperLynx 是 Mentor 公司的电子电路仿真验证系列工具,提供了完整的仿真分析功能,包括: 信号完整性分析工具 HyperLynx SI、电源完整性分析工具 HyperLynx PI、三维电磁场建模与仿真工具 HyperLynx 3D EM、板级热分析工具 HyperLynx Thermal、板级电磁兼容分析工具 HyperLynx DRC、模拟/数模混合电路分析工具 HyperLynx Analog。借助 HyperLynx 电子电路仿真验证系列工具,工程师能够更加轻松地应对当今电子电路设计所面临的全方位的挑战,有效地减少产品的设计反复,缩短开发周期,加快产品的上市时间,并极大地提高产品的可靠性。

在电子设计中已经有多种可以用于 PCB 板级信号完整性分析的模型,其中最为常用的有三种,分别是 SPICE、IBIS 和 Verilog-AMS、VHDL-AMS。

SPICE(Simulation Program with Integrated Circuit Emphasis)是一种功能强大的通用模拟电路仿真器,描述器件内部的实际电气连接。SPICE 模型由两部分组成:模型方程式(Model Equations)和模型参数(Model Parameters)。由于提供了模型方程式,因而可以把SPICE模型与仿真器的算法非常紧密地联接起来,可以获得更好的分析效率和分析结果。PCB 板级的 SPICE 模型仿真计算量较大,分析比较费时。

IBIS(Input/Output Buffer Information Specification)模型是一种基于 V/I 曲线的对 I/O BUFFER 快速准确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,提供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适合做振荡和串扰等高频效应的计算与仿真。

AMS(IAnolog/Mixed-Signal)是新的模拟混合信号仿真/设计标准,是一种行为模型语言,支持模拟、数字、数模混合电路系统的建模与仿真。作为硬件行为级的建模语言,Verilog-AMS和VHDL-AMS分别是Verilog和VHDL的超集,而Verilog-A则是Verilog-AMS的一个子集。

下面介绍如何基于 IBIS 模型对 DDR 的信号完整性仿真分析以及为了适配 HyperLynx 应用对 IBIS 模型如何修改。

2. 参考资料

3. 安装软件

本文介绍了Hyperlynx DDR SI仿真分析技术,探讨了电子设计中的信号完整性挑战,重点讲解了IBIS模型在DDR SI仿真中的应用和适配HyperLynx的过程,以帮助工程师提升设计效率和产品可靠性。

本文介绍了Hyperlynx DDR SI仿真分析技术,探讨了电子设计中的信号完整性挑战,重点讲解了IBIS模型在DDR SI仿真中的应用和适配HyperLynx的过程,以帮助工程师提升设计效率和产品可靠性。

2864

2864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?