超低功耗可扩展吞吐量多核数字信号处理应用的设计

米塔·斯里瓦斯塔夫、穆罕默德·艾特沙姆丁、凯尔·斯特格纳和莱拉·纳扎汉达利,弗吉尼亚 理工学院暨州立大学

我们提出了一种系统级解决方案,用于设计面向能量受限应用的工艺变异感知(PVA)可扩展吞吐量多核系统。在所提出的方法中,我们利用电压调节的优势来实现能效,同时通过挖掘各种DSP设计中存在的并行性来补偿吞吐量的损失。我们证明,与简单的动态电压调节相比,这种混合方法在不同的工作负载环境下可节省6.27%至 28.15%的功耗。本文介绍了基于90nm工艺节点制造的原型芯片的设计细节及其研究成果。该芯片包含8个同构 FIR核,能够在近阈值到标称电压范围内运行。在我们的20个芯片样本中,在标称电压(0.9伏特)下观察到核心间速度差异为7%,在近阈值电压(0.55伏)下为26%。我们还观察到核心功耗存在54%的差异。对于任意期望吞吐量,系统将根据芯片内部各核心的速度和功耗特性选择最佳核心数量及其最优工作电压。我们还将展示此类系统在环境温度变化下的能效分析结果。

分类与主题描述

C.3[Special-Purpose and Application-Based Systems]:实时和嵌入式系统;B.8.2[Performance and Reliability]:性能分析与设计辅助;C.0[General]:系统架构 通用术语:设计、算法、实验 附加关键词和短语:工艺偏差,低功耗,电压调节,活动单元缩放,多核,DVFS,90纳米,能效,专用集成电路芯片,实现,众核,DSP,近阈值,温度变化

ACM参考格式

米塔·斯里瓦斯塔夫、穆罕默德·艾特沙姆丁、凯尔·斯特格纳和莱拉·纳扎汉达利。2015年。超低功耗可扩展吞吐量 多核DSP应用设计。ACM电子系统设计自动化汇刊20卷3期,文章34(2015年6月),21页。DOI: http://dx.doi.org/10.1145/2720018

引言

对高能效DSP设计的需求不断增长,因为这些设计越来越多地应用于由小型电池或有限的 采集能量供电的各种场景中。许多此类低功耗系统在近阈值区域消耗最少的能量,此时电 源电压接近器件的阈值电压。在近阈值区域,虽然功耗和能耗降低,但性能显著下降。通 过在较低电压下使用多个并行相同的(同构)核心,可以在保持这些系统能效的同时恢复 部分损失的性能。这对于算法尤其有利可以高度并行化且开销可忽略的应用,例如FIR滤波器。在本文中,我们介绍了工作在近 阈值区域的同构多核系统的设计细节。我们基于在90nm专用集成电路芯片上测得的数据 进行分析并展示结果。

在动态环境中,目标吞吐量随时间变化,传统方法是动态调整工作电压以满足所需的 吞吐量。我们将此类系统称为BASE。然而,对于资源有限的小型低功耗嵌入式系统而言, 由于额外的开销,为DSP核心提供多种可访问的工作电压是不现实的。为此,我们提出一 种混合方法,将动态电压调节(VS)与激活的核心数量调整(激活核心缩放,ACS)相结 合。该混合方法仅使用少量工作电压,通过确定最优的激活核心数量(Nopt)及其最优工 作电压(Vddopt),以最小的能量消耗满足目标吞吐量。

工作在近阈值电压区域的电路受到工艺变异(PV)效应的显著影响[Wang等 2006],, 这会影响核心的速度和功耗特性。在存在工艺变异的情况下,同构多核设计中的各个核心 在工作速度和功耗方面可能表现出异构性。换句话说,由于工艺变异,某些核心运行速度 较高,而其他核心则运行较慢。类似地,由于工艺变异,多核设计中不同核心的功耗也可 能存在显著差异。因此,算法在确定Nopt和Vddopt时,应考虑每个核心所受的工艺变异效 应。在我们的20个芯片样本中,在标称电压(0.9伏)下观察到核心间速度差异为7%,而 在近阈值电压(0.55伏)下达到26%。我们还观察到核心功耗特性的巨大差异。例如,在 标称电压下,所有核心以50MHz运行时,其功耗差异达到54%。

一种将同质性重新引入设计的简单解决方案是让所有核心以设计中最慢核心的速度运 行。这在典型的全局电压调节(VS)系统中将会如此。然而,我们提出的方法是在制造完 成后(仅执行一次)收集芯片上每个核心的特征行为,这将有助于进一步提高系统的能效。例如,当所需的最佳核心数量少于系统中存在的总核心数时,提出的方法可以有选择地挑 选核心,系统可以按照所选核心组定义的速度运行,而不是按照系统中最慢的核心速度运 行。这种有选择地挑选核心的方法也是能效较高的,如Srivastav等[2013]所示。然而,对 于需要使用系统中所有核心的工作负载条件,两种方法的系统吞吐量仍将由最慢的核心决 定。

本文中,我们将基于所提出的考虑工艺变异的设计方法,展示片内和芯间工艺电压效 应对核心最佳数量Nopt以及最佳工作电压Vddopt的影响。我们将混合主动核心缩放( ACS)与电压缩放(VS)方法论应用于8核FIR设计,以实现从100兆赫到2.5吉赫的广泛期 望吞吐量。与仅具备VS能力的系统相比,我们观察到节能幅度为6%至28%。需要指出的是, 本工作的目标并非设计出速度最快或能效最高的FIR滤波器。相反,本工作的主要目标是找 出在结合使用ACS和VS并充分考虑工艺变异效应的情况下所能实现的节能程度。我们认识 到,除我们的方法之外,还可采用多种与本方法正交的电路级和架构级技术,以进一步提 升设计的能效。

除了工艺之外,芯片上的集成电路还会受到其他变异源的影响,例如温度、电源噪声和电流不足[Wirnshofer 2013]。在这项工作中,我们忽略了具有动态特性的电源噪声变化和电流不足问题。温度升 高通常由于载流子迁移率降低和互连电阻增加而导致电路速度变慢。然而,在我们的低 VDD(近阈值电压)情况下,电路工作在温度反转区域。在此区域,阈值电压随温度下降 的影响超过了迁移率退化的影响。因此,电路会随着温度升高而加快速度,反之亦然。本 文还将展示温度变化对核心在速度和功耗特性方面的影响,并进一步评估其对高能效架构 的影响。

这项工作分为两个阶段完成。在第一阶段,对多核DSP设计进行了广泛的仿真研究, 并从能耗、运行速度和核心数量等方面进行了分析和展示[Srivastav等 2012, 2013]。在本 文所呈现的第二阶段中,采用90nm工艺设计了一款多核FIR滤波器ASIC芯片,以在硬件 上验证我们前期论文中的研究成果。

本文的主要贡献如下。

(1)我们提出了一种可扩展吞吐量8核FIR滤波器设计,该设计采用精细的表征方法、非易失 性存储器记录各种配置,并结合核心数量缩放与最优电压选择的混合方法,在考虑工艺偏 差的情况下实现最大能效。(2)我们提供了在90nm IBM工艺技术下制造的8核FIR滤波器的 频率和功率测量结果,以此展示所提出的混合方法在节能方面的有效性。(3)我们对20个芯 片样本在宽范围吞吐量[100MHz–2.5GHz]下,工艺偏差对核心数量和工作电压的影响进行 了扩展分析。(4)我们分析了温度变化对能效架构的影响。

尽管我们的工作重点是同构多核设计以及可并行化的应用,但其优势并不局限于此类 芯片。在当今的设计中,芯片通常是多个具有不同功能的IP设计的集合。我们的研究将使 那些可以并行化的功能(通常是DSP处理器)在面对工艺偏差时,实现更高的能效。

相关工作

近年来,集成电路设计研究人员对多核数字信号处理系统中的节能问题给予了大量关注。本节总结了与此相关的研究工作。

王和钱德拉卡桑[2005]提出了首个在亚阈值区域运行的180毫伏快速傅里叶变换架构。该研究探索了通过电压调节来降低每次操作能耗的方法。然而,由此产生的吞吐量非常低, 在180毫伏时为164Hz,在350毫伏时为10MHz。自那以后,大量研究致力于探索近/亚阈 值系统和工艺变异性[Calhounetal.2010;考尔洪和钱德拉卡桑2004,2006;Zhaiet al. 2005]。过去许多原型已证明可以将传统的电压调节极限扩展至低于阈值电压,即亚阈值电压区[王和钱德拉卡桑2005;Bowmanetal. 2007]。

过去已开展并持续进行大量研究,以分析和建模工艺偏差(PV)的影响,特别是对多 核设计的影响[Borkaretal.2003;Humenayetal.2007;Seoketal.2011; Bowmanetal. 2002]。多位研究人员探索了采用动态电压频率调节(DVFS)方法在速度 和功耗之间进行权衡的优化技术[Aydinetal.2001;Shinetal.2000;Jejurikarand Gupta2006;HerbertandMarculescu2009;LeSueurandHeiser 2010]。此外, Kim等[2011]提出了一种将DVFS应用于多核通用处理器的技术。这些研究大多针对工作 在超阈值区域的设计,其中工艺偏差的影响较小。然而,在近阈值区域,工艺变异性的影 响显著增大,因此不可忽略[Wangetal. 2006]。因此,本文展示了片内和片间工艺变异 在近阈值电压下对20个芯片每个包含8个核心的速度和功耗特性的影响。

Sartori等人[2010]提出了一种在多核系统中高效选择核心运行的方法论。然而,他 们的方法仅基于性能(速度)进行优化,未考虑功耗或能量。在设计能效解决方案时,分 析性能与功耗之间的权衡至关重要。此外,Herbert等人[2012]通过研究电压/频率岛下 的变异性提供了有益的见解。

Dighe等人[2010]提出了一款在65nm工艺下工作电压最低为0.8V的80核处理器的最 大频率特性存在非常有趣的变异性。尽管本文提到了对最大频率和功耗的单独影响,但作 者并未探讨这种变异性带来的能效增益或损失问题。我们进一步扩展了这项工作,通过分 析工艺变异性对系统参数(如核心数量和工作电压)的影响,在设计能效系统时加以考虑。此外,我们还将评估温度变化对这类系统的影响。

总之,上述所有工作为我们的贡献奠定了坚实的基础。然而,这些工作要么缺乏对工艺变 异(PV)在近阈值工作区域对系统设计影响的分析,要么在系统可能运行的不同工作负载条件 方面考虑不完整。我们的工作在此基础上进一步推进,提出了一种多核数字信号处理系统的设 计,该设计能够在存在工艺变异(PV)的情况下适应广泛的吞吐量需求,同时实现最大能效。在当前提出的工作中,我们假设系统可使用预先确定的固定且量化后的电压。然而,本研究并 未探讨生成这些电压所涉及的复杂性,如Calhoun和Chandrakasan[2006]所述。

我们还展示了一个在90nm工艺节点上构建的原型,该原型包含8个同构核心,工作在 近阈值区域,以证明该算法在为期望吞吐量选择最能效架构方面的有效性。最后,我们将 展示温度变化对能效架构的影响。

设计架构与方法论

在本节中,我们将 fi 首先讨论系统架构的详细信息。随后,我们将介绍用于选择最能效架构的系统参数选 择方法。表I给出了进行所有实验所用工具的摘要。

系统架构

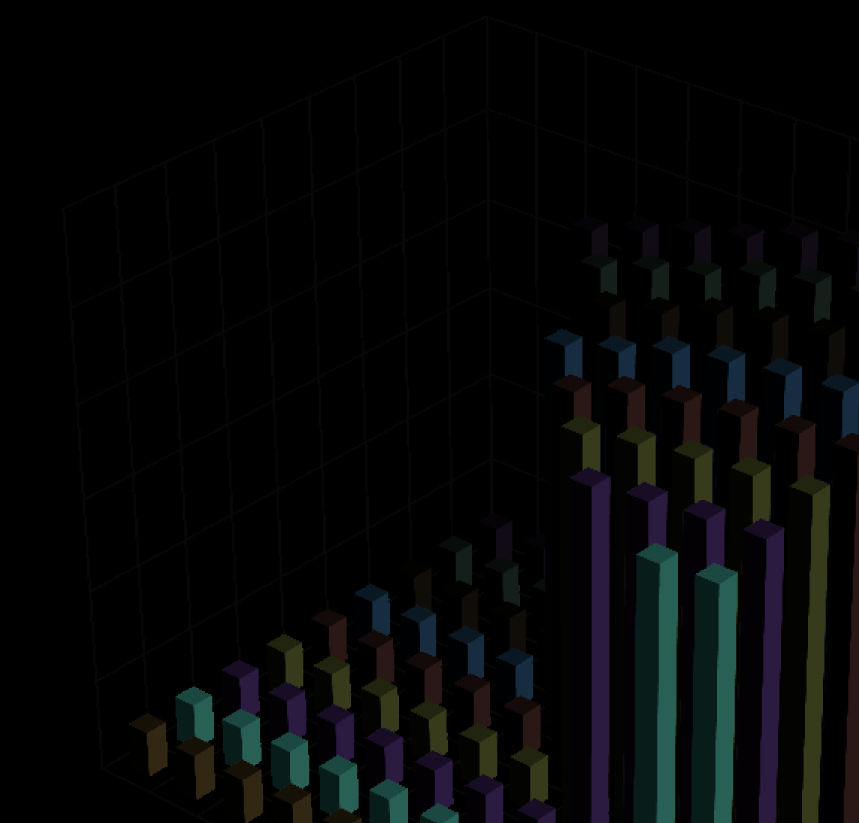

同构多核系统的架构如图1所示。它由多个核心以及若干可选的工作电压组成。该系统架构 的设计使其能够适应现场的任何期望吞吐量。这类应用在需求多变的环境中非常理想系统的吞吐量随时间变化。当系统运行时,事件检测器或用户将决定期望的系统吞吐量。例如,在现场用于检测经过车辆的声学传感器中,当检测到感兴趣的事件时,需要提高滤 波器的分辨率。设计此类系统的挑战在于,针对期望吞吐量,选择最优核心总数(Nopt)以 及在部署期间可用的最优工作电压(Vddopt)。尽管核心数量(N)可以任意选择,但对于 大多数数字信号处理应用而言,如果N 不是2的幂,则控制信号和数据流(总线连接等) 会变得越来越复杂且效率低下。因此,本文研究了一种多核FIR滤波器,其中核心数量选择 为2的幂,具体为1、2、4和8。

部署之前,会对所有核心进行一次性表征。典型控制器的有限状态机(FSM)也在图 1中示出。利用下一节第3.2节中描述的算法,针对系统预期运行的每个期望吞吐量,控制器 计算[Nopt Vddopt]。该配置随后作为查找表(LUT)存储在非易失性存储器中,并可在运 行期间由控制器读取。在本文中,我们假设系统在从100兆赫到2.5吉赫的广泛吞吐量范围 内运行。

控制器还通过时钟门控(CG)或电源门控(PG)将不需要的核心置于休眠状态。CG技术 应用速度较快,但仅关闭时钟,因此在非活动模式下,设计仍会消耗漏电功耗。对于具有较长非 活动空闲周期的系统而言,这种方式效率不高。而采用PG技术,则会通过断开核心的电源来减 少功耗。

图1.动态可扩展吞吐量同构多核系统的架构。

表I.工具流程

库 IBM90nm CMOS(ARM单元)

硬件描述语言与仿真 Verilog,SynopsysVCS

电压缩放特性 SynopsysHSPICE,NanoSim

功耗仿真 SynopsysPrimeTimePX

布局布线、设计规则检查与版图对电路 SynopsysICC,Calibre

测试软件 国家仪器Labview

为了更清晰地显示,图中无法达到330兆赫的点被裁剪至10MHz频率。

晶体管开关,例如上拉管。使用电源门控(PG)可以实现显著的功耗节省。然而,当核心 处于活动状态时,由于上拉管开关的漏电,会导致性能损失;同时在对核心进行上电( PU)和断电(PD)时也会带来能量损耗。时钟门控与电源门控之间的权衡如图2所示。通 过使用32个上拉管开关,发现FIR滤波器的上电和断电时间分别为14和8个时钟周期,这一 开销并不显著。对于当前面向超低功耗应用的设计,由于在长时间空闲期间能够实现可观 的漏电节省,因此更倾向于采用电源门控(PG)技术。

图2.电源门控与时钟门控方案之间的权衡。

设计参数选择

在本节中,我们将介绍一种算法,该算法将针对不同的吞吐量确定最小能耗架构。它选择 诸如核心数量和工作电压等系统参数。该算法基于穷举搜索。对于能量收集应用而言,节 能是首要考虑的因素,因此,在该算法中我们致力于优化每次操作的总能耗。通过调整核 心数量和/或工作电压来满足期望吞吐量。

例如,考虑一个能够实现330MHz期望吞吐量的系统。图3(a)展示了不同的架构元组[No p t Vddo p t], 这些元组可以满足要求并提供期望的吞吐量。此外,对于这些[N Vdd]元组,我们可以确定能效最高的架构, 如图3(b)中的峰值尖峰所示。在此示例中,Nopt= 32和Vddopt= 0.4V。因此,使用32核 心并在0.4伏特下运行的系统是实现330MHz吞吐量的最能效架构。此数据基于使用45n m PTM库[Srivastav等 2013]获得的仿真结果。

本文设计的多核FIR滤波器ASIC芯片包含8个核心。因此,系统架构可以使用1个激活 核心(1C)、2个激活核心(2C)、4个激活核心(4C)或全部8个核心激活(8C)来构建。具有特定数量激活核心的系统可以在不同电压下运行,以满足期望吞吐量。核心的工作电 压可选范围为截止电压(电路停止工作)到标称电压之间。在芯片上测得FIR核心的典型最 小电压为0.4伏特。因此,我们采用0.4伏特至0.9伏特的工作电压范围,分辨率为50毫伏。对于给定的期望吞吐量,本节提出的算法将确定最优参数[Nopt Vddopt],以实现最大能效。

理想情况下,对于固定的吞吐量,[Nopt Vddopt]组合在各个芯片之间应保持一致。然而, 由于存在芯间工艺变异效应,[Nopt Vddopt]组合在不同芯片之间有所变化。稍后在第5节中, 我们将看到核心的速度和功耗特性存在显著差异。第5节还将提供20个制造的多核FIR芯片 的[Nopt Vddopt]组合的实验结果。

此外,如果同构核心在单个芯片内确实具有相同的核心特性,那么对于1C架构而言, 从8个核心中选择任意1个核心都不会改变系统的能效。同样,对于2C和4C架构,从8个核 心中选择任意2个或任意4个核心,仍然会保持相同的效率。然而,由于存在片内工艺变异(PV),我们会发现同一芯片内的核心在速度和功耗特性上存在差异。因此,在选择[N opt Vddopt]元组时,从可用的8个核心中找到合适的一组核心(coreopt)也至关重要。

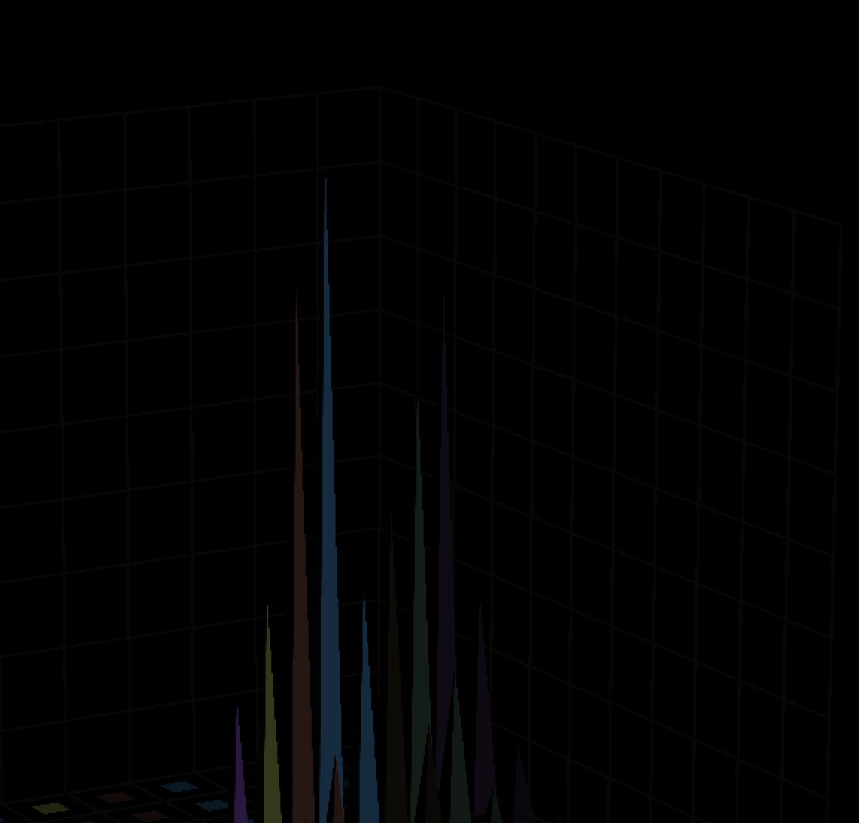

除了具有静态特性的工艺变异(PV)外,电路特性还会受到温度的影响。温度会影响 两个主要参数:载流子迁移率和阈值电压[Weste和Harris 2011]。随着温度升高,载流 子迁移率以及阈值电压都会降低。在电路层面,这表现为延迟增加(性能下降)和漏电功 耗增加。然而,这种行为会随工作电压的变化而改变。冷(−40◦°C)、室温(25◦°C)和高温( 85◦°C)条件下的综合效应如图4所示。在高VDD下,延迟具有负温度系数,即随着温度升高 而减小。这主要是因为在高VDD下,迁移率退化对延迟起主导作用。然而,在低VDD下, 延迟具有正温度系数,即随着温度升高,延迟减小。这是因为在低VDD下,阈值电压的降 低对电路特性起主导作用。随后,在第5.6节中,我们将分析温度变化在目标电压下对能效 优化配置的影响。

总之,对于期望吞吐量,最小能耗架构的系统参数将具有[Nopt、Vddopt和coreopt]。这些参 数一旦计算出来,便可存储在查找表中,供控制器在运行时选择。对于当前系统,我们需要2比 特(4个选项)来存储Nopt配置(1、2、4或8);此外,需要2比特(4个选项)来存储Vddopt配 置,以及3比特(8个选项)来存储coreopt配置(C1、C2、C3、C4、C5、C6、C7、C8)。因 此,对于每个期望吞吐量,我们需要7比特(3+ 2+ 3)来存储所有[Nopt Vddopt coreopt]配置。

在本研究中,我们考虑了系统应满足的16种可能的期望吞吐量情况,因此总共需要16* 7= 112(14字节)的内存来存储

根据吞吐量为FFT处理器a选择核心数量和工作电压。(b)为FFT处理器a选择最能量最优的[N Vdd]集合)

根据吞吐量为FFT处理器a选择核心数量和工作电压。(b)为FFT处理器a选择最能量最优的[N Vdd]集合)

图3.(a)根据吞吐量为FFT处理器a选择核心数量和工作电压。(b)为FFT处理器a选择最能量最优的[N Vdd]集合。

cold room hot

图4.基于仿真模型的FIR滤波器在不同温度下的频率电压特性 .

所有配置。14字节内存的面积开销与系统面积相比可以忽略不计。此外,基于最新的闪存 技术[Flash‐控制器],,14字节闪存的功耗将处于纳瓦范围,因此与核心的功耗(毫瓦)相 比可以忽略不计。在实际设计系统中,例如考虑一个具有256核的系统,存储所有吞吐量下[ Nopt Vddopt coreopt]的全部配置所需的内存为32字节。

在第5节中,我们将基于芯片测量结果研究最小能耗架构的系统参数。我们还将比较采 用提出的方法(VS和自适应控制策略)构建的系统与仅具备VS功能的基准系统之间的能效。两种系统在使用电压调节器以生成目标电压时,都会产生面积和能耗损失开销。在当前比 较研究中,我们忽略这一开销,因为两个系统受到的影响相同。

实现细节

In本节将介绍我们原型ASIC芯片的实现细节。

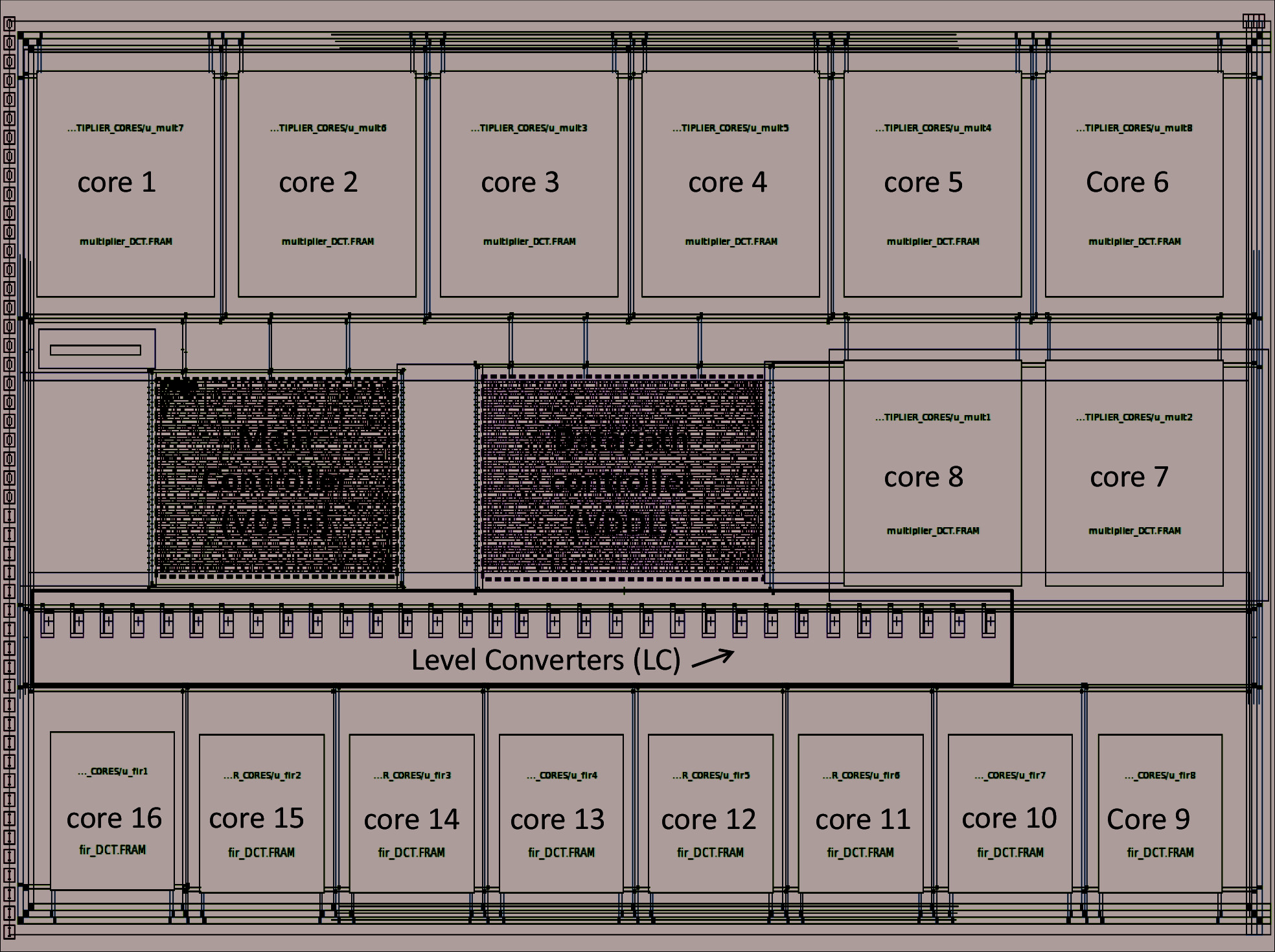

如图5所示,顶层芯片布局采用ARM标准单元库在90nm工艺下实现。芯片核心面积 为 580μm× 1000μm,整体芯片裸片尺寸为1.5mm2,包含焊盘单元。在七层金属层中, 五层金属层用于信号和时钟布线,最上两层用于电源和地。该芯片具有76个IO引脚用于接 口,并采用80引脚QFP封装进行测试。芯片的主要组件总结如下。

时钟管理

在设计该芯片的时钟分配网络时存在三个挑战。首先,为了准确测量每个核心的功耗,我 们需要确保在任何给定时间只有一个核心处于激活状态,这意味着所有其他非激活核心的 时钟应被关闭。我们采用了时钟门控技术来实现这一点。其次,由于90nm工艺IO库的限 制,无法将频率超过100MHz的片外信号引入芯片内部。为了能够在高于100MHz的频率 下测试所有核心,必须具备一种生成较高的片上稳定时钟频率的机制。为此,我们设计并 实现了片上的环形振荡器(ROs)。第三,为了在不同吞吐量下对每个核心进行表征,我 们

图5.包含所有16个核心的芯片顶层布局。

sho应在芯片上提供一系列可用的频率。出于这个原因,我们有 desi设计了一个4位可编程片上时钟分频器。

(a)时钟生成模块。我们使用标准单元库中的反相器设计了标准单元环形振荡器( S‐RO)。通过与非门单元对S‐RO进行门控,从而在不使用时节省动态功耗。在仔细研究仿真结果并考虑所需频率范围后,实现了包含15、25、33和43个反相器的4个S‐RO。这些 S‐RO在给定芯片工作电压(Vdd)下产生固定频率信号。如果芯片的供电电压升高,则 S‐RO产生的频率将随之升高,反之亦然。

(b)可编程时钟分频器。我们使用标准单元设计了可编程时钟分频器。有四个引脚用于 设置分频系数。通过该设计,可对外部片外时钟或片上S‐RO时钟进行如下分频:1、2、3、 4、6、8、12、16、24、32、48、64、96、128、192和384。将此模块与时钟生成模块集 成,能够灵活地产生广泛的片上稳定时钟频率。

控制器

The该芯片中有两个主要控制器,分别在两个不同的电压域中运行 .

(1)主控制器。如图5所示,主控制器位于与芯片核心不同的电压域中,以确保控制器 始终在标称电压(VDDH)下工作。主控制器为所有核心提供控制和数据接口。尽管芯片 上的接口运行在低速下,但每个核心都能够以高速运行(FIR滤波器可达850MHz)。因此, 我们在芯片中创建了两个时钟域:慢速时钟域用于接口逻辑,快速时钟域用于核心。

(2)数据路径控制器。该控制器在任何给定时间与核心工作在相同的电压域(VDDL) 中。例如,如果核心在0.45伏下运行,则该控制器也在0.45伏下运行。该控制器负责通过 两级反相器组装32位数据以与核心接口。此外,该控制器还从核心收集32位数据,并通过 电平转换器(LC)将其发送到主控制器。

电平转换器(LC)

我们基于Wooters等人[2010]设计了32个定制的电平转换器。图5中标出了32个LC。 LC用于将来自VDDL电压域的信号与VDDH域进行接口连接。

同构核心

我们实现了两种不同功能的核心:16位乘法器核心和8位FIR滤波器。乘法器核心为完全组 合设计,而FIR核心采用流水线结构。本文中我们仅展示FIR的结果,乘法器的研究留待未 来工作。8位FIR核心的布局面积为 100μm× 100μm。在综合、验证、单元布局和布线完 成后,我们将一个FIR核心构建成一个宏单元。这样,所有8个FIR核心将完全相同,仅控 制器的接口信号除外。这是设计同构多核系统时任何设计者所能达到的最佳效果。每个核 心均可通过3位模块选择引脚单独启用。每个核心连接至VDDL电压域,该电压域通过输入/ 输出上的电源引脚进行控制。VDDL可从近阈值(或FIR的截止电压)调节至标称电压。

测试设置

在本节中,我们将描述用于20个封装芯片中所有核心的测试方法。随后,我们将讨论表征开销。

测试设置如图6(a)所示。该设置包括一个带有国家仪器公司(NI)VHDCI连接器接口 的PCB板,连接至NIPCI‐6552板[National‐Instrument]。系统还包括Labview软件 (PC)、用于测量功耗的示波器以及三个电压源。其中一个电压源用于输入/输出(2.5V), 一个用于主控制器(VDDH)(1.2V),另一个用于选择核心电压(VDDL)。专用集成 电路芯片插入板上的零插拔力插座中。使用LabVIEW波形编辑工具生成输入激励,然后 通过通过PCI‐6552板连接的VHDCI连接器将输入激励发送到芯片。Labview软件还用于 监控来自芯片的信号。利用此设置,我们对所有核心进行性能和功耗测量。之后,我们还 将介绍用于进行温度变化分析的设置。

功能测试与速度测量

每个核心均通过在从标称电压到其截止的工作电压范围内进行测试来 实现功能验证

测试设置。(b)温度变化腔室设置)

测试设置。(b)温度变化腔室设置)

图6.(a)测试设置。(b)温度变化腔室设置。

电压。在每个工作电压下,测量核心能够运行的最高频率。我们使用片上S‐RO时钟来测试 每个核心的功能。稍后在第5节中,我们将展示这些片上频率的范围。此外,对所有8个核 心重复执行类似的过程。工作电压以50mV步进进行调整。

功耗测量

使用示波器,在不同工作电压下测量所有核心的功耗轨迹。通过 Labview软件向芯片发送不同的输入激励来测量功耗。在当前的原型中,未实现电源门控。因此,所有核心的漏电功耗已集成到动态功耗测量中。对于90nm节点,漏电功耗也非常 微小,因此核心之间的漏电功耗变化可以忽略不计。

温度测量

为了基于环境温度变化对这款芯片进行分析,我们使用了ESPEC SH‐241型号[ESP]。测试设置如图6(b)所示。该温控箱可提供的温度范围为−40◦C至150◦ C。然而,连接PCI板与芯片的VHDCI连接器电缆仅可在0◦C至 55◦C范围内工作。这限制了 我们的温度变化分析范围在5◦C至 50◦C之间。我们采用前文所述的相同方法,采集所有核 心在两个不同温度T0(5◦C)和T1(50◦C)下的功耗和频率特性。在第5.6节中,我们将基 于在室温下选定的配置,展示温度变化对能效的影响。

表征开销与可扩展性

当前原型包含8个核心,因此对20个芯片的所有核心进行一 次性表征并不耗时。使用10种不同的测试模式测试全部8个核心时,每个芯片需要14080 (10种测试模式×4个时钟周期×11种电压×8个核心×4种时钟设置)个时钟周期。假设平均时钟速度为200MHz,则总校准时间为 70 μ秒。目前的表征假设所有核心采用 串行测试。通过并行化校准过程可以进一步优化,从而减少时间开销。然而,这仍然是一 次性过程。

在核心数量较多的情况下,例如数百个核心,通过运行功能模式对每个核心进行单独 表征可能会变得具有挑战性且费力。此外,基于不同环境温度对核心进行表征也极不切实 际。作为替代方案,我们可以在每个芯片内实现环形振荡器(ROs)。我们可以利用环形 振荡器频率的差异来校准核心速度的变化[Nikolic和Pang 2006]。此外,使用EKV模型, 我们可以从标称电压到近阈值区域快速而准确地表征电路的速度、动态功耗和漏电功耗[ Rafeei等人 2013],从而加快一次性表征的过程。在本研究中,我们的目标不是减少校准 时间,而是评估工艺变异(PV)对片内和片间同构核心的影响。由于我们单个芯片上仅有 8个核心,因此采用了手动校准方法。未来,我们建议在每个核心中集成环形振荡器用于校 准目的。

结果

本节总结了各种实验的结果及我们的分析。

我们首先展示了20个封装芯片上可用的片上时钟频率范围以及这些时钟的百分比变化。随后,我们将展示所有芯片在不同期望吞吐量下实现的[Nopt Vddopt]元组的结果。这将帮 助我们深入了解每个芯片所选择的核心总数(芯片间差异)以及针对不同吞吐量所选择的 具体核心[coreopt](芯片内差异)之间的差异。

芯片上可用的频率范围

四个S‐RO(SC0、SC1、SC2、SC3)结合16种可编程分频器的选择,可生成从2.5MHz到 980MHz的频率范围,如图7(a)所示。SC0是最快的时钟,具有15级反相器级数,其次是 SC2(23级)、SC3(33级)和SC4(43级)。这些时钟随后用于测试每个核心的功能。此外,我们在20个芯片上测量了S‐RO的频率。由于片间PV效应,由S‐RO生成的频率在不 同芯片之间会有所差异。20个芯片中SC2时钟测得的频率变化如图7(b)所示。在标称电压 下,由于工艺变异(PV),与平均频率相比存在60MHz(17%)的变化。如果排除异常 值,则20个芯片之间的时钟频率变化为5%。

芯片0上的片上时钟频率范围。(b)显示从20个芯片的片上SC2时钟测得的频率的直方图)

芯片0上的片上时钟频率范围。(b)显示从20个芯片的片上SC2时钟测得的频率的直方图)

图7.(a)芯片0上的片上时钟频率范围。(b)显示从20个芯片的片上SC2时钟测得的频率的直方图。

速度和功耗测量

在本节中,我们将分析所有核心在标称电压下的速度和功耗变化。对所有20个芯片(160个 核心)的8个核心在多个工作电压下进行了功能验证,直到它们失效为止。记录每个核心的 最高工作频率。图8(a)显示了在标称电压下测得的所有160个核心的最高频率分布。在标称 电压下测得的标准差为68.5MHz(相对于平均值的7%)。在低电压下观察到高达26%的 更大变化,为简洁起见未予展示。

类似地,我们绘制了所有160个核心在50MHz工作频率下的功耗,如图8(b)所示。观 察到标准差为0.25毫瓦(相对于均值的54%)。我们在不同的工作电压下也观察到类似的 趋势。这表明,在我们的芯片中,工艺变异(PV)对功耗的影响比对速度的影响更为显著。因此,[Nopt Vddopt]在不同吞吐量下的元组将有很大差异。我们将在下一节中介绍此分析。

显示20个芯片(160个核心)中所有核心测得的频率直方图。(b)显示20个芯片(160个核心)中所有核心测得的功耗 直方图)

显示20个芯片(160个核心)中所有核心测得的频率直方图。(b)显示20个芯片(160个核心)中所有核心测得的功耗 直方图)

图8.(a)显示20个芯片(160个核心)中所有核心测得的频率直方图。(b)显示20个芯片(160个核心)中所有核心测得的功耗 直方图。

选择 [NoptVddopt]

在本节中,我们对在不同期望吞吐量范围内为多个芯片选择的最小能耗架构[Nopt Vddopt] 进行了分析。五种不同芯片在若干吞吐量下所选择的[Nopt Vddopt]元组集合列于表II中。例如,在芯片编号15(最后一行)中,实现

表II.不同芯片在期望吞吐量范围MHz–2.5GHz内选择的[Nopt Vddopt]元组集 合[0–19]

| 吞吐量(MHz) | |||||

|---|---|---|---|---|---|

| 芯片ID | 100 | 400 | 600 | 1000 | 2500 |

| 芯片‐0 | [1 0.55] | [1 0.55] | [2 0.55] | [4 0.55] | [8 0.55] |

| 芯片‐3 | [1 0.40] | [1 0.55] | [2 0.50] | [4 0.50] | [8 0.50] |

| 芯片‐5 | [1 0.65] | [1 0.65] | [1 0.65] | [2 0.65] | [4 0.65] |

| 芯片‐10 | [1 0.50] | [2 0.50] | [1 0.65] | [2 0.60] | [8 0.55] |

| 芯片‐15 | [1 0.45] | [1 0.55] | [4 0.45] | [2 0.60] | [4 0.65] |

期望吞吐量为100MHz至300MHz时,能效最高的架构是单核以0.45伏运行。然而,当需要实现400 MHz的吞吐量时,单核在0.45伏下已无法满足需求,因此电压需提升至0.55伏。在0.45伏电压下,四核以500兆赫至600兆赫运行时能量效率最高。

在图9中,我们绘制了所有芯片在整个期望吞吐量范围内选择的Nopt的等高线图。从图 9可以看出,能效架构的变化,即从单核到双核、四核再到八核的转变,在所有芯片中并不 一致。这表明了片间工艺变异对每个芯片内部核心特性的影响。例如,在芯片编号5中,其 中一个核心非常快速且功耗高效,能够满足9种不同的吞吐量需求。而与此同时,芯片编号 15中有多个核心较慢。

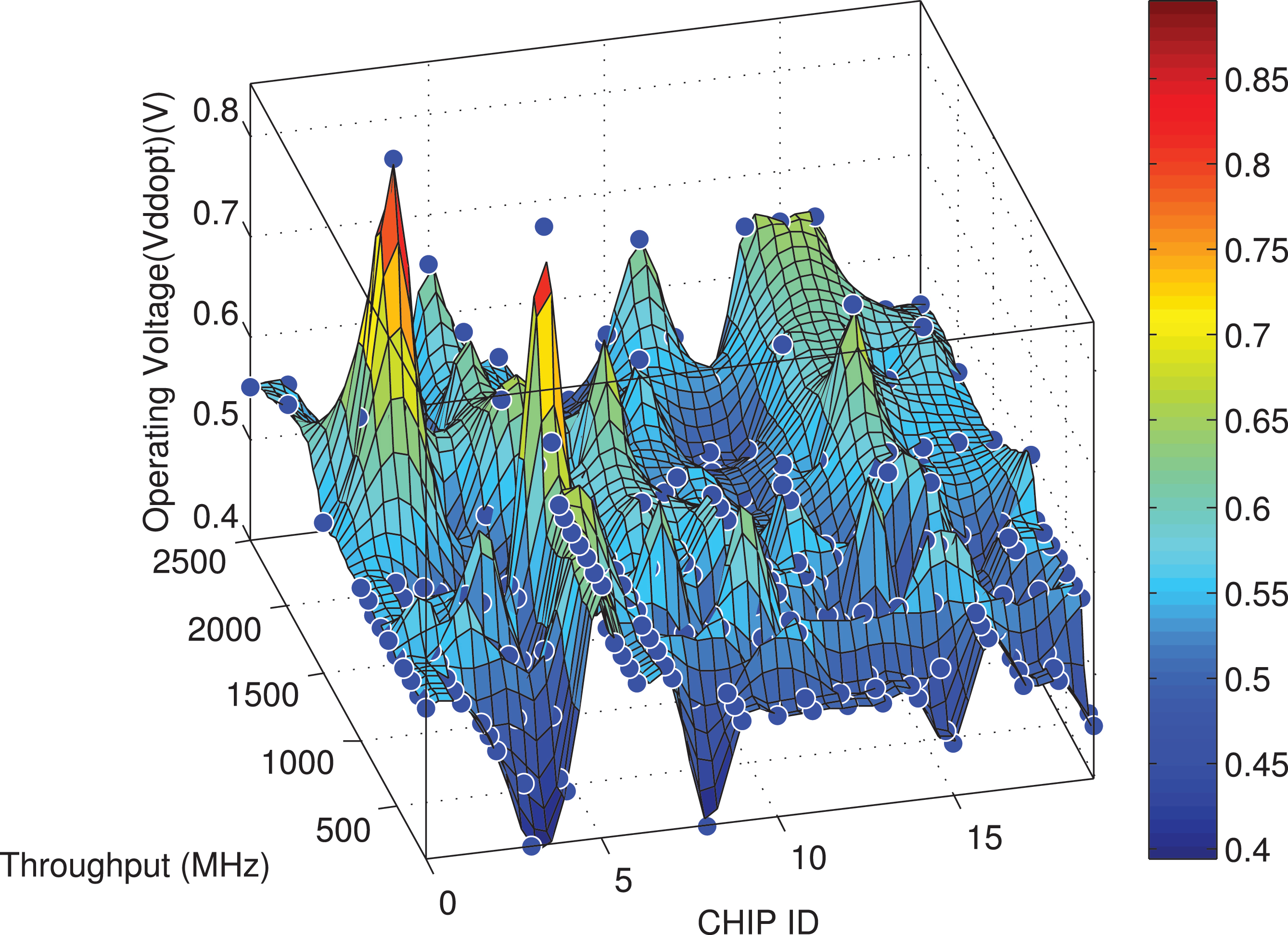

此外,表II还显示了不同芯片在少量期望吞吐量下选择的Vddopt 。我们在图10中绘制 了所有芯片所选的Vddopt的曲面图,以分析这种差异。从图和表中可以得出结论:由于芯 片间差异,每个芯片内各个核心的特性彼此不同。因此,为实现相同期望吞吐量而选择的 能效架构在不同芯片上也会不同。例如,从表II可以看出,在实现600兆赫的期望吞吐量 (第3列)时,芯片0将选择在0.55伏下运行的双核,而芯片15则会选择在0.45伏下运行的 四核,以实现最大能效。

此外,我们将观察到,为了使许多芯片在整个动态范围内以能量高效的方式运行整个系统,我们只需 要少数几个工作电压

图9.Nopt由不同芯片[0–19]在期望吞吐量范围[100MHz–2.5GHz]内选择。

图10.Vddopt由不同芯片[0–19]在期望吞吐量范围[100MHz–2.5GHz]内选择。

接近阈值电压。从表II可以看出,芯片编号10需要0.5V、0.55伏、0.6V和0.65伏四个电压。通过我们的架构,系统可以使用四个专用电压构建。还可以进一步分析那些最佳电压超过 四种但被迫仅使用四种选择的芯片的效率损失。在

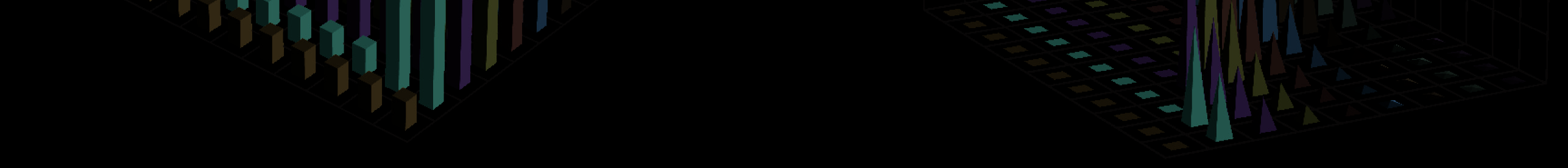

Fig. 11.核心数量coreopt在不同的芯片上,从8个核心中选择,覆盖广泛的吞吐量范围 [100MHz–2.5GHz]

在当前分析中,该算法提供了以50mV步进自由选择任意电压的灵活性。

选择[核心opt]

在本节中,我们对20个芯片在不同期望吞吐量下的coreopt进行了分析。如图11所示,在 100MHz至2GHz的吞吐量范围内,大多数架构使用1、2或4个核心。每个芯片上共有8个 核心可用。理想情况下,所有核心的速度和功耗特性应相同,因此对于单核架构而言,从 8个核心中选择任意一个都不应改变系统行为。双核和四核架构也类似。然而,由于片内工 艺变异,这些核心在制造完成后不再具有同质性,其特性各不相同。

图11展示了部分芯片在所有期望吞吐量下的核心opt。图中标记的圆圈表示激活的核心。图中还显示了激活核心的工作电压。需要注意的是,在我们的设计中,为了简化设计,我们 考虑所有核心采用相同的工作电压。图11揭示了片内工艺变异对同构核心影响的一个有趣现 象。因此,在选择能效最高的架构时,确定核心opt也非常重要。这也突显了一次性完成的 表征过程的重要性。为实现系统的最大能效,必须对每个核心进行仔细且严格的表征。该表 征过程也可以每隔5年或10年启动一次,以重新校准[Nopt Vddopt核心opt],并纳入老化效应 的影响。

节能

在本节中,我们展示了采用所提出的VS与ACS混合方法相较于仅具备VS功能的基准系统所获得的节 能结果。

图12.在低负载(10MHz–300MHz)、中等负载(400MHz–800MHz)和高负载(900MHz–2.5GHz)环境下,与BASE相比的节能情况。

基准系统采用芯片上最大可用数量的8个核心构建,而混合系统可选择使用1、2、4或8个核心 来构建系统。基准系统采用电压调节技术以满足目标吞吐量并降低能耗。混合系统将优化[N opt Vddopt coreopt]以满足目标吞吐量。两个系统均可使用具有50mV步进的相同电压。

图12展示了在20个芯片样本的不同工作负载环境下,混合系统相对于基准系统的节能 情况。平均而言,在低负载(10兆赫‐300兆赫)、中等负载(400兆赫‐800兆赫)和高负载 (900兆赫‐2.5吉赫)环境下,混合方法相比基准系统分别节能28.15%、19%和6.27%。在 低吞吐量负载下,混合方法相较于简单VS的节能效果更为显著。这主要是因为混合方法可 以根据可用电压和所需吞吐量选择使用1个、2个、4个或全部8个核心。在低负载环境下, 所需的最佳核心数量少于芯片上的最大可用数量。因此,与基准系统相比,混合系统在低 或中等负载环境下的节能效果更高。然而,在高负载环境下,混合系统和基准系统都可能 需要使用芯片上全部8个核心以满足吞吐量需求,因此混合系统相比基准系统的节能效果相 对较低。在工作负载变化且较长时间段内处于低负载的应用场景中,相比仅具备电压调节 能力的基准系统,混合系统将具有显著优势。

图1 3.在50兆赫频率下测量芯片3的消耗总功率的核心分布 an o工作电压为0.45伏。

芯片3和(b)芯片5中所有核心在50MHz频率和0.65伏工作电压下测得的平 均总功耗)

芯片3和(b)芯片5中所有核心在50MHz频率和0.65伏工作电压下测得的平 均总功耗)

图14.在低温(T0)和高温(T1)条件下,(a)芯片3和(b)芯片5中所有核心在50MHz频率和0.65伏工作电压下测得的平 均总功耗。

温度变化分析

在本节中,我们分析了温度变化对核心特性的影响,并研究了系统能效随温度变化的情况。

根据第4.5.3节中总结的设置,我们测量所有核心的总功耗。随后,为了研究核心的分 布情况以及温度变化的影响,我们绘制了在不同温度下(低温(T0:5◦C)、室温(23◦C) 和高温(T1:50◦C))测得的芯片3中所有核心的平均总功耗的中位数(μ)和标准差(σ)。图13显示了该分布情况。从图中可以看出,随着温度升高,核心的总功耗降低,因此分布 向左移动。类似地,当温度降低时,漏电功耗增加,从而导致总功耗增加,这使得相对于 室温的分布向右移动。我们基于芯片结果对温度变化所做出的观察与Calhoun和 Chandrakasan[2006]中提出的结果相似。在当前设置中,低温与室温之间的差异为18◦ C,而高温与室温之间的差异为27◦C。

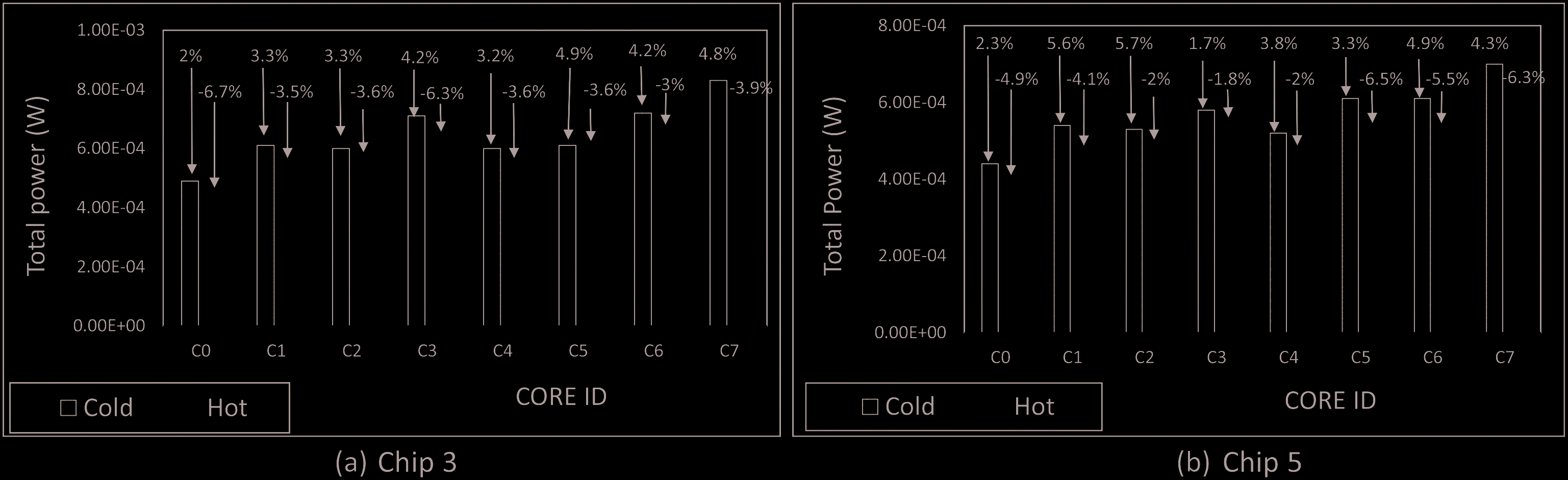

我们还评估了同一芯片内核心温度变化的影响。例如,图14(a)显示了在0.65伏电压下, 芯片3中所有核心在两种温度设置T0和T1时消耗的总功率的变化情况。从图中可以看出,不 同核心的功耗变化各不相同。我们首先研究T0温度相对于室温下的变化情况。例如,核心 0(C0)消耗的总功率变化为2%,而核心7(C7)的变化为4.8%。同样,在T1温度下,不 同核心的功耗变化也不同。例如,与它们在室温下的功耗相比,C0的功耗 C7的功耗降低3.9%。尽管温度影响对各个核心的影响不同,但它们之间的差异相当小,大 约在1%–3%之间。

为了研究芯片到芯片温度变化的影响,我们在相同设置下测量了芯片5消耗的总功率, 即50MHz频率和0.65伏工作电压。结果如图14(b)所示。从图中可以看出,不同芯片受到的 影响各不相同。例如,考虑温度降低(T0)的情况,芯片3中的C3经历了4.2%变化,而在 芯片5中仅经历1.7%变化。类似地,在温度升高(T1)情况下,芯片3中显示‐3.9%变化的 C7,在芯片5中则经历‐6.3%变化。

温度升高也会导致频率降低。同样,温度降低将导致频率升高。我们在第5.1节中总结 了用于测量核心可达到的最大频率的当前设置。由于核心频率较高,我们受限于使用片上 RO时钟和可编程分频器,因此芯片上可用的频率是离散的,如图7(a)所示。最小的可用频 率变化为10%(40MHz)。在当前18◦change(T0)以及 27◦change(T1)的设置下,我 们未观察到频率发生变化。这可能是因为变化小于10%,在当前设置限制下难以捕捉。尽 管如此,核心仍在室温设置下确定的频率下运行。

我们还研究了温度对系统在不同吞吐量下能效的影响。这将导致能效的损失或增益。为此,针对每个目标吞吐量以及推导出的最优配置[Nopt Vddopt coreopt],我们计算系统在 T0(5◦℃)和T1(50◦℃)下消耗的能量。芯片3和芯片5在两种不同温度下相对于室温的能 耗差异如图15所示。我们在三种工作负载环境下评估能量差异:低负载( 10MHz‐300MHz)、中等负载(400MHz‐800MHz)和高负载(900MHz‐2.5吉赫)。

从图中可以看出,在T0(低温)条件下,与室温相比,在不同工作负载环境下消耗的 总能量会更多。这表明,如果系统采用基于室温设置获得的配置,则在不同工作负载环境 下,消耗的总能量将比室温条件下分别增加4.42%、3.68%和4.47%。这些差异

图15.芯片3和芯片5在低负载(10MHz–300MHz)、中等负载(400MHz–800MHz)和高负载(900MHz– 2.5GHz)环境下,T0和T1温度相对于室温的消耗总能量差异。

表III.混合方法设计在90纳米和45纳米技 术下相对于BASE的节能情况。[Srivastav等 2013]。

| 动态环境 | 能量 节能 | 90nm | 45nm |

|---|---|---|---|

| 10.1%–43.5% | 32.5%–71.1% |

芯片5的数值略小。同样,在T1(高温)下,系统将获得更高的能效,因为核心的漏电功 耗会因温度升高而降低。因此,从图15中可以看出,在不同工作负载环境下,芯片3的能 耗分别减少了4.2%、4.58%和3.4%。

在给定情况下,当温度降低时能效损失(4%)并不显著。然而,随着温度进一步降低, 能效将进一步恶化。与此同时,核心的运行速度将快于室温下测得的速度。可以进一步研 究通过重新配置是否能够恢复能效。例如,如果室温下的配置建议为[40.65V],,则可分析 通过减少核心数量或在低电压下运行是否能够提升能效。换句话说,系统应进行重新配置 以实现最优能量运行。

同样,当温度升高(T1)时,能效得到提升,即核心的功耗降低。然而,随着温度进 一步升高,核心的工作频率将下降。超过某一阈值后,核心将无法满足吞吐量需求。例如, 在室温下系统配置建议[40.65V],,但当温度超过一定限度时,四核在0.65伏工作电压下将 因温度升高而无法满足吞吐量要求。在这种情况下,必须增加核心数量或提高工作电压。换句话说,系统应重新配置以满足所需的吞吐量。此外,还需要评估在不同温度下保存系 统配置所带来的开销,以及对温度变化进行表征和检测的机制。这项研究将留作我们的未 来工作。

技术趋势及其影响

在本节中,我们将讨论所提出的方法随着工艺节点缩小的可扩展性。

随着技术的缩小,工艺变异性增加[维尔恩舍费尔 2013],其在近阈值电压下的影响更 加显著。随着工艺变异(PV)影响的增大,核心之间的特性差异也将增加。换句话说,将 观察到核心特性具有较高的方差。因此,调度器在选择能够满足目标吞吐量要求的最高效 核心之前,分析工艺变异性(PV)的影响将变得越来越重要。

表III展示了在动态工作负载环境下90纳米和45纳米节点的类似观察结果[Srivastav等 2013]。这再次表明,工艺变异感知方法论(例如本文提出的方法)将比BASE更有效率, 并且随着技术节点的缩小,其相对于BASE的效率将进一步提高。

由于代工厂的限制,我们选择了90纳米工艺节点进行芯片制造。尽管90纳米技术的工 艺变异性相对较低,但在近阈值工作电压下的影响仍不可忽略。这为验证我们在构建工艺 偏差感知的高能效架构方面的想法和方法论提供了一个良好的平台。

结论与未来工作

在本文中,我们验证了一种节能方法的有效性,该方法在表征阶段根据工艺偏差效应和期 望吞吐量预先选择核心数量及其工作电压。验证是通过在90纳米IBM工艺下制造的8核 FIR设计完成的。在0.9伏和0.55伏时,观察到各核心之间的频率变化分别高达7%和26%。由于工艺偏差,不同的芯片需要不同的核心数量和不同的电压来满足相同的吞吐量。尽管90纳米工艺的工艺变异性相对较低,但在接近阈值的工作电压下,其影响不可忽 略。这为验证我们构建考虑工艺偏差的能效架构的思想和方法论提供了一个良好的平台。此外,与采用电压调节以满足不同吞吐量需求的基准系统相比,节能最高可达28%。在片 外直流‐直流转换中,为了获得所需的工作电压会产生一定的能效损失,而我们在分析中未 考虑这一因素。然而,这种情况在电压调节方法和我们提出的方法中均普遍存在。

我们还展示了温度变化对核心特性在速度和功耗方面的影响。基于芯片在不同环境温 度下的测量结果,我们评估了温度变化对能效架构配置的影响。如果系统基于室温设置进 行配置,我们观察到当温度发生18◦变化时,系统的能效将损失约4%。

在测试原型芯片时,发现了设计中的许多不足之处。例如,通过运行所用模式对手动 校准核心的方法不具备可扩展性。在不同的工作电压和各种温度设置下测量每个核心的频 率和功耗,可能是一项费力的任务。有必要研究在每个核心中使用环形振荡器(RO)等电 路,以代表该核心的速度和功耗。此外,还需要研究校准工艺变异(PV)对环形振荡器 (RO)的影响,使其能够代表工艺变异(PV)对核心的影响。

多核DSP低功耗优化设计

多核DSP低功耗优化设计

1026

1026

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?