碳纳米管场效应晶体管在高速亚阈值条件下工作的超低功率应用设计

R. Marani1和 A. G. Perri 2,z

1意大利国家研究委员会(CNR),先进制造智能工业技术与系统研究所(STIIMA),巴里 70125,意大利

2巴里理工大学电气与信息工程系电子器件实验室,巴里 70125,意大利

本文旨在对用于超低功耗应用的在亚阈值区工作的碳纳米管场效应晶体管(CNTFETs)的行为进行仿真。特别地,我们提出了一种基于碳纳米管场效应晶体管的SRAM单元设计,并采用我们先前提出的碳纳米管场效应晶体管模型。为了进行比较,同样的设计流程被应用于基于CMOS技术的SRAM单元表征,其中我们使用了ADS库中的BSIM4模型。特别是通过参数化仿真调整MOSFET参数,以获得与碳纳米管场效应晶体管性能相当的MOSFET模型性能。© 2019年 电化学学会。[DOI: 10.1149/2.0201910jss]

手稿于2019年9月9日收到。2019年10月7日发表。

引言

碳纳米管(CNTs)是一种有前景的材料,可用于低功率应用和低电阻互连。特别是碳纳米管具有高载流子迁移率以及可能的金属或半导体特性,可广泛应用于电子领域,例如作为晶体管的沟道。

基于碳纳米管的场效应晶体管即为碳纳米管场效应晶体管。因此,碳纳米管场效应晶体管是纳米技术中一种新兴的纳米级器件,具有固有的性能优势以及优异的机械、化学和电学性能。

特别是类MOSFET的CNTFET被用于高性能和低功耗存储器设计,因为这种器件具有显著更小的关断电流,可大幅降低碳纳米管场效应晶体管的关态功耗。7–8针对该器件,我们已提出一种紧凑型半经验模型2,8,并引入了一些改进,以方便在SPICE和Verilog‐A中实现。随后,我们的模型被用于对模拟和数字电路进行静态和动态分析。9–11

本文研究了碳纳米管场效应晶体管在亚阈值区工作时的特性,以用于超低功耗应用。特别是,我们使用我们的模型对基于碳纳米管场效应晶体管的SRAM单元进行了仿真。

然后,为了进行比较,采用相同的设计流程来表征基于CMOS技术的SRAM单元,其中我们使用ADS库中的BSIM4模型。特别是通过参数化仿真对MOSFET参数进行调整,以获得与CNTFET性能相当的MOSFET模型性能。

本文的结构安排如下。首先,我们简要介绍我们的碳纳米管场效应晶体管模型12–14,然后设计基于碳纳米管场效应晶体管和CMOS技术的SRAM单元结构。接着展示所提出的SRAM单元设计的仿真结果,重点比较其在性能和功率损耗方面的表现。最后,我们讨论相关结果,并给出结论与未来发展。

我们碳纳米管场效应晶体管模型的简要回顾

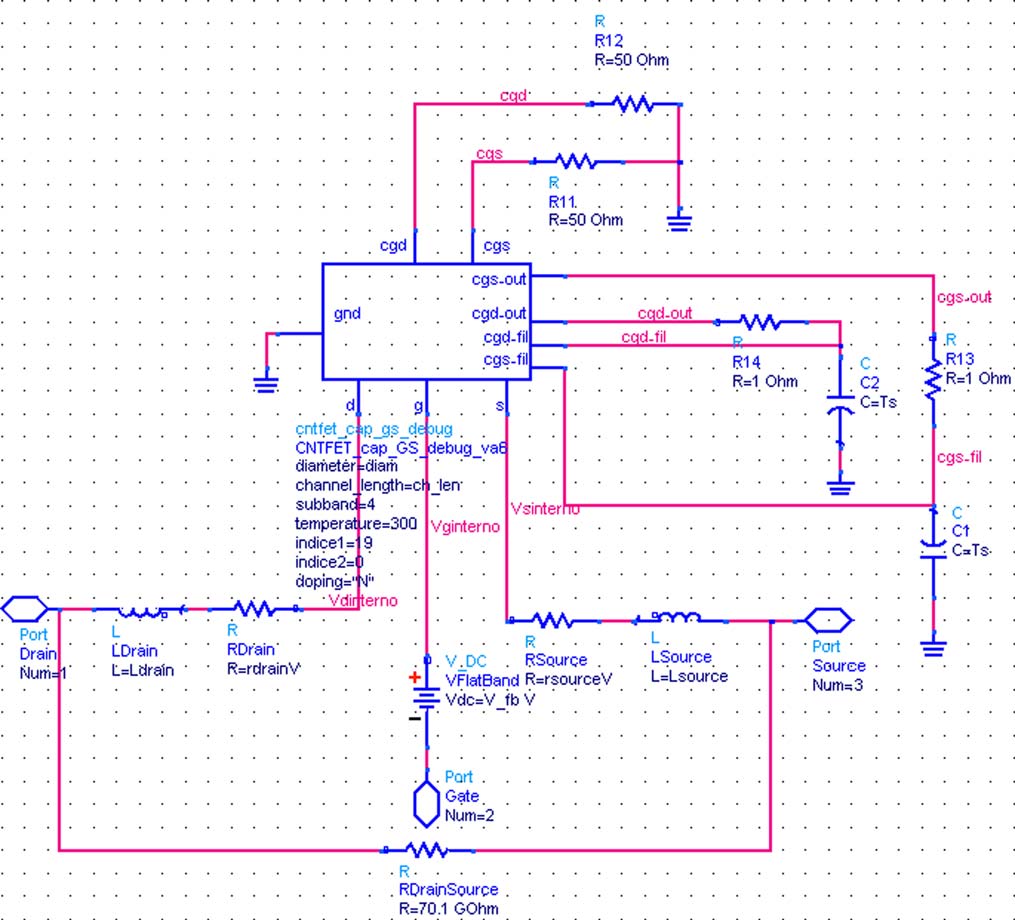

我们的直流模型的详尽描述见参考文献2至14。因此,建议读者查阅这些参考文献。该模型是一个紧凑型半经验模型,可直接且方便地在仿真软件中实现,用于设计模拟和数字电路:实际上,模型中最复杂的部分包含在Verilog A中。特别是所使用的软件为高级设计系统(ADS),其也采用Verilog A编程语言。我们考虑了单壁n型碳纳米管场效应晶体管,并基于弹道输运假设。该假设使得我们能够定义碳纳米管电流的解析公式。

当在栅源之间施加正电压 VGS 时,沟道起始处的导带降低 qVCNT,其中

q 是电子电荷,VCNT是表面势,其表达式见我们的参考文献12至14。

假设每个子带在整个沟道长度上均匀减小,总漏极电流可表示为:15

$$

I_{DS} = \frac{4qkT}{h} \sum_p [\ln(1+ \exp \xi_{Sp}) - \ln(1+ \exp \xi_{Dp})]

$$

其中,k 是玻尔兹曼常数,T 是绝对温度,h 是普朗克常数,p 是子能带数量,而 ξSp和 ξDp则通过子能带能隙随温度变化,其表达式见参考文献2。

为了获得被测器件的直流特性,我们参考了32纳米技术的p型碳纳米管场效应晶体管。此外,器件直径为1.5纳米,手性指数为(19, 0),并考虑了4个子能带。

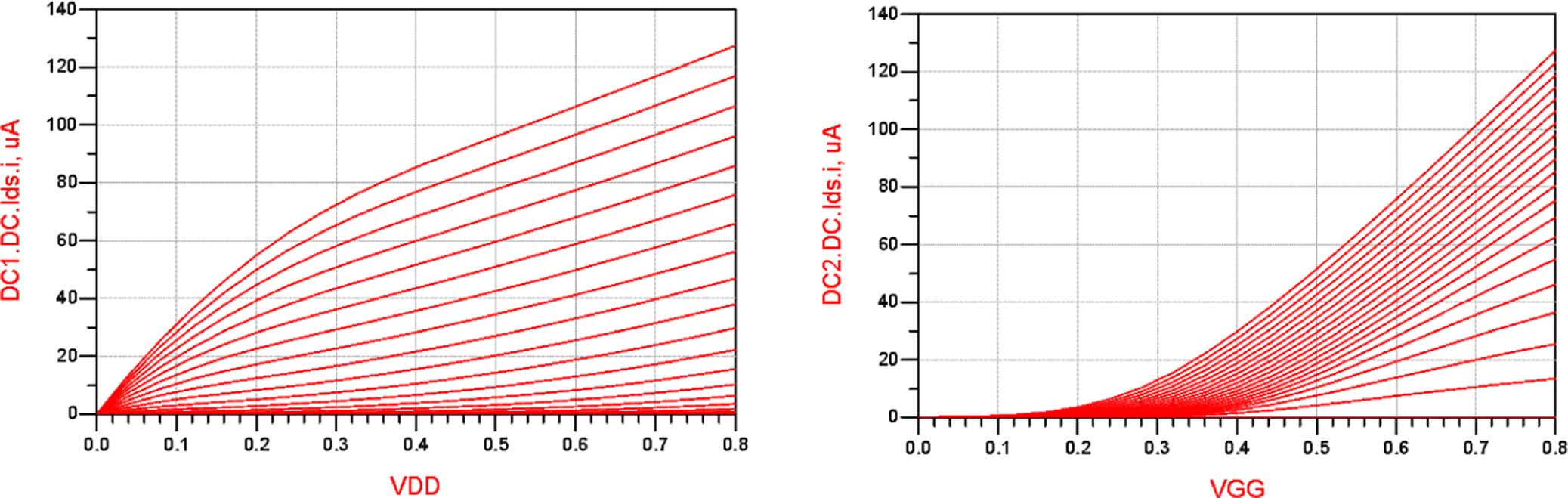

在图3中,我们给出了所模拟的碳纳米管场效应晶体管的 IDS 与 VDS(表示为VDD)以及 IDS 与 VGS(表示为VGG)的特性。

此外,进行了两次直流分析:直流1和直流2。在直流1分析中,VGS从0伏特变化到0.8伏特,步长为0.04伏特。在直流2分析中,VDS电压也从0伏特变化到0.8伏特,步长为0.04伏特。

BSIM4模型

BSIM(伯克利短沟道IGFET模型)16指的是一系列用于集成电路设计的金属氧化物半导体场效应晶体管模型。

在本研究中,BSIM4模型已用于45纳米工艺节点。然而,它也兼容0.13微米、90纳米、65纳米、23/28纳米和22/20纳米工艺节点。此外,BSIM4模型适用于电路仿真和CMOS技术开发。

用于仿真以下章节中描述的基于CMOS的6T单元SRAM的模型,正是ADS库中提供的BSIM4模型。

通过设置模型的适当参数,可以将PMOS转换为NMOS,反之亦然。

在这种情况下,图4中表示的是伯克利短沟道IGFET模型 NMOS 符号。

通过参数仿真对NMOS和PMOS的参数进行了调整,以获得与碳纳米管场效应晶体管模型性能相当的金属氧化物半导体场效应晶体管模型性能。

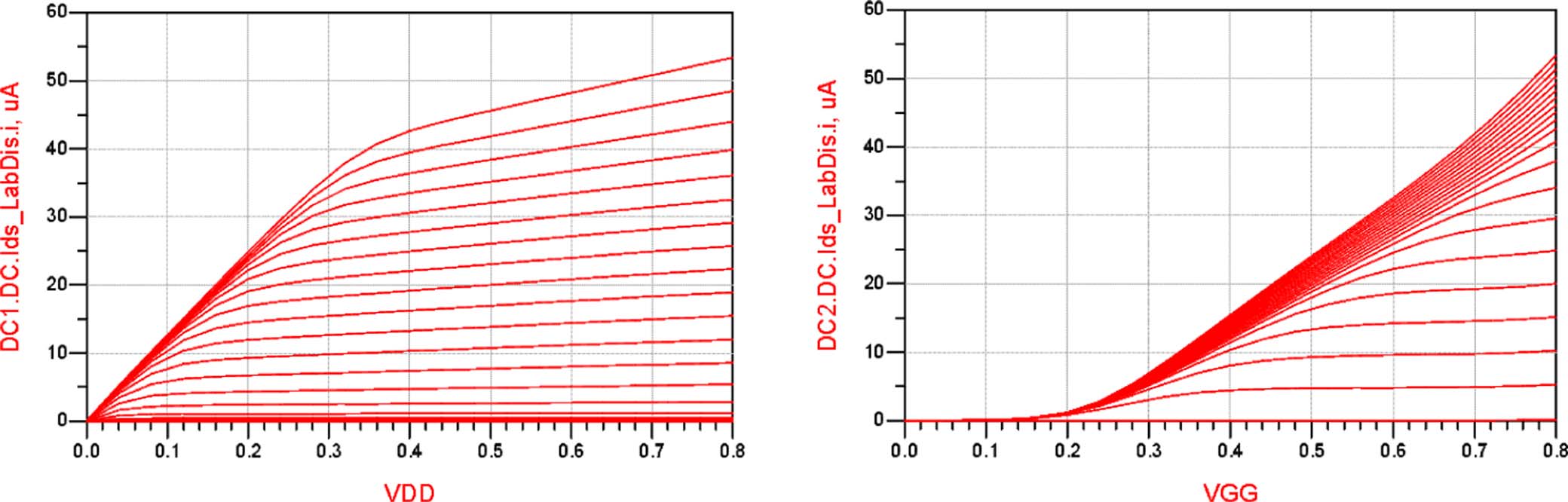

在图5中显示了所模拟的N型金属氧化物半导体的 IDS 与VDS (表示为电源电压)以及 IDS 与VGS (表示为栅极电压)特性。

同样在此情况下进行了两次直流分析:直流1和直流2。在直流1分析中,VGS从0伏特变化到0.8伏特,步长为0.04伏特。在直流2分析中,VDS电压也从0伏特变化到0.8伏特,步长为0.04伏特。

实验设置与方法

基于碳纳米管场效应晶体管的静态随机存取存储器单元的设计

现代片上系统(SoC)中有相当大一部分由静态随机存取存储器(SRAM)占据,因其具有更高的速度和更低的功耗。

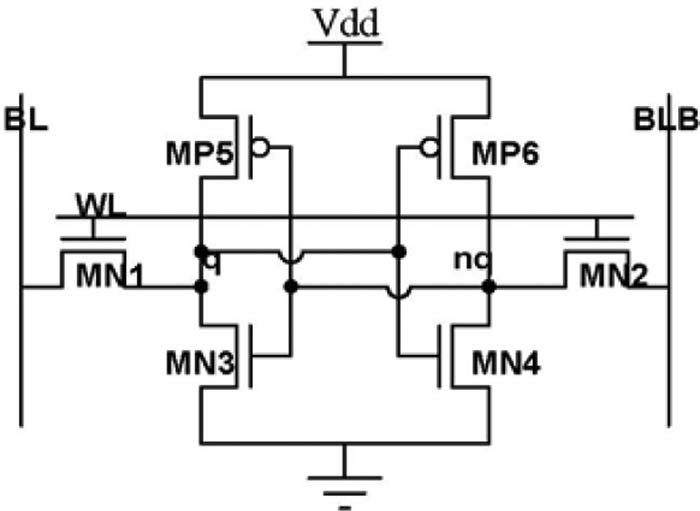

一种基于碳纳米管场效应晶体管技术的六晶体管静态随机存取存储器单元结构如图6所示。

静态随机存取存储器由四个晶体管组成,形成两个交叉耦合反相器,用于存储一个存储位。交叉耦合反相器的两个输出表示两种稳定状态“0”和“1”。另外增加两个访问晶体管,用于在读写操作期间控制对交叉耦合反相器的访问。因此,存储一个存储位需要六个晶体管。字线(WL)作为栅极电压控制访问晶体管MN1和MN2,将两个反相器的输出连接到两条位线。这些位线用于从存储单元读取存储的数据或将新数据写入存储单元。

写操作 .— 写周期的开始是将要写入的值及其互补信号施加到位线上。为了写入‘0’,需将‘0’施加到位线BL,同时将其互补信号‘1’施加到。反之,为了写入‘1’。然后使WL变为高电平,待存储的值被锁存。

读操作 .— 通过使能字线WL来启动读周期,从而开启两个访问晶体管M5和M6。第二步是将存储在D中的值通过M1和M6传输到位线BL和上。在BL侧,当D中存储的是“1”时,晶体管M4和M5会将位线拉向电源电压。如果存储器中的内容为0,则情况相反,将被拉向1,而BL被拉向0。

空闲状态 .— 在空闲状态下,字线未使能,访问晶体管M5和M6将单元与位线断开。只要两个交叉耦合反相器与任何外部电路断开,它们将继续相互增强。

在以下仿真中,对于所有碳纳米管场效应晶体管,我们假设沟道长度为32纳米,MN1、MN2、MN3和MN4的晶体管宽度W为64纳米,MP5和MP6的晶体管宽度W为80纳米,以便与参考文献19–20获得可比较的结果。

所有碳纳米管场效应晶体管均采用手性(19, 0)的纳米管作为沟道。事实上,碳纳米管直径取决于手性,为1.49 纳米,因此使用(19, 0)型碳纳米管的碳纳米管场效应晶体管的阈值电压为0.289 伏特。这些值在参考文献19中已被确认为在存储单元进行数据读操作或新数据写操作时的最优值。

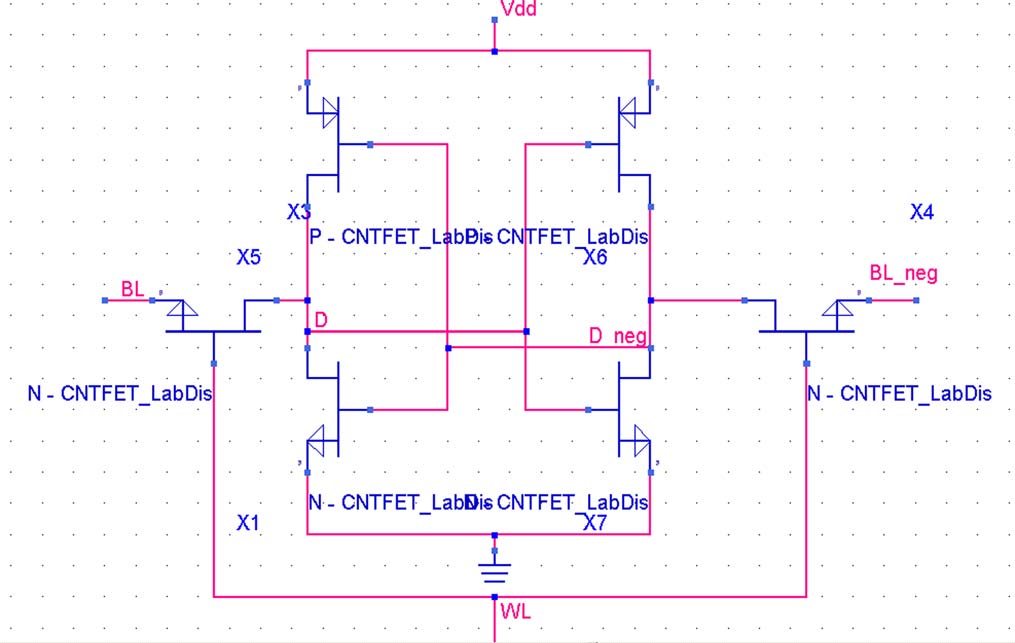

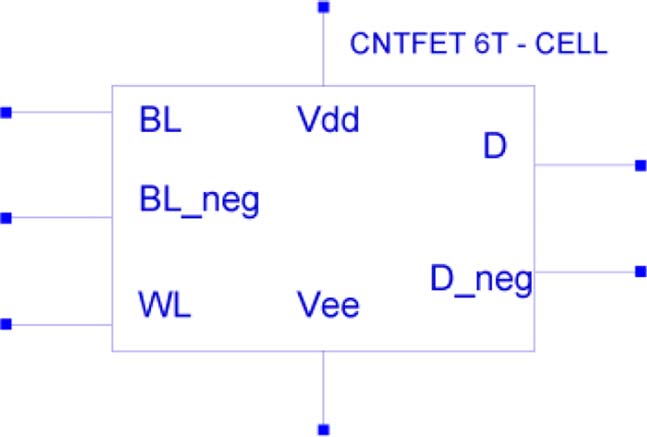

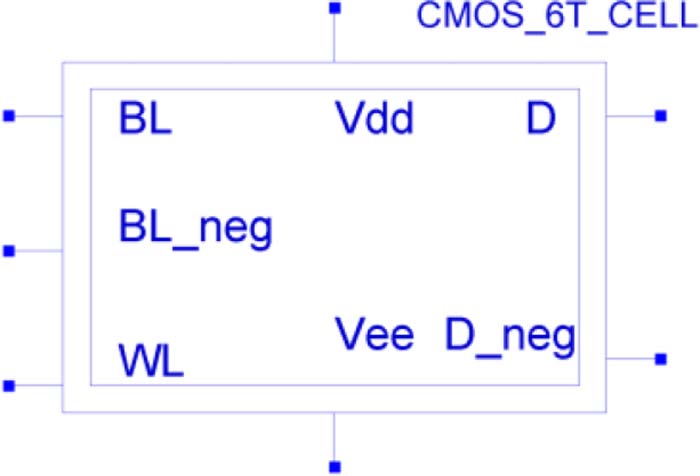

图2中所示的符号用于绘制基于CNT‐FET的SRAM单元的电路图,如图7 所示。

在此电路图中,插入了七个端口以将单元的输入和输出信号与符号的相应输入和输出引脚关联起来,如图8所示,与电路图相关。

至于基于CMOS的SRAM单元在ADS中的电路图,与图7相同,只是将碳纳米管场效应晶体管替换为CMOS。

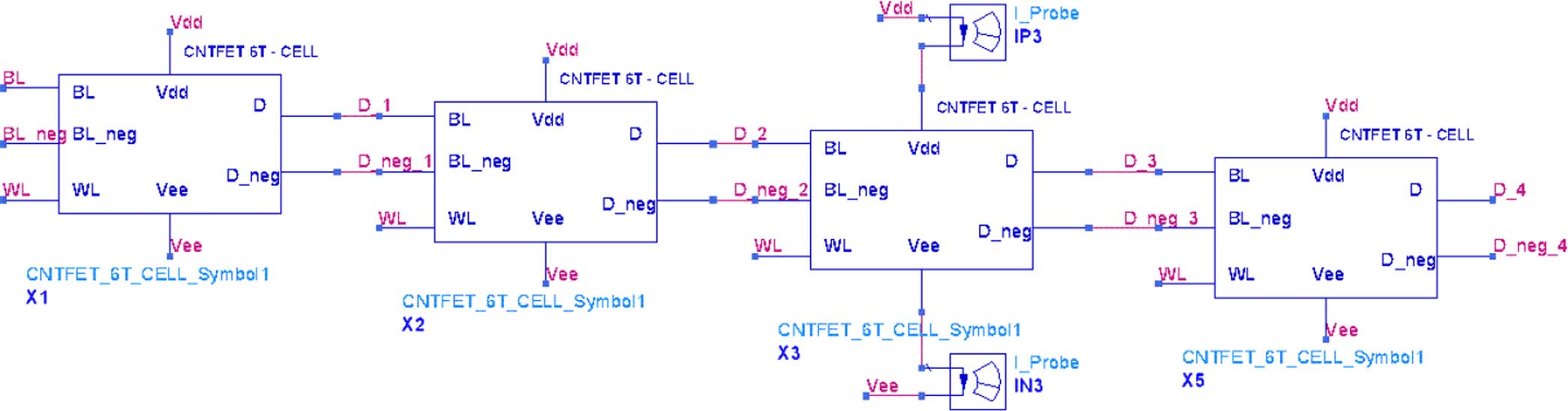

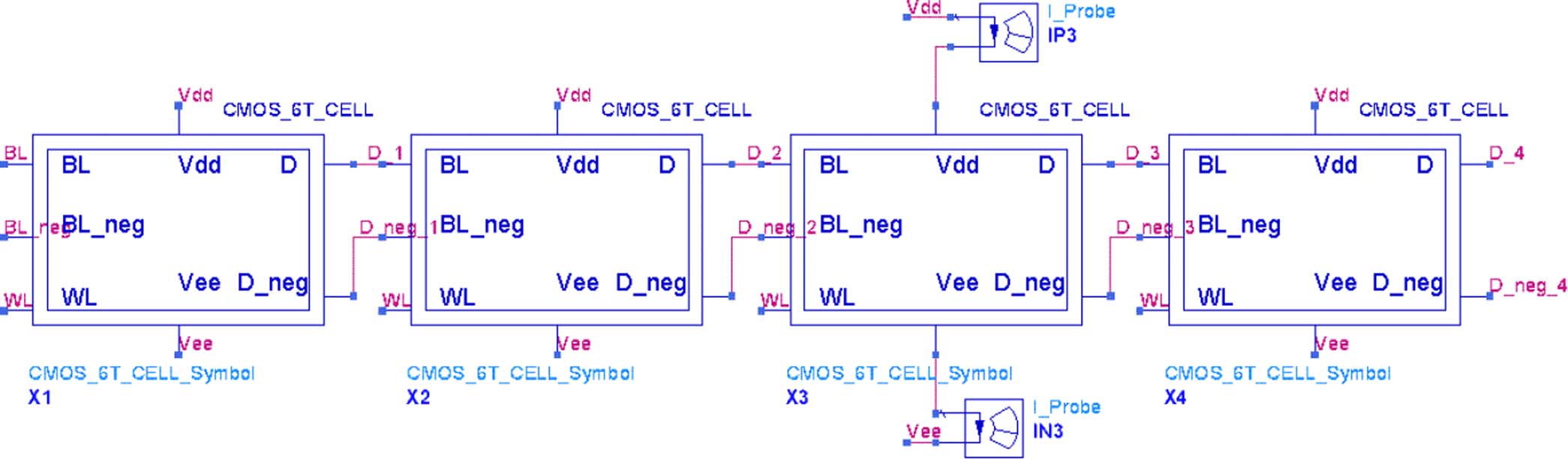

图13显示了为进行瞬态仿真而实现的电路。

我们没有使用单个单元:事实上,为了使仿真接近实际行为,必须实现一个6T单元的级联。每个单元作为前一个单元的负载。每个单元的输出信号即为下一个单元的输入信号。

在第一级输入端,我们施加了一个梯形信号,其上升和下降时间等于在第三级单元输出端观察到的相应时间。

在图13所示电路中,电源电压等于±0.3 伏特,工作频率为 3.84 GHz。然而,该电路也可用于考虑其他电源电压和工作频率值的情况。

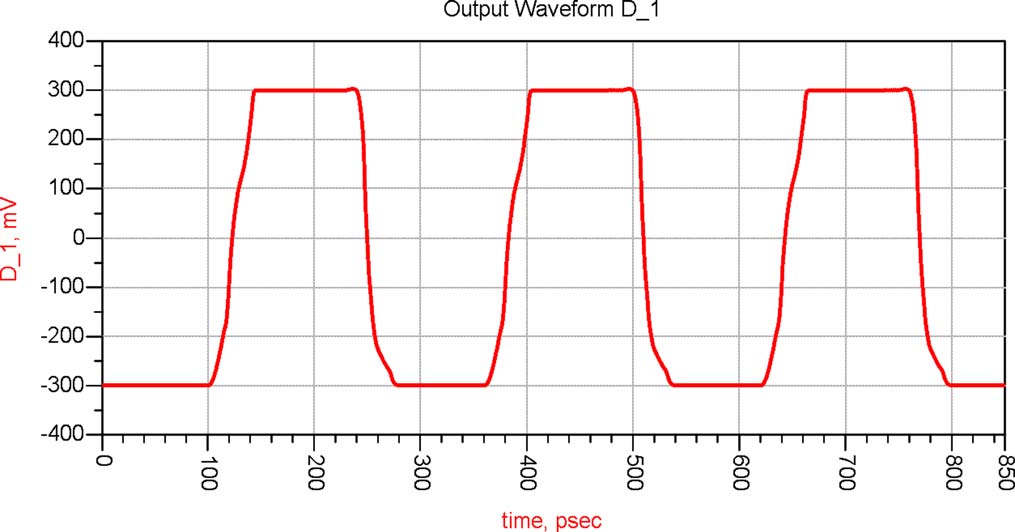

在图14中,我们报告了级联中第一个单元的输出波形。

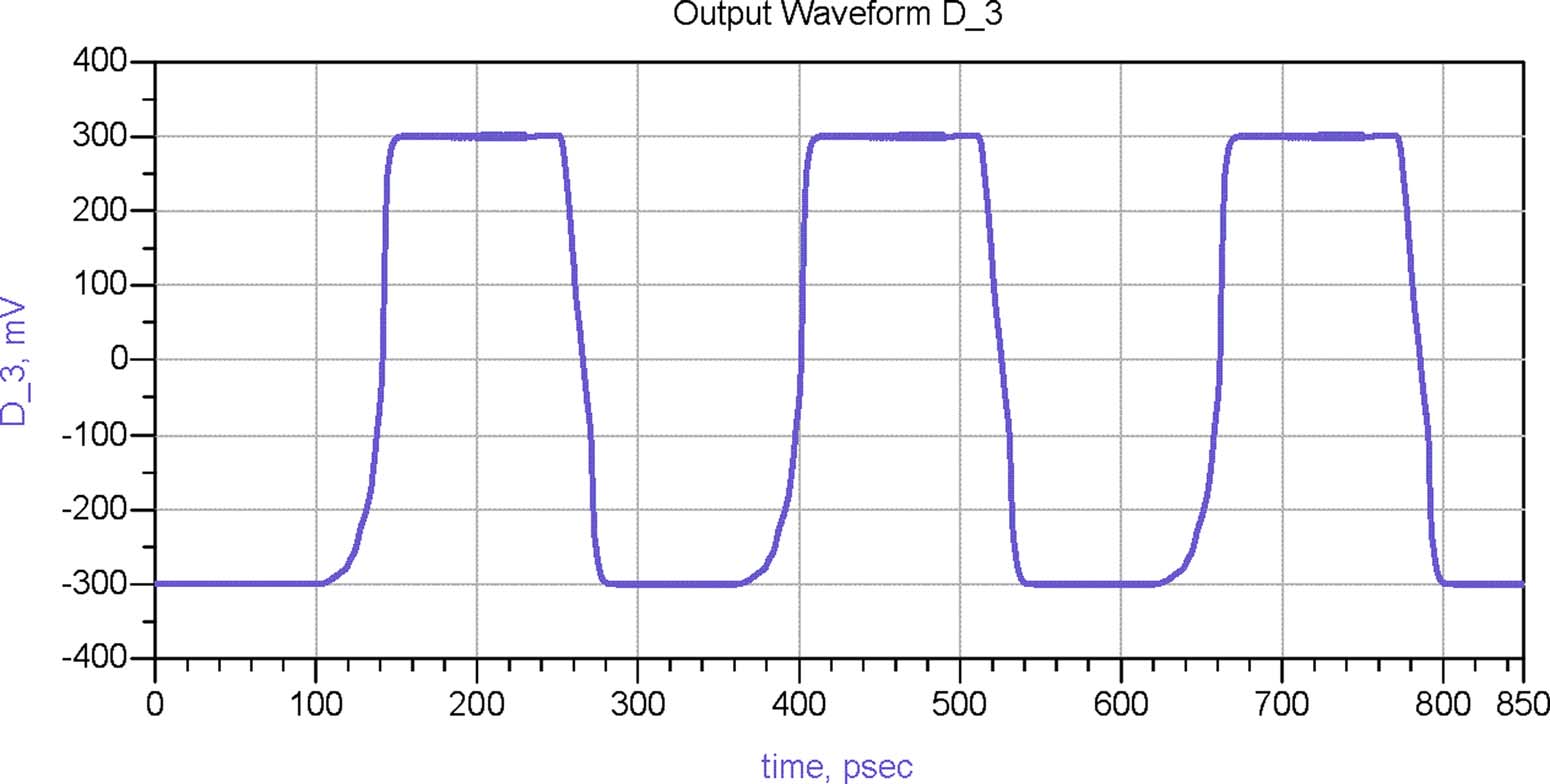

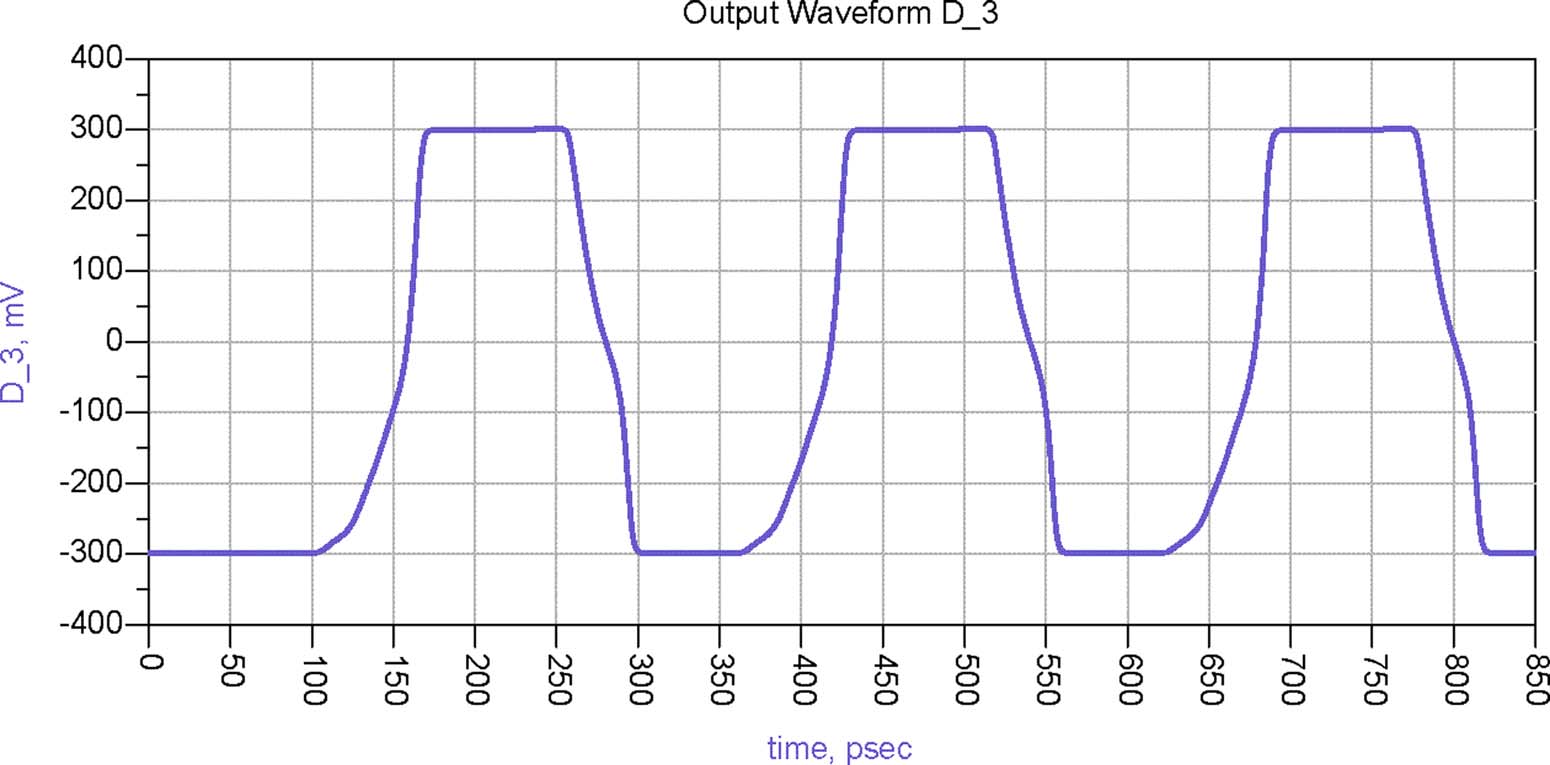

在相同工作条件下,图15显示了级联中第三个单元的输出波形。

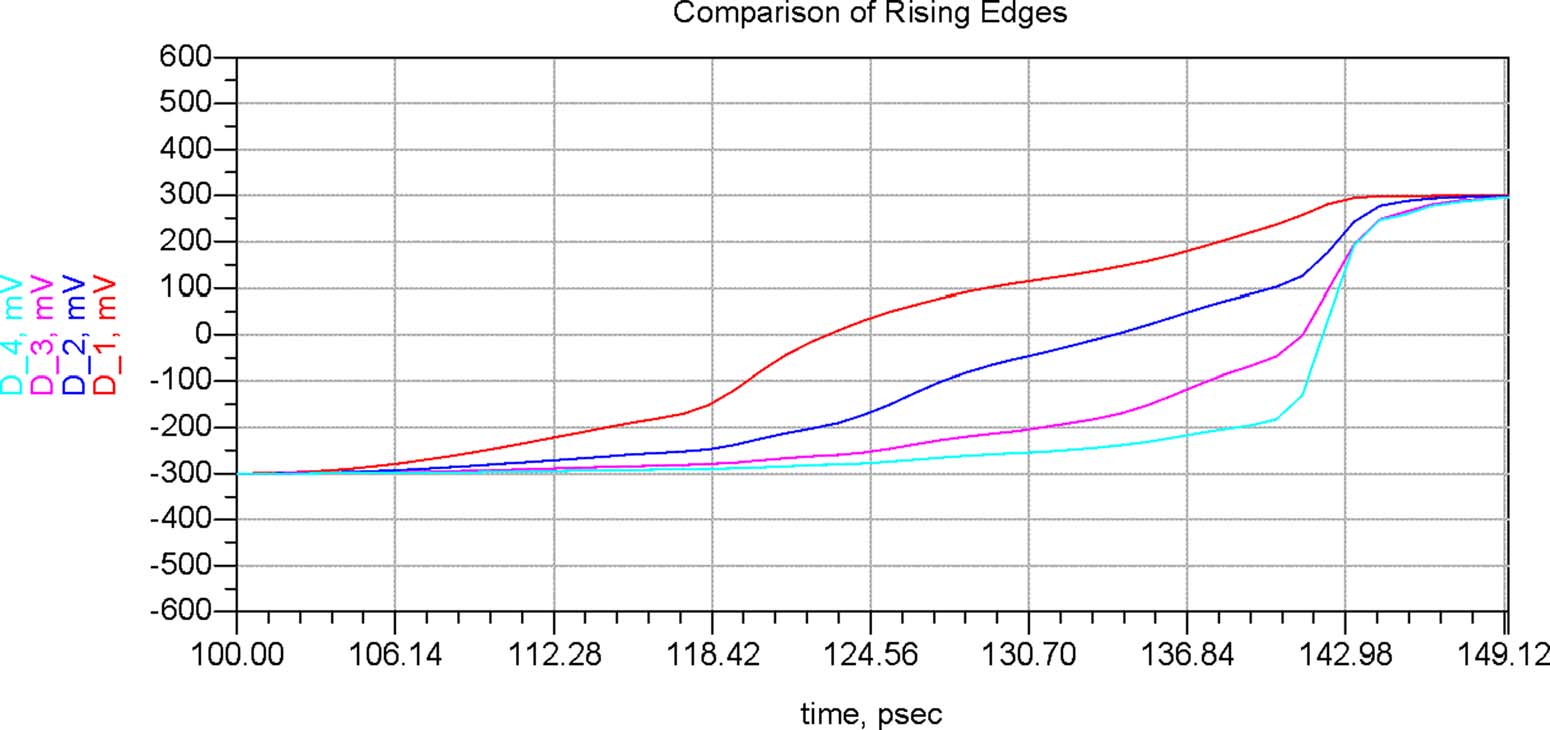

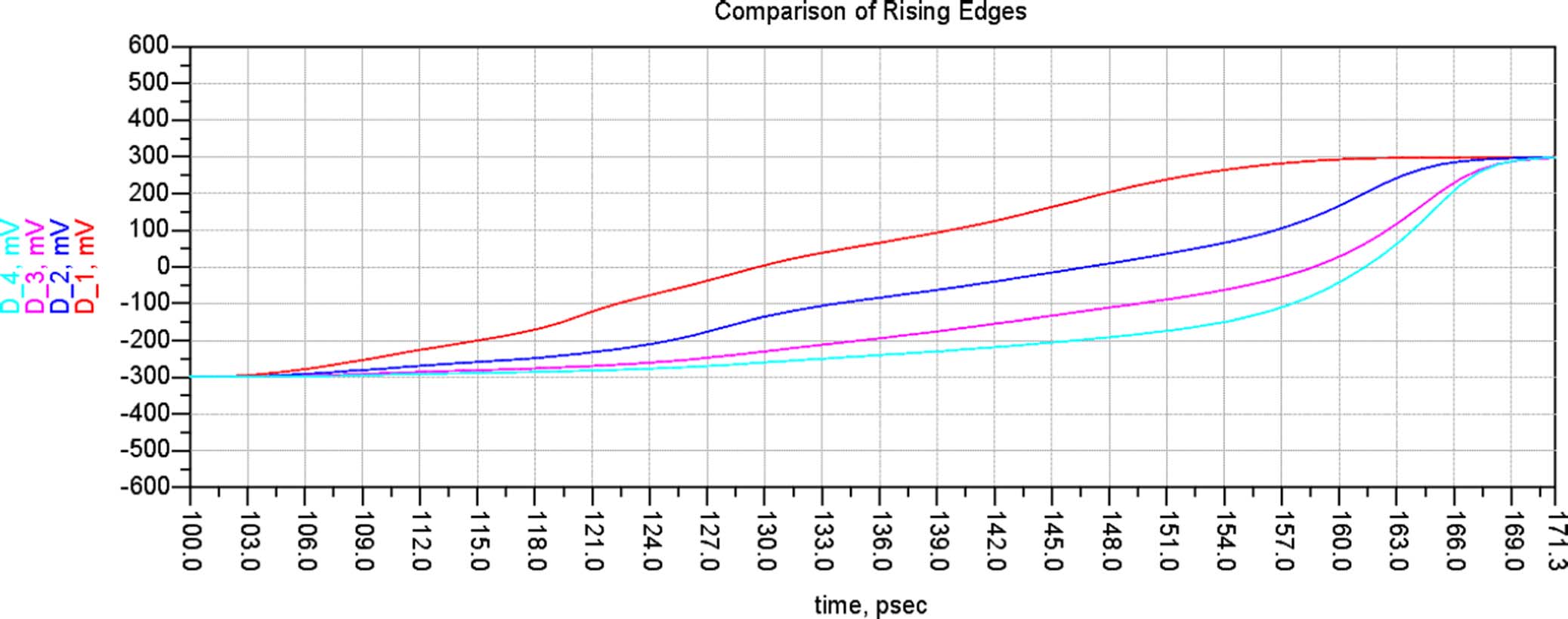

在图16中,我们报告了信号的上升沿,其中可以验证,随着电源电压的降低,上升时间得到了改善。

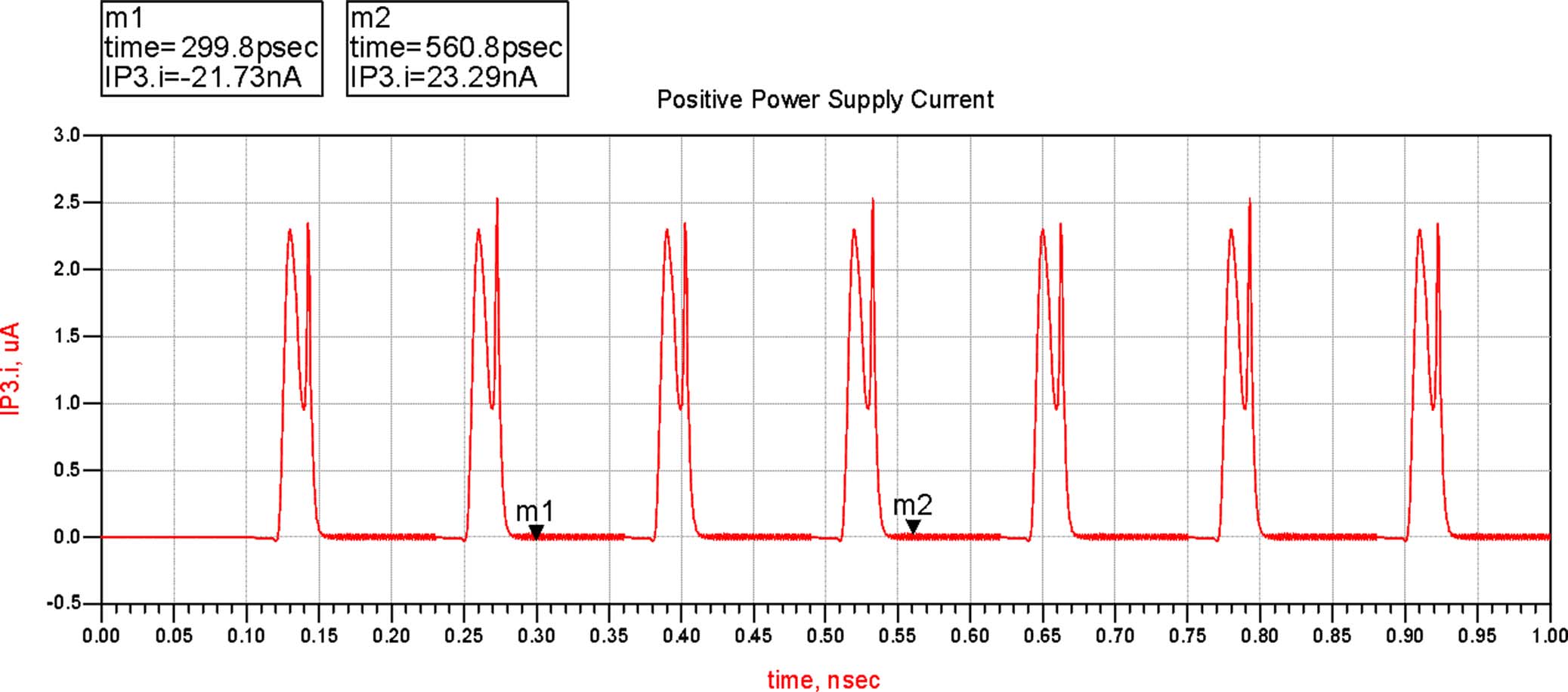

图17显示了电流相对于电源(±0.3 伏特和3.84 GHz)的变化趋势。通过这种方式,可以确定一个周期内积分电流的值、能量值以及功率值。

为了比较在CNT‐FET技术中实现的SRAM与CMOS技术中相同实现的性能,我们采用了之前已描述过的方法。

图18所示电路由两个信号BL和BL_neg驱动,这两个信号必须处于反相状态,才能使单元正常工作。

图18所示电路中的电源电压等于 ±0.3 V。P型和N型互补金属氧化物半导体(如图18中所示的V_thp和V_thn)的阈值电压略低于电源电压,因此获得了6T单元的近阈值行为。

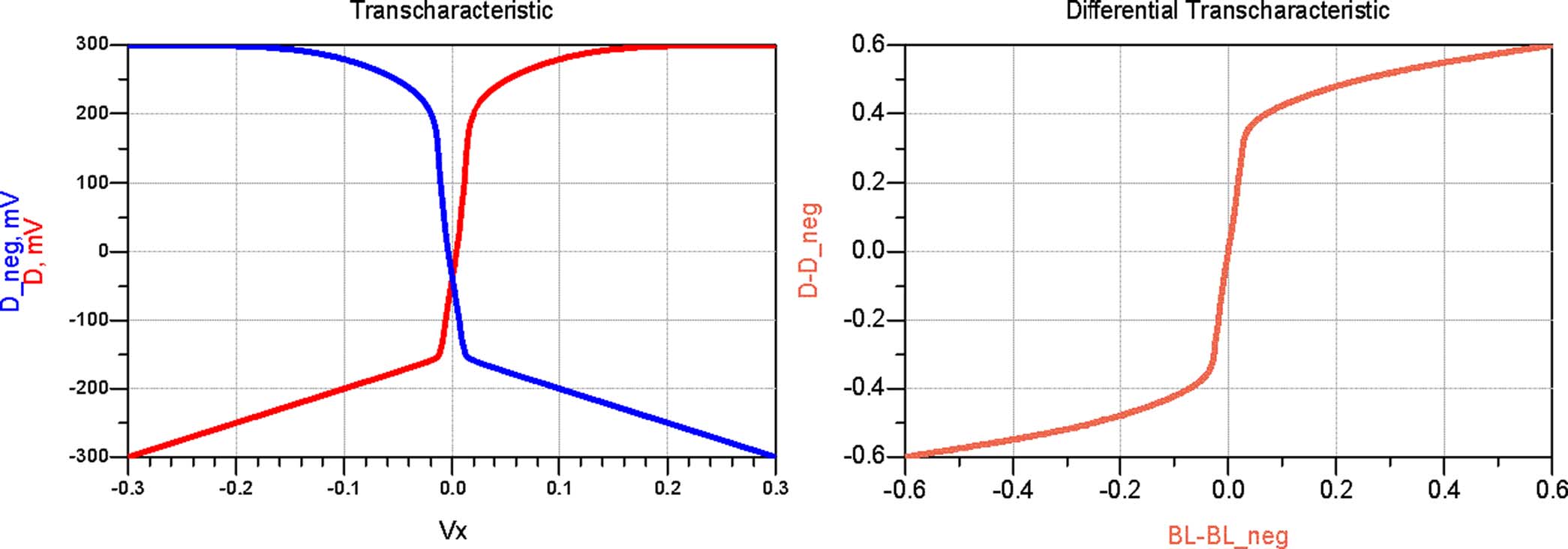

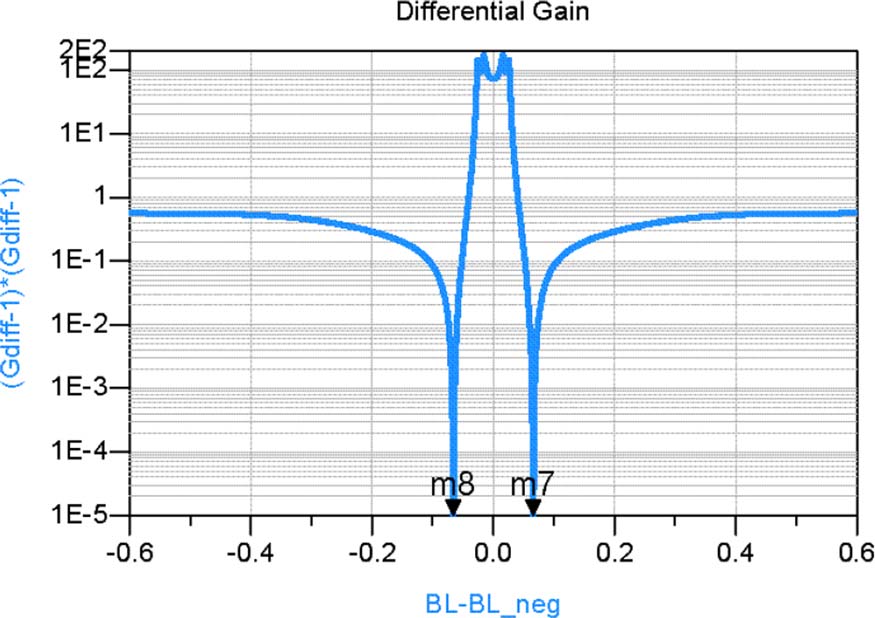

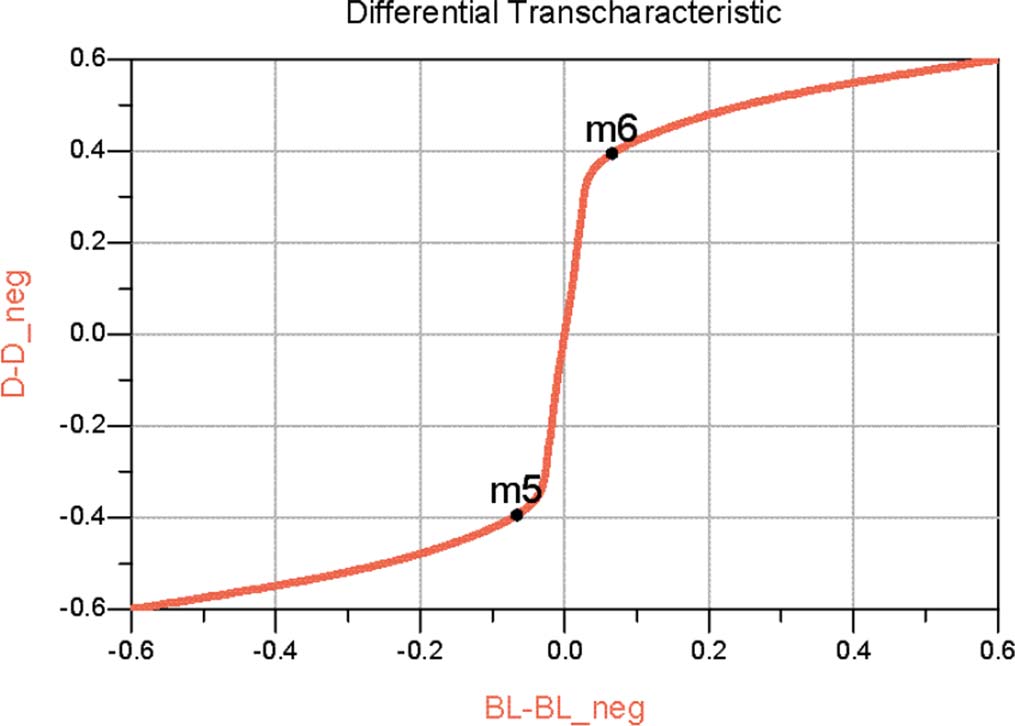

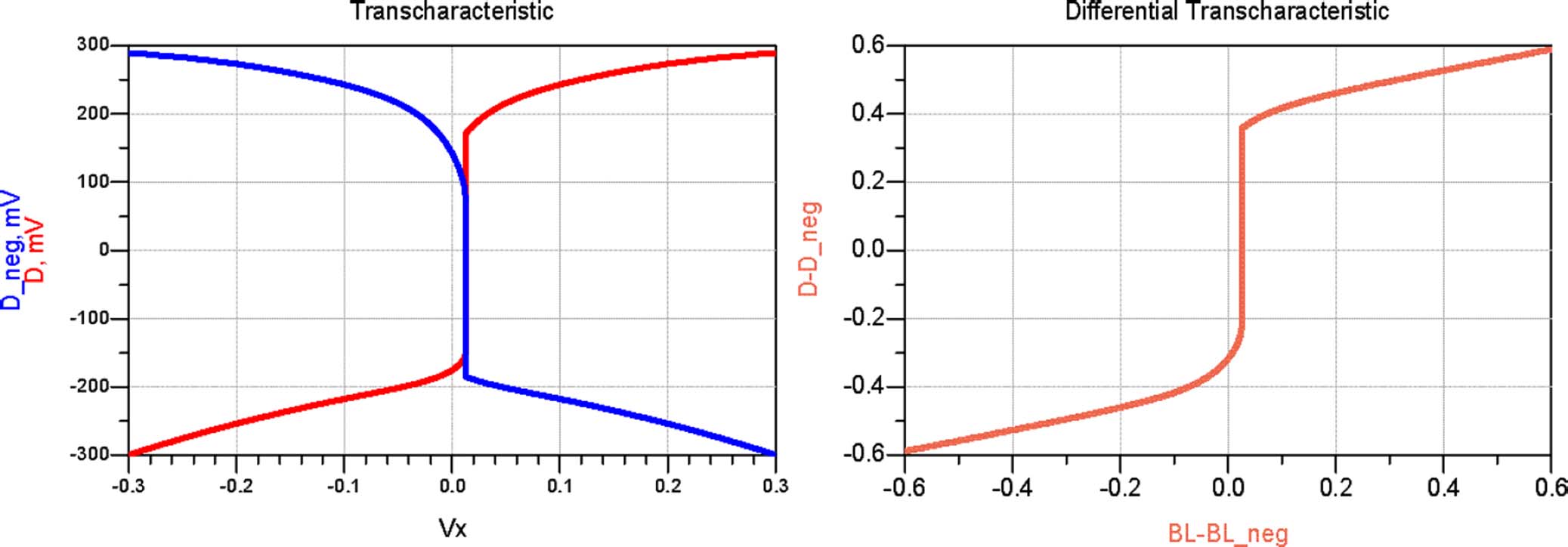

为了简化处理,我们仅报告在电源电压为 ±0.3 V、工作频率为3.84 GHz时获得的跨导特性和增益,如图19所示。

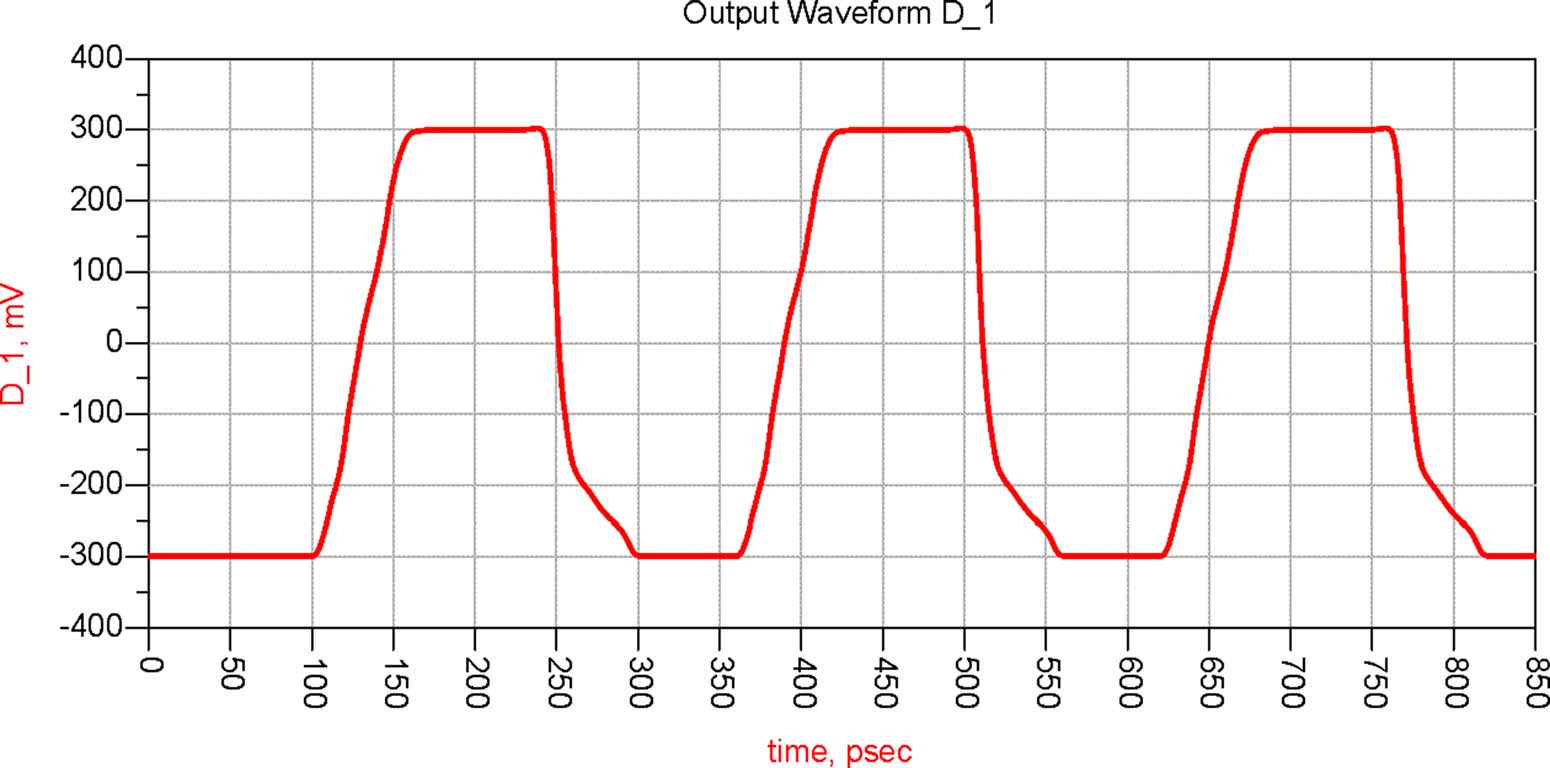

图20显示了级联中第一个单元的输出波形。在相同工作条件下,图21显示了级联中第三个单元的输出波形。

在图22中,我们报告了信号上升沿(±0.3 伏特和 3.84 GHz)。

对于CMOS技术,我们已经验证,降低电源电压可以改善上升时间。

最后,图23显示了电流相对于电源(电源电压 =±0.3 伏特和工作频率=3.84 GHz)的变化趋势。

通过这种方式,可以确定一个周期内积分电流的值、能量值和功率值。

仿真结果讨论

仿真结果可以通过以下表格进行总结 I、II、III和 IV,其中我们报告了两种技术的功率和上升时间,并考虑了以下情况的仿真结果:

1. 电源电压 = ± 0.5伏特;工作频率 = 3.84 GHz

2. 电源电压 = ± 0.3伏特;工作频率 = 2.2GHz

3. 电源电压 = ± 0.5伏特;工作频率 = 2.2GHz

因此,为了避免加重论述的负担,我们未展示相关的图表。

可以明显观察到,使用碳纳米管场效应晶体管实现的存储单元能够达到非常高的工作频率,同时始终保证可靠且失真小的信号。对该单元的静态分析确定了逻辑阈值,在碳纳米管场效应晶体管技术中,这些逻辑阈值比在互补金属氧化物半导体技术中获得的更为受限。

互补金属氧化物半导体技术中SRAM单元的仿真表明,其在接近4 GHz频率下仍能良好运行,超过该频率后信号发生严重畸变,几乎变为三角波信号。

| 表I. 所设计的SRAM 6T的功率和上升时间值 单元(电源电压= ± 0.5 伏特 和频率 = 2.2 GHz)。 |

|---|

| 技术 |

| CMOS 45纳米 |

| CNTFET 32纳米 |

| 表II. 所设计的SRAM 6T 单元(电源电压= ± 0.3 伏特且频率为= 2.2 GHz)。 |

|---|

| 技术 |

| CMOS 45纳米 |

| CNTFET 32纳米 |

| 表III. 所设计的SRAM 6T的功率和上升时间值 单元(电源电压= ± 0.5 伏特和频率 = 3.84 GHz)。 |

|---|

| 技术 |

| CMOS 45纳米 |

| CNTFET 32纳米 |

| 表IV. 所设计的SRAM 6T的功率和上升时间值 单元(电源电压= ± 0.3 伏特和频率= 3.84 GHz)。 |

|---|

| 技术 |

| CMOS 45纳米 |

| CNTFET 32纳米 |

结论与未来发展

本文中,我们对用于超低功耗应用的亚阈值区工作的碳纳米管场效应晶体管(CNTFETs)的行为进行了仿真。特别是,我们提出了基于碳纳米管场效应晶体管的SRAM单元设计,并采用了我们此前已提出的碳纳米管场效应晶体管模型。随后,采用相同的设计流程对基于CMOS技术的SRAM单元进行表征,其中使用了ADS库中的BSIM4模型。特别地,我们通过参数化仿真调整了MOSFET参数,以使MOSFET模型的性能与碳纳米管场效应晶体管模型相当。

我们观察到,采用碳纳米管场效应晶体管实现的存储单元能够达到很高的工作频率,同时始终保证可靠且失真小的信号。对该单元的静态分析确定了逻辑阈值,在碳纳米管场效应晶体管技术中,这些逻辑阈值比在互补金属氧化物半导体技术中获得的更受限制。

基于CMOS技术的SRAM单元仿真表明,在接近4 GHz频率下仍能良好运行,超过该频率后信号发生严重畸变,转变为首个三角波近似信号。

目前我们正在研究温度和噪声对基于CNTFET的模数电路的影响。17–20

659

659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?