超低功耗10纳米FinFET的设计策略

1. 引言

三栅鳍式场效应晶体管器件由于对沟道具有更强的控制能力,已取代传统的平面型MOSFET,广泛应用于14纳米及以下工艺节点,从而实现了更低的亚阈值摆幅(SS)和漏致势垒降低(DIBL)。体硅鳍式场效应晶体管可缓解绝缘体上硅(SOI)FinFET存在的晶圆成本较高和散热性能较差等问题。此外,栅致漏极泄漏(GIDL)成为实现超低关态电流(IOFF)(<100pA/lm量级)的主要限制因素。已有许多研究提出了在FinFET器件中降低GIDL电流的方法[1,2]。通过提高晶体管的阈值电压,可以降低IOFF。这可以通过多阈值电压技术实现,例如优化源漏延伸区、调节栅极功函数以及增加栅极长度[3,4]。较长的栅极长度有助于降低漏电流,并减轻低功耗(LP)和超低功耗(ULP)晶体管的短沟道效应(SCEs),但会占用更大的器件面积[5]。此外,它还可能导致模拟性能指标(FOM)下降,例如截止频率fT= gm/2πCgg,其中Cgg为总栅极电容。这是因为随着栅极长度的增加,跨导减小,同时Cgg增大。

已提出多种技术,如HALO注入和渐变沟道设计,以克服性能指标的退化问题。在纳米级器件,采用这些技术带来了技术挑战。源漏工程(也称为栅极‐源极‐漏极重叠)的概念已被研究用于抑制短沟道效应(SCEs)并降低关态电流[6–8]。以往关于多阈值技术的研究主要集中在绝缘体上硅FinFET。在本工作中,上述三种技术被应用于体硅鳍式场效应晶体管,以满足低功耗和超低功耗晶体管的IOFF要求。

2. 器件仿真

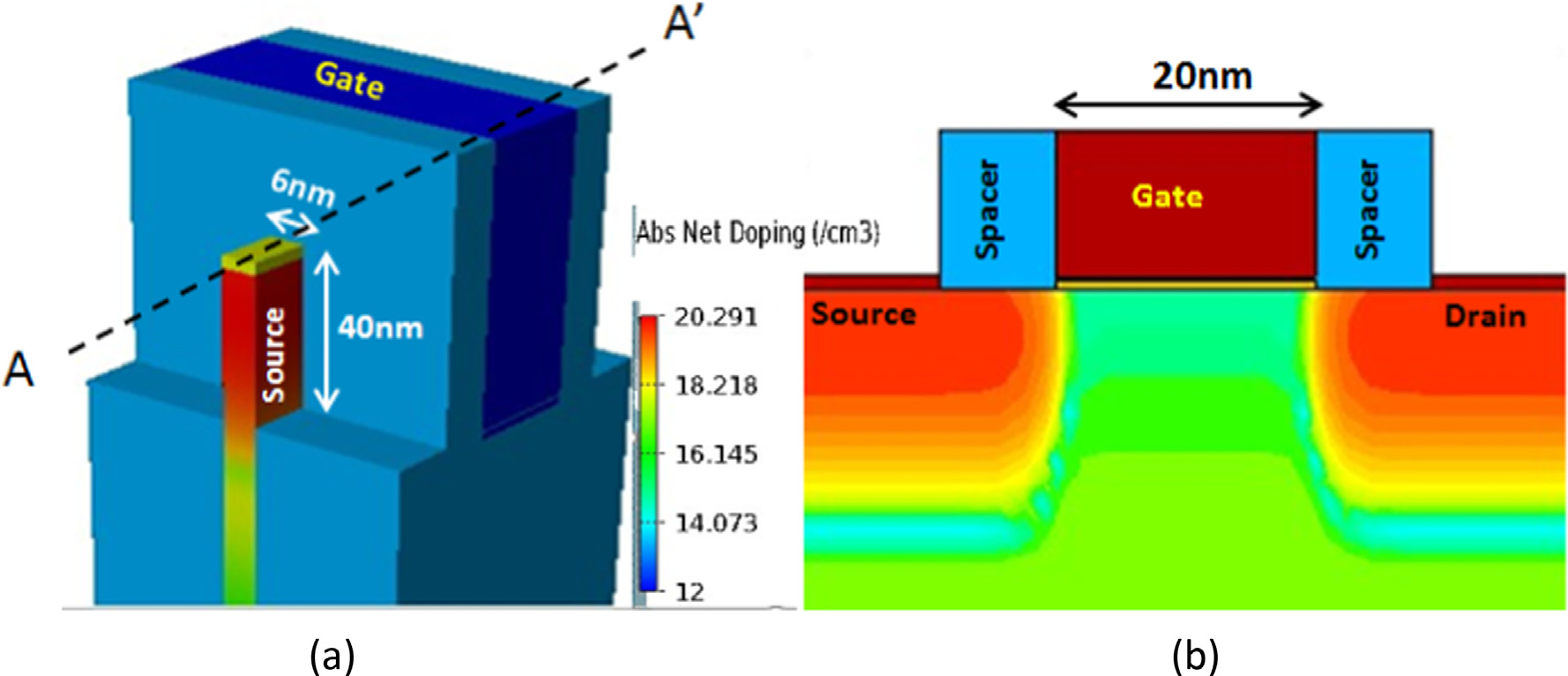

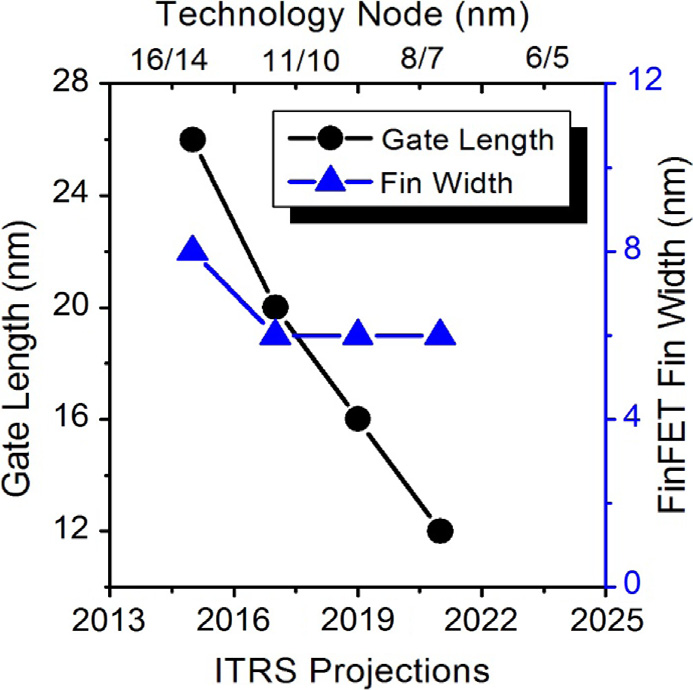

国际半导体技术路线图(ITRS)预测的延伸至7纳米节点的FinFETs鳍片宽度和栅极长度如图1所示。在7纳米节点之后,垂直全环绕栅极场效应晶体管(VGAA)和单片3DCMOS(M3D)等新晶体管结构仅是未来候选方案中的几个[9]。本研究针对符合10纳米节点ITRS要求的体硅n型沟道FinFETs进行。

仿真的器件参数列于表1中。栅极长度为20纳米,等效栅介质厚度(EOT)为0.8 nm。源漏掺杂为1.5 × 10²⁰ cm⁻³。沟道停止注入的掺杂浓度范围从1 × 10¹⁷ cm⁻³到 5 × 10¹⁸ cm⁻³。图2 显示了为仿真构建的器件。

| 参数 | 值 |

|---|---|

| 栅极长度 | 20纳米 |

| 鳍高度(Hfin) | 40纳米 |

| 鳍厚度(Wfin) | 6 nm |

| 栅极氧化层厚度(等效氧化层厚度) | 0.83 纳米 |

| 源漏掺杂 | 1.5 × 10²⁰ cm⁻³ |

使用Silvaco 3D VictoryProcess和VictoryDevice工艺与器件仿真器[10]对三栅FinFET进行了三维工艺与器件仿真。FinFETs通过沉积、刻蚀、扩散和蒙特卡洛注入工艺制备而成。

VictoryProcess的模块。器件仿真采用玻姆量子势(BQP)模型,以考虑载流子在三个维度上的量子限制效应[11]。表面沟道中的迁移率使用 “CVT”模型进行建模,该模型考虑了横向和纵向电场的影响[12]。仿真中还包含了俄歇效应以及浓度依赖的Shockley‐Read‐Hall复合等其他效应。已引入Hurkx模型及其带间隧穿(BTBT)公式来分析栅致漏极泄漏(GIDL)。BTBT产生率GBTBT由下式给出:

$$

G_{BTBT} = A \cdot \exp\left(-\frac{B}{E}\right) \cdot E^{P}

$$

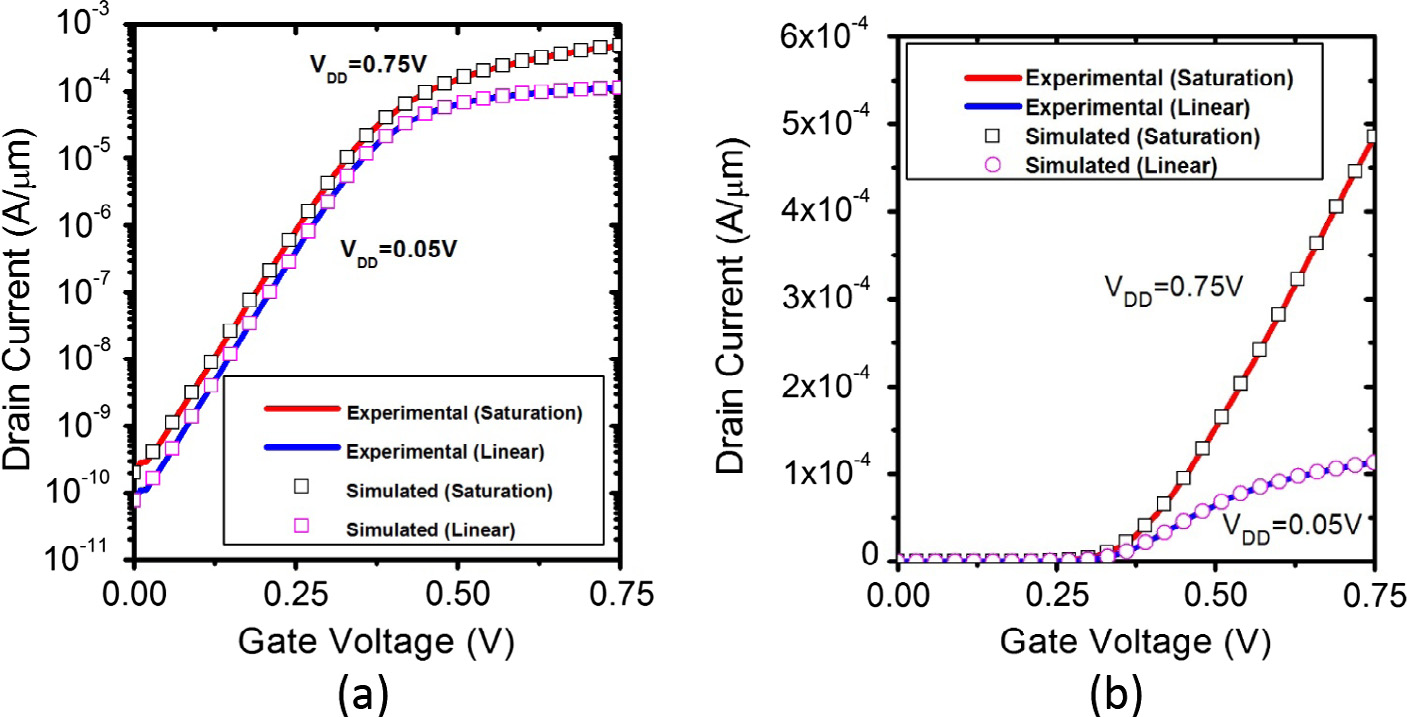

其中E为横向电场,E₁ = 1 V/cm;P = 2.5 表示硅作为间接带隙半导体中的声子辅助BTBT跃迁。A和B是硅的凯恩参数,其值分别为A = 4 × 10⁴ cm⁻³ s⁻¹和B = 1.9 × 10⁷ V/cm[13]。模拟得到的IDS-VGS特性如图3所示,并与报道的20nm体硅鳍式场效应晶体管的实验数据进行了比较,验证了所用模型的有效性。

使用这些模型,已研究了多种满足10纳米节点低功耗和超低功耗NMOS FinFET晶体管目标的方法。

3. 结果与讨论

在本节中,研究了穿通掺杂、源极和漏极延伸工程以及栅极功函数对IOFF和跨导的影响,并在下文讨论了结果。

3.1. 穿通阻止掺杂(PTS)的影响

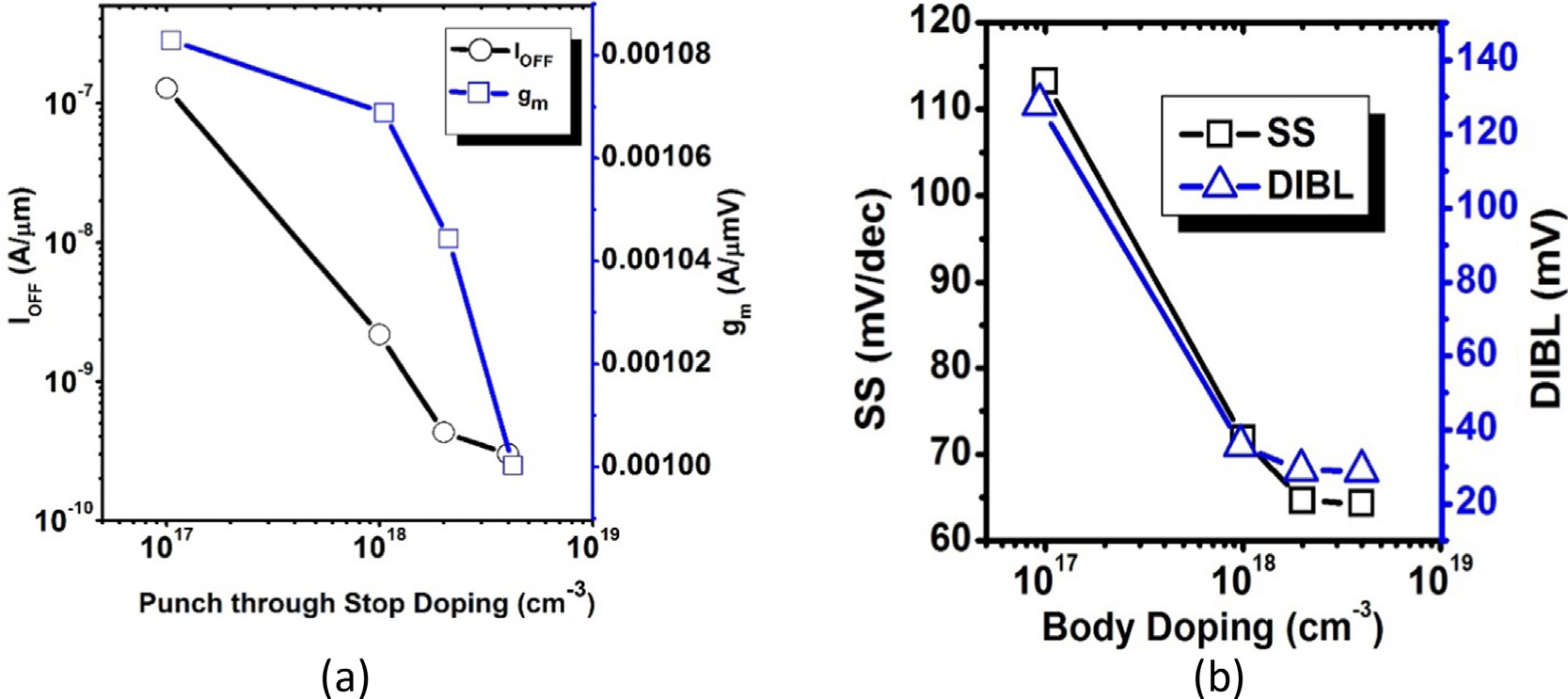

Manoj等人研究了PTS掺杂对体硅FinFET漏电流的影响[15]。众所周知,通过增加沟道中p型(或n型)掺杂浓度,可以提高n型(或p型)MOSFET的阈值电压。然而,引入掺杂剂也会导致迁移率退化。为了减小对迁移率的影响,本研究采用了反向掺杂分布。通过改变穿通阻挡(PTS)注入的剂量来调节阈值电压,其中注入峰值位于鳍下方。但由于PTS注入尾部的存在,沟道区域并未完全保持未掺杂状态。

为了评估漏电流性能,将p型PTS掺杂从1 × 10¹⁷ cm⁻³更改为4 × 10¹⁸ cm⁻³。这些仿真针对栅极功函数(WF)为4.5电子伏特的情况进行。较高的鳍体掺杂由于迁移率退化而导致关态电流降低,跨导也降低(图4(a))。跨导提取自饱和区。体掺杂对亚阈值摆幅(SS)和漏致势垒降低(DIBL)的影响如图4(b)所示。DIBL通过DIBL = (Vth,sat − Vth,lin)/(VDS,sat − VDS,lin)提取。其中Vth,sat和Vth,lin分别为饱和模式和线性模式下的阈值电压值。VDS,sat为0.75伏特,VDS,lin为0.05伏特。通过增加穿通阻挡(PTS)掺杂,DIBL和SS得到改善。显然,调整PTS掺杂可以实现更低的DIBL和SS,但同时也会降低跨导,且IOFF并未降低到足以满足超低功耗晶体管要求的程度。

3.2. 源漏延伸区工程

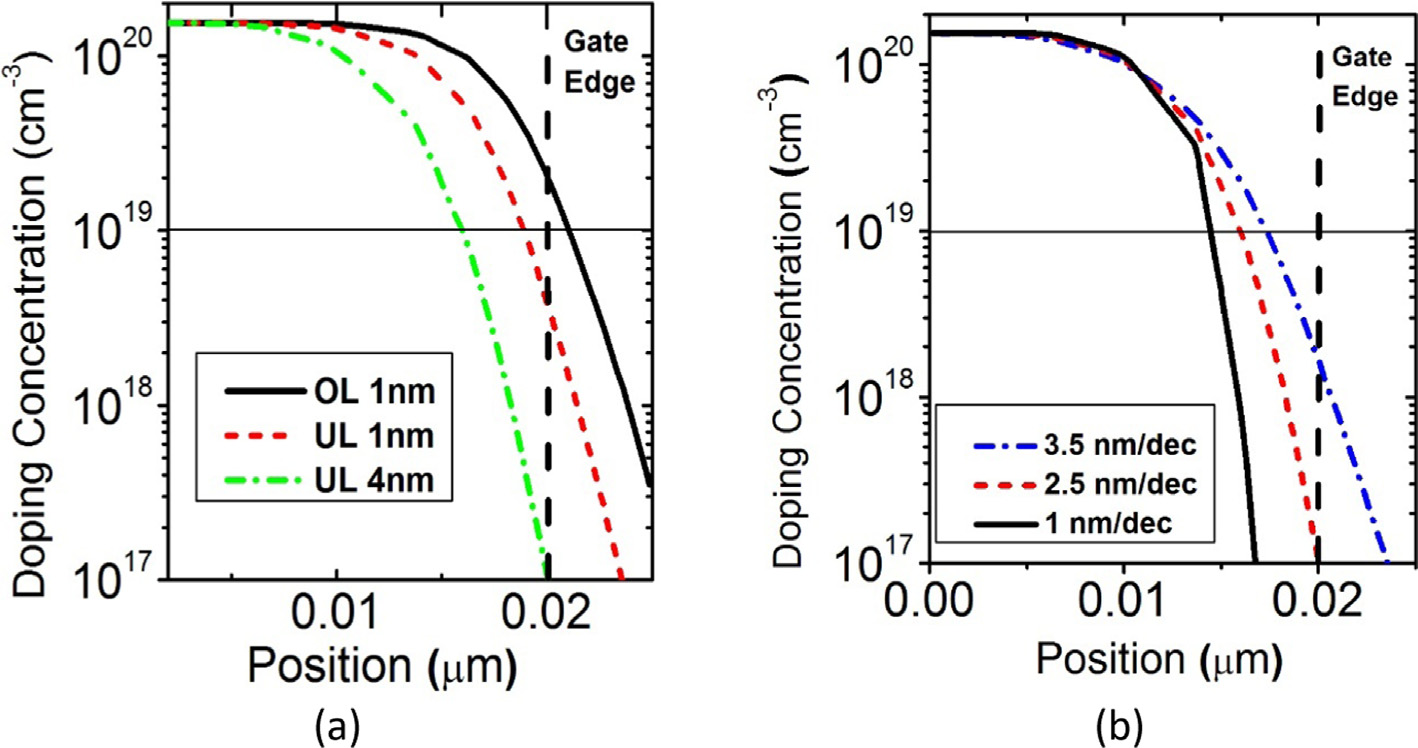

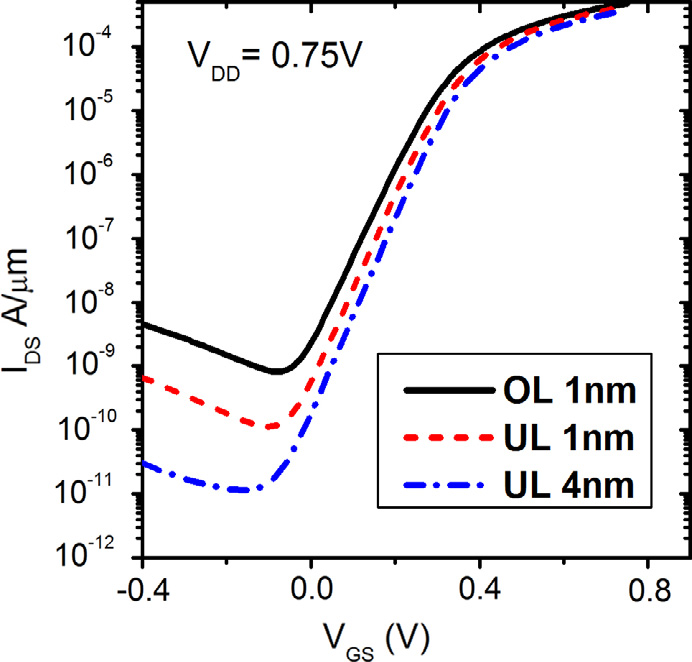

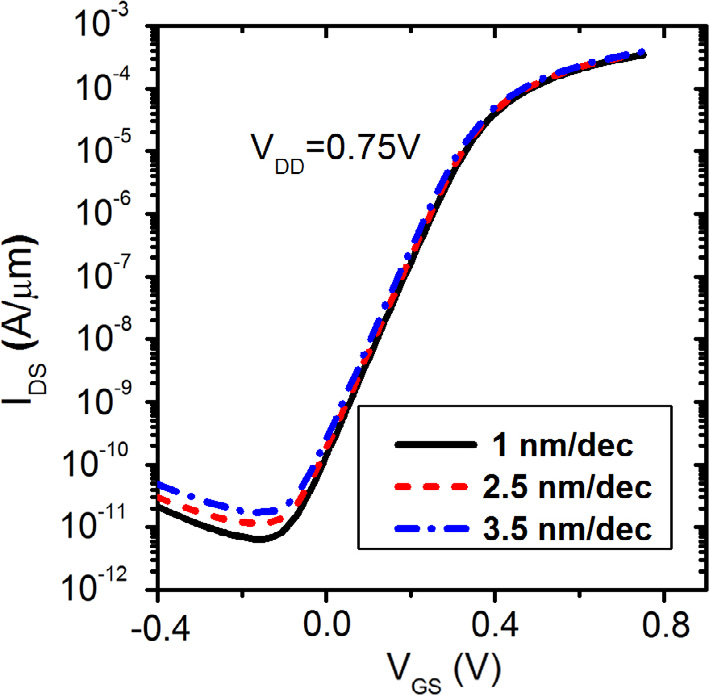

源极和漏极的掺杂分布采用高斯表达式 $N(x) = N_p \exp(-x^2/r^2)$ 建模,其中 $N_p$ 为源漏峰值掺杂浓度,$r$ 为横向散射。该峰值浓度设置为 $2 \times 10^{20} \text{cm}^{-3}$,且 $r$ 在 1 到 3.5 纳米之间变化。通过改变侧墙厚度来设计结未对齐,该侧墙厚度由栅极边缘处的 $1 \times 10^{19} \text{cm}^{-3}$ 掺杂值的位置定义,如图5(a)所示。对于4纳米超浅结情况,结梯度(横向标准偏差)的变化如图5(b)所示。

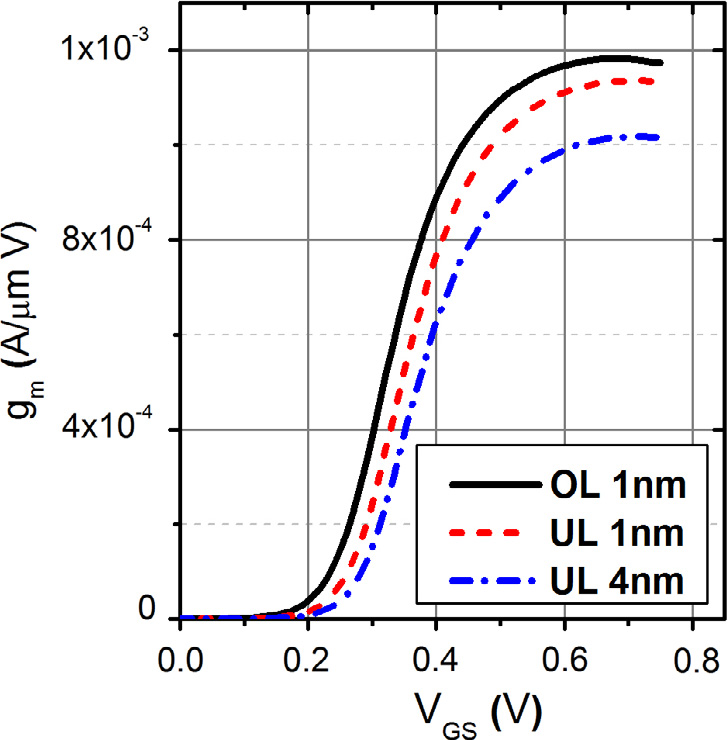

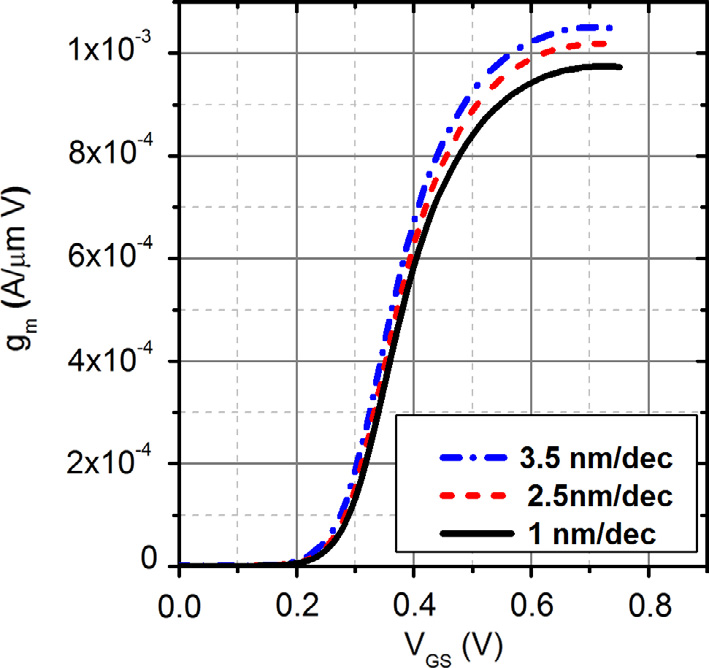

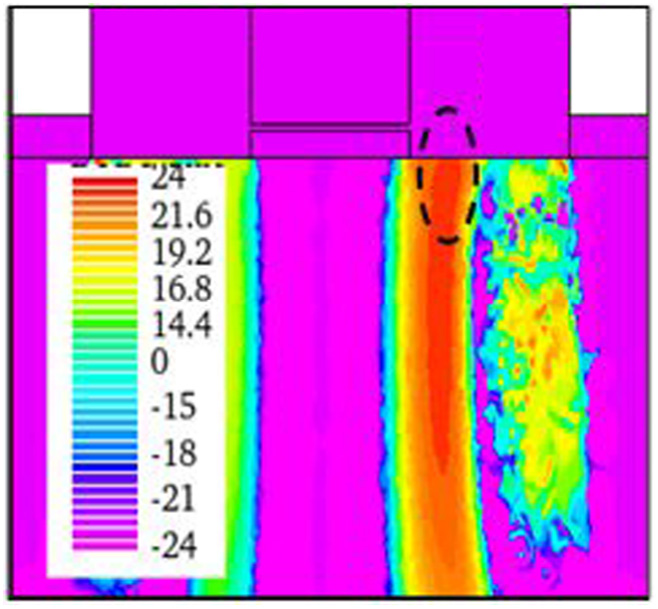

在图6中,观察到结重叠增加4 nm时,GIDL电流增加了两个数量级。增加结未对齐(UL)会增加有效沟道长度,并导致 $g_m$ 退化,如图7所示。图8显示了在漏极偏压为0.75 伏特时,4 nm 结未对齐情况下不同结梯度的 $I_{DS}-V_{GS}$ 特性。更陡的结梯度会减小GIDL电流,因为有效沟道长度增加,垂直结电场降低,从而提高了 $g_m$(图9)。需要注意的是,梯度的变化也会导致在掺杂浓度为 $1 \times 10^{19} \text{cm}^{-3}$ 时定义的结位置发生移动。

图10 显示了UL和OL两种情况下的BTBT产生率。对于UL情况,BTBT产生率热点位于侧墙区域下方。另一方面,在OL结的情况下,BTBT产生率热点位于栅极下方。

1 纳米的重叠(OL);(b) 4纳米的非重叠(UL)。)

1 纳米的重叠(OL);(b) 4纳米的非重叠(UL)。)

3.3. 栅极功函数的影响

另一种提高阈值电压的方法是增加栅极功函数。在本研究中,对于掺杂浓度为 $2 \times 10^{18} \text{cm}^{-3}$ 且结未对齐为4 nm的情况,金属栅功函数在 4.40 到 4.75 电子伏特之间变化。图11 显示了功函数对 $I_{OFF}$ 和 $g_m$ 的影响。当功函数从4.40变化到4.75电子伏特时,$I_{OFF}$ 呈线性下降。超过4.6 电子伏特后,GIDL电流开始占主导地位,导致 $I_{OFF}$ 增加。观察到通过调节功函数,可实现关态电流 <10 pA/μm。

4. 基准测试

对于低功耗和超低功耗应用,期望在最低关态电流下实现最高的本征频率。对上述所有三种情况的 $I_{OFF}$ 和晶体管本征速度进行了比较。图12映射了本研究中每种情况下获得的 $I_{OFF}$ 和本征频率 $f_T$ 值。增加掺杂浓度会导致 $V_T$ 升高,从而引起 $I_{OFF}$ 降低,但同时会降低本征速度。可以观察到,尽管功函数不影响 $g_m$ 的峰值,但对于超低功耗应用而言,仍不足以满足 $I_{OFF}$ 的目标要求。

对于超低功耗应用,栅极长度为20纳米、体掺杂浓度为 $2 \times 10^{18} \text{cm}^{-3}$、4 nm结未对齐且功函数为4.6 电子伏特的晶体管可在0.75伏特下实现 $I_{OFF} \leq 10 \text{pA}/\mu m$。

5. 结论

已对栅极长度为20纳米的10纳米三维三栅n沟道体硅FinFET进行了三维TCAD仿真。研究了实现低功耗(LP)和超低功耗(ULP)应用关态电流目标的三种方法。较高的穿通阻止掺杂可抑制短沟道效应,但会降低跨导。设计源漏结位置和掺杂梯度提供了额外的调谐策略,通过更陡峭的结梯度实现欠重叠,从而降低 $I_{OFF}$。通过合理选择栅极功函数,可进一步降低 $I_{OFF}$。研究发现,通过优化选择栅极功函数(4.6 电子伏特)、源漏延伸区工程(4 纳米欠重叠)以及鳍中掺杂浓度($2 \times 10^{18} \text{cm}^{-3}$),20纳米栅极长度器件可满足LP和ULP晶体管的要求。

7154

7154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?