中断系统架构

TMS320C6678的中断系统框架为CIC->INTC->CORE

CIC(4组)负责管理整个芯片层面来自各种外设的至多1024个系统事件(ps:这里是至多1024个,并不是系统事件正好有1024个,看文档时大家可能会在这里产生疑问)为什么至多1024个后续会讲到。

INTC可将CIC输出的128个事件映射到每个核的12个通道,整个中断的流程就是这样。

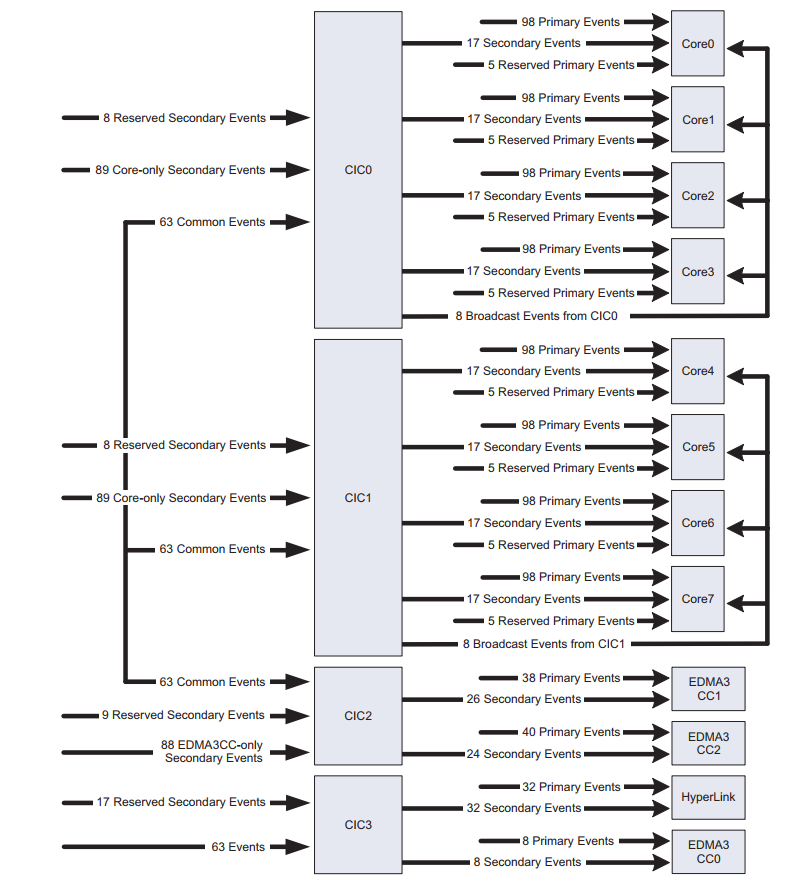

中断系统如下图所示:

接下来对系统各个部分展开详细讲解

CIC

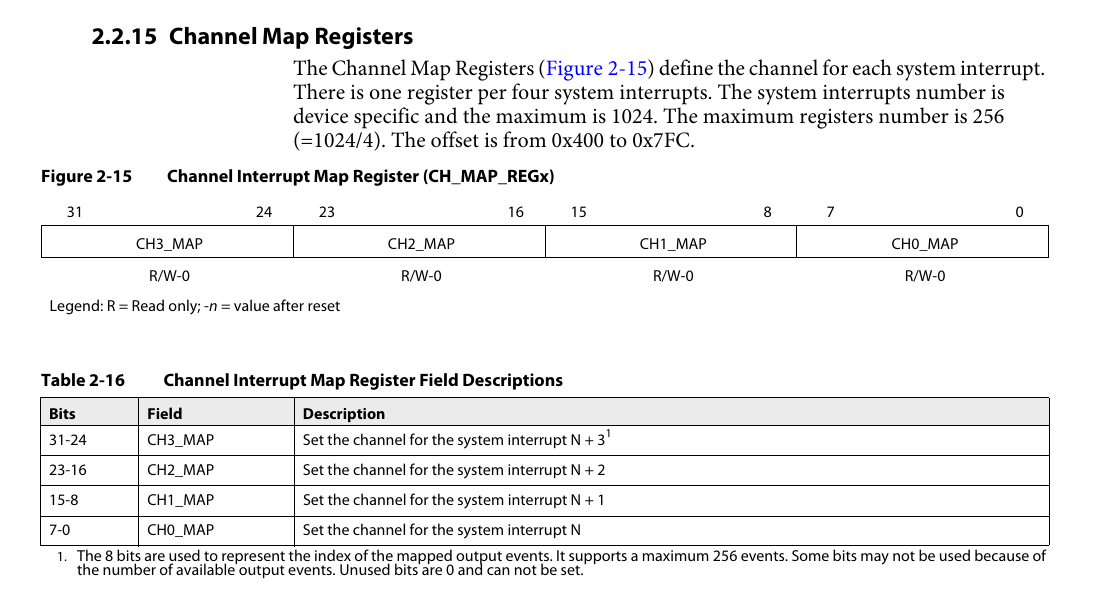

CIC是芯片级中断控制器,根据数据手册看到一共有256个32位的系统事件寄存器,每8位记录一共系统事件,因此最多有32/8*256=1024个系统事件。CIC可以映射256个信道给核去处理,也就是CIC0和CIC1总共映射256个中断事件给8个核,core0-core3处理CIC0的128个中断事件,core4-core7处理CIC1的128个中断事件。

INTC

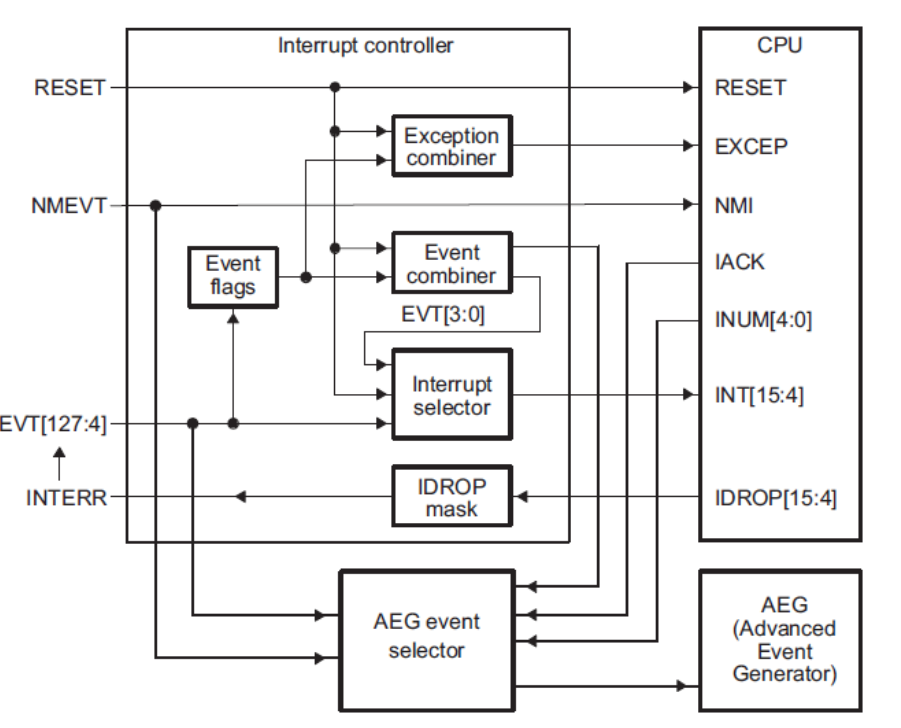

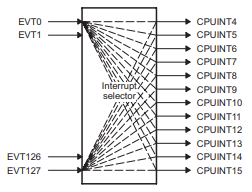

接下来介绍INTC的工作原理,INTC的输入来源有RESER、NMEVT和EVT[127:0](普通系统事件从CIC映射来的128个输出通道),EVT每一位对应一个中断源,最终会映射到INT[15:4](12个中断输入)上,INTC维护着一个中断服务表,存放着各个中断服务函数(ISR)的入口地址。

那么问题来了,128个事件对应12个输出这不是不够用吗,这里就有一个方法是中断复用,12个中断入口可以处理多个共享该入口的中断事件,多个共享的中断事件公用一个ISR函数,在函数中通过状态寄存器读对应事件号,然后对不同事件号做不同处理。

DSP中断系统详解

DSP中断系统详解

7394

7394

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?