偶然闯进了黑金社区,下载了一本名为《Verilog HDL那些事儿——建模篇》的书籍。从大学来一直到现在,几乎所有的书都是如出一辙的official,这本书给我耳目一新的感觉。

第一课是流水灯的控制和闪耀灯的控制。下面分享一下我编辑的代码。

功能目的:①闪耀灯模块:执行频率10Hz(100ms),资源占用:一个Led灯

②流水灯模块:执行频率3.3Hz(300ms),资源占用:三个Led灯

原码①:module flash(clk,rst_n,led_flash);

input clk;

input rst_n;

output led_flash;

reg led_flash_r;

reg[19:0] cnt;

always @ (posedge clk or negedge rst_n)

if (!rst_n) cnt <= 20'd0;

else if (cnt == 20'd999999) cnt <= 20'd0;

else cnt = cnt + 20'd1;

always @ (posedge clk or negedge rst_n)

if(!rst_n) led_flash_r <= 1'b0;

else if (cnt == 20'd999999) led_flash_r = ~led_flash_r;

assign led_flash = led_flash_r;

endmodule

原码②:module run(clk,rst_n,flash_out);

input clk;

input rst_n;

output [2:0] flash_out;

reg [23:0] cnt1;

always @ (posedge clk or negedge rst_n) //分频器,计数到300ms

if (!rst_n) cnt1 <= 24'd0;

else if(cnt1 == 24'd9999999) cnt1 <= 24'd0;

else cnt1 = cnt1 + 24'd1;

reg[2,0] flash_out_r; //定义一个寄存器flash_out_r

always @ (posedge clk or negedge rst_n) //流水灯控制

if(!rst_n) flash_out_r <= 3'b000;

else if(flash_out_r == 3'b000) flash_out_r <= 3'b001;

else begin if(cnt1 == 24'd9999999) flash_out_r <= {flash_out_r[1:0],1'b0};

end

assign flash_out = flash_out_r;

endmodule

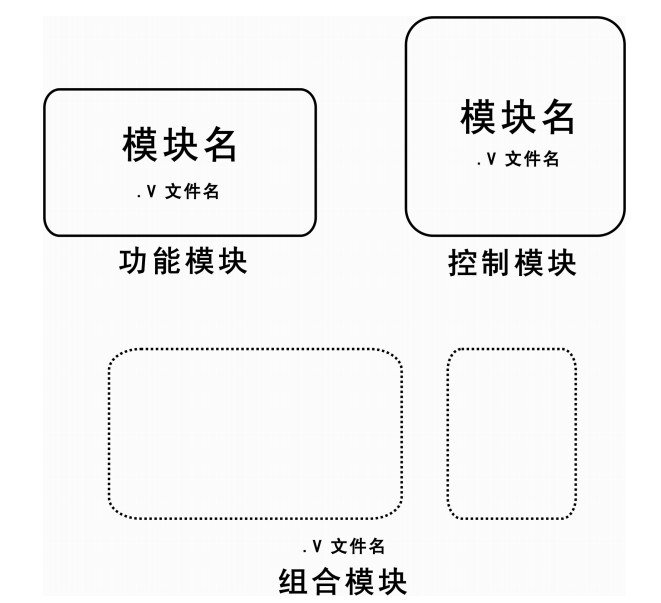

低级建模的一个准则是:一个功能模块|控制模块 仅有一个功能。过多的模块会使其不易于建模,而且使得图形绘制更加复杂。

本文分享了使用VerilogHDL进行低级建模的经验,包括闪耀灯和流水灯两个模块的代码实现,强调了一个功能模块仅负责单一功能的原则。

本文分享了使用VerilogHDL进行低级建模的经验,包括闪耀灯和流水灯两个模块的代码实现,强调了一个功能模块仅负责单一功能的原则。

7965

7965

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?