一、实验设备

FPGA开发平台、计算机、其它外接器件

二、需求分析(选题的意义、功能要求等。。。这里有点水,小伙伴们可以选择性跳过)

选题的意义:个人认为本项目(《数字时钟》)的选题意义有二,其一,时钟和闹钟早已是老生常谈的日常工具,利用课堂上所学习的知识贯通运用到现实生活中,作为操作实践,具有一定的现实意义;其二,数字时钟的功能设计囊括了数码管、LCD屏、开关运用、管教分配等知识,能够对本学期所学的实验知识做一个挽接,在知识的总结上也具备一定意义;

功能要求:

1.用数码管显示时、分、秒:分为两个界面,即时钟界面以及闹钟设置界面,显示时钟的时分秒以及闹钟的时分秒,可以通过开关切换显示,是项目的基本功能;

2.能按比例缩短时间调试:调控时钟或闹钟的频跳速度,方便演示和调试;

3.闹钟功能:用户可以通过sw8切换进入闹钟界面,再利用sw1-3设定具体的闹钟时间,到点即响,同样是项目的基本功能;

4.用LCD屏显示日期(年月日)以及祝福语:作为时钟,显示年月日的功能个人觉得也是有必要的,另外关于祝福语,我们对实验和知识的学习其实本身就是快乐的过程,生活也没有必要每天都过得毫无色彩、千篇一律,所以怀揣着这份情怀呢,我在本项目中加了一个显示祝福语的功能,意在表达自己的这份对科学和生活的热爱以及学习的热情。

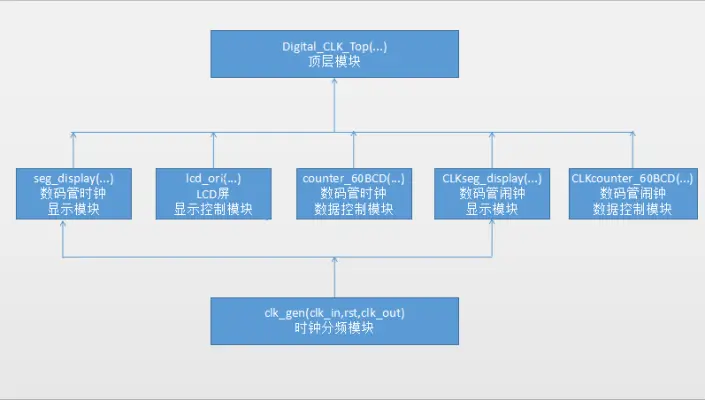

三、系统框架介绍(系统结构图,各模块的功能及端口介绍,等)

系统结构图如下所示:

各模块的功能及端口介绍:

(这里的模块功能和端口做简要的介绍,详细的用法请移步至《设计思路》部分)

1.Digital_CLK_Top(clk_50M, Reset_n, seg7,ledcom,key,beep,

LCD_ON1,LCD_BLON1,LCD_RS1,LCD_RW1,LCD_EN1,LCD_DATA1);

功能:顶层模块,调用其他子模块,统筹整个系统的功能;

端口:

clk_50M, //系统时钟输入

Reset_n, //系统复位输入

seg7, //数码管显示输出位

ledcom, //数码管位置调控输出位

key, //开关输入号位,主要使用于CLKcounter_60BCD

beep, //蜂鸣器输出信号

LCD_ON1, //LCD供电电源开关

LCD_BLON1, //LCD背景电源开关

LCD_RS1, //寄存器选择信号

LCD_RW1, //液晶读写信号

LCD_EN1, //液晶时钟信号

LCD_DATA1, //LCD的数据端口

2.lcd_ori(LCD_ON,LCD_BLON,LCD_RS,LCD_RW,LCD_EN,LCD_DATA,CLK);

功能:LCD屏显示控制模块,用于控制LCD屏显示年月日以及祝福语;

端口:

LCD_ON, //LCD供电电源开关

LCD_BLON, //LCD背景电源开关

LCD_RS, //寄存器选择信号

LCD_RW, //液晶读写信号

LCD_EN, //液晶时钟信号

LCD_DATA, //LCD的数据端口

CLK, //模块时钟输入(项目中输入的是clk_50M)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2949

2949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?