一种基于电荷俘获存储器和氧化物薄膜晶体管的集成显示器驱动电路低功耗设计新策略

1. 引言

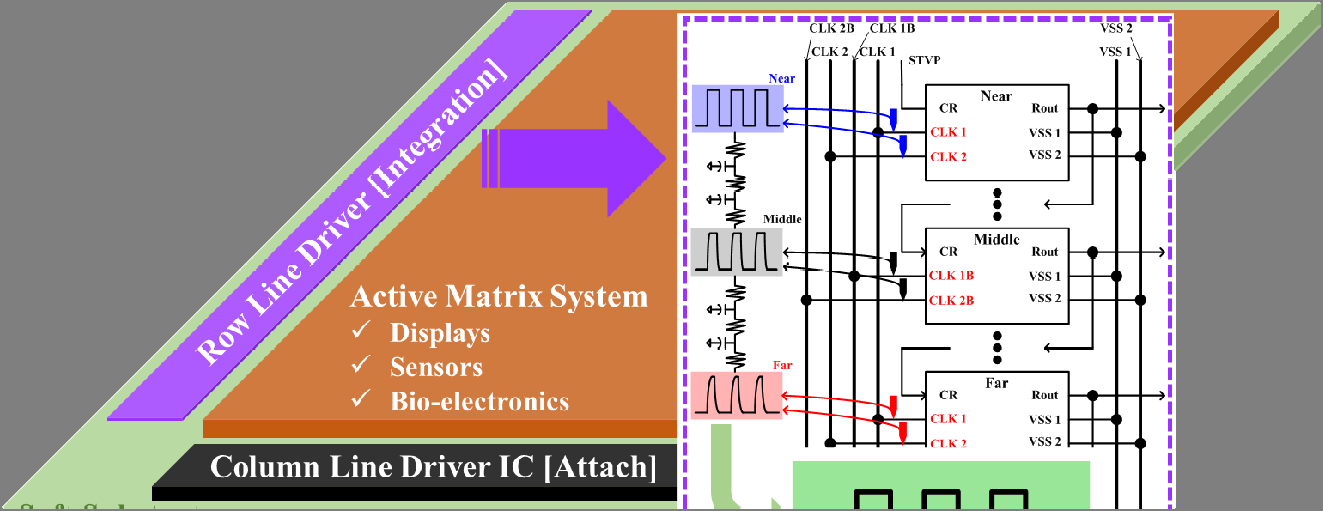

近年来,许多研究人员正在开发使用柔性(可弯曲或可拉伸)衬底的有源矩阵(AM)系统,以应用于显示器或生物电子应用。为了实现这类系统,需要将由薄膜晶体管(TFT)构成的行线驱动器进行集成。但与多晶硅晶体管相比,由于薄膜晶体管具有相对较高的驱动电压和较低的电流驱动能力,这些电路存在功耗高的缺点。

良率是另一个技术问题。使用集成行线驱动器的有源矩阵系统的良率随着集成电路中器件密度的降低而提高。这一趋势对于柔性电子器件尤为重要,因为密度会影响其耐久性。因此,我们提出了一种包含集成过程和器件的新电路设计平台,并为解决这些技术问题提供了有力的替代方案。

2. 读出调制方法的概念

使用薄膜晶体管的移位寄存器等集成电路需要许多时钟线,如图1所示,以补偿薄膜晶体管性能的不足。由时钟线引起的功耗占总功耗的比例超过60%[ref.1]。

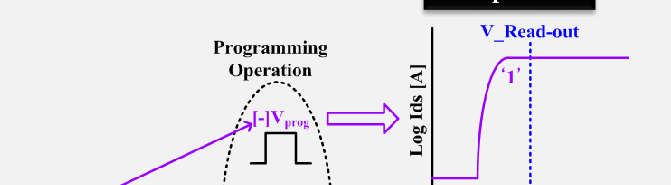

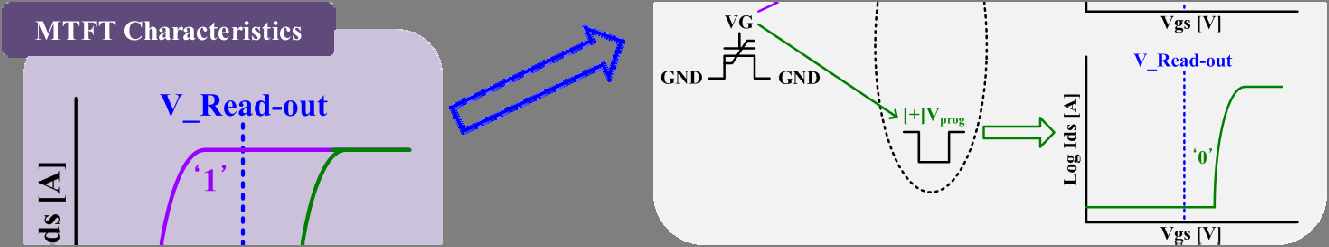

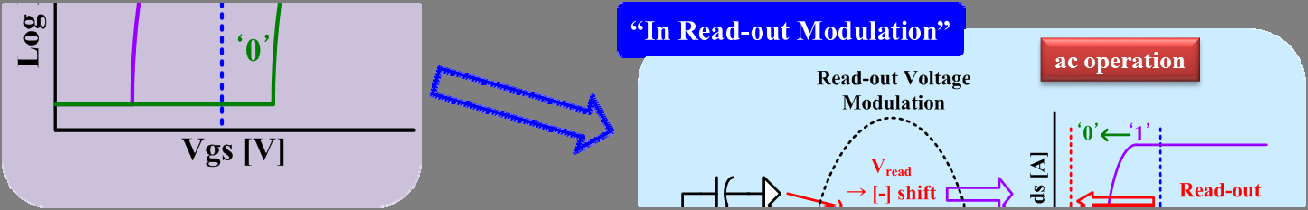

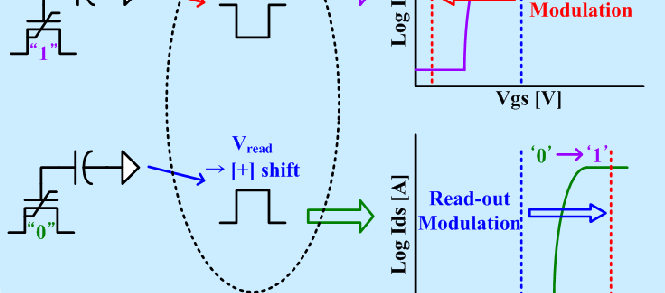

从这一观点出发,我们提出了一种利用非易失性记忆体 (NVM)薄膜晶体管替代大量时钟线的读出调制方法,以最小化时钟功耗。图2描述了读出调制概念。读出调制操作原理可解释如下;

- 1st:NVM TFT编程(设置‘1’)

- 2nd:读出操作(正常读出‘1’)

- 3rd:负向读出电压调制(调制后读出‘0’)

显示器中移位寄存器的输出信号在大部分工作时间内通常保持在“关”状态。第一步和第二步操作对应于RoM方案中的“关”状态,且不引入时钟信号。仅在非常短的工作时间内,输出信号会切换到“开”状态。第三步操作对应于使用非易失性存储薄膜晶体管的RoM方案中的这一“开”状态。第二步和第三步操作的顺序可根据情况重新排列。采用此方法,非易失性存储薄膜晶体管的逻辑状态可以立即调制并返回初始状态,而无需刷新事件。

在这些操作中,用更少的器件且无需额外时钟来实现只读存储器方法的控制模块非常重要。可以通过引入众所周知的电路技术(如升压保持或电容耦合[ref. 3])来实现该控制模块。我们还可以利用来自其他级的相邻信号,例如输出或节点信号[ref 3]。通过这些策略,可以降低时钟线的功耗,并提高有源矩阵系统的良率。

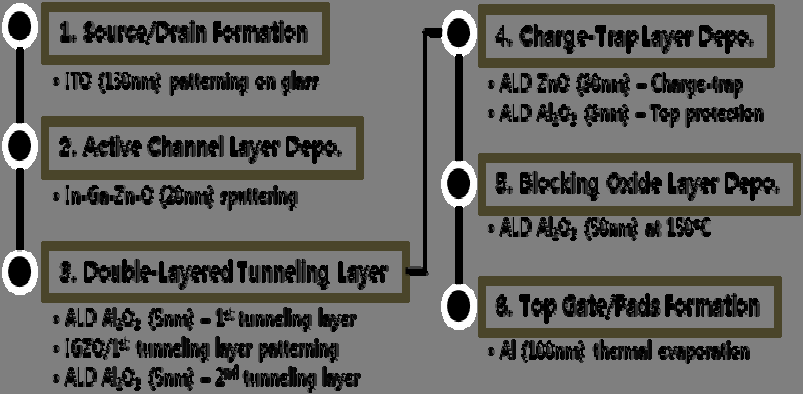

我们优化了集成过程,以验证只读存储器方法的可行性。采用电荷俘获型存储TFT(CTM‐TFTs)和氧化物薄膜晶体管(OxTFT)作为控制器件[ref. 4~ 5]。由CTM‐TFTs和OxTFTs组成的测试电路经过专门设计,以验证提出的RoM方案。

3. 制造与测试

图3和图4展示了完整的工艺流程分别用于制造只读存储测试电路和集成电路的横截面示意图。典型的器件特性和估算的器件参数分别总结于图5和表1中。图6显示了电路原理图、CTM‐TFT编程的时序图以及RoM操作时序图。该测试电路基于伪反相器设计,电路输出随只读存储器方法而变化。图7解释了详细的工作原理,其中假设CTM‐TFT已被编程为“1”。

| 氧化物薄膜晶体管 | 存储器 | |

|---|---|---|

| Vth [V] | -1.57 | |

| μ [cm²/V·s] | 13.7 | |

| S.S [V/十倍频] | 0.13 | |

| 存储器窗口 [V] | 18.1 |

表1. 器件特性总结 [W/L = 40μm/20μm]

(a) 氧化物薄膜晶体管 [W/L=40μm/20μm]

(b) 非易失性存储薄膜晶体管 [W/L=40μm/20μm]

OxTFT [W/L=40μm/20μm],(b) NVM TFT [W/L=40μm/20μm])

OxTFT [W/L=40μm/20μm],(b) NVM TFT [W/L=40μm/20μm])

(a) 示意图

(b) NVM TFT编程的时序图

(c) RoM操作时序图

(a) NVM TFT编程(置为“1”)

(b) RoM操作时序图

(c) 公共读出

(d) 读出调制 [(‐)shift]

图8显示了已制备的测试电路的测试单元组(TEG)设计和照片图像。考虑到OxTFTs的器件特性,n‐only反相器的上拉与下拉薄膜晶体管的比例确定为1:4。反相器中下拉薄膜晶体管的尺寸设计为W/L=2,000 μm/20μm,以考虑测量装置的寄生负载。CTM‐TFT和Ccoup分别设计为W/L=500 μm/20 μm和12皮法,以防止在向测试电路施加控制信号时产生耦合效应。

4. 实验结果

图9(a) 描述了测量测试电路的工作条件。工作电压由CTM‐TFTs和OxTFTs的特性决定。正向编程和正向只读模式的相反条件也在图9(b)中显示。

(a) 负向编程和负向只读模式

(b) 正向编程和正向只读模式

图10和图11分别展示了负向编程和正向编程情况下基本的RoM操作。当CTM‐TFT的读出电压通过Vin信号向负方向移动时,如图10所示,由于Ox2 TFT(下拉)在RoM操作中关断,反相器的输出产生正向信号。正向编程的RoM操作(图11)则表现出与负向编程(图10)相反的输出。在RoM操作的时间持续从10秒变化到160 μ秒的情况下,对输出波形进行了评估。如图所示,测试电路在不同频率范围内均能良好地运行RoM方案。

5. 结论与讨论

我们提出并验证了读出调制方法以最小化时钟功耗并提高有源矩阵系统的良率。根据获得的频率特性结果,成功验证了只读存储器方法的技术可行性。

所提出的只读存储器方法的技术目的不仅限于薄膜晶体管的电路集成领域,还可以扩展到无线电力传输、可植入生物电子系统和物联网连接设备等多个领域。从这一角度来看,通过优化高频特性和详细的时序裕度可控性,可以开发出多种利用RoM方案的应用电路。

尽管需要额外准备制造工艺以将OxTFTs与CTM‐TFTs集成,但从低功耗的角度来看,读出调制方法可为有源矩阵系统带来有效优势,尤其适用于柔性电子器件。因此,读出调制方法可成为采用薄膜晶体管的集成电路设计的一种有前景的策略。

906

906

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?