本章主要介绍处理器硬件的设计,所以可能会比较简略。主要以Y86-64为模板讲解一个cpu大概是如何实现的。

- 内存从概念上来说是一个很大的字节数组,保存着程序和数据。Y86-64程序用虚拟地址来引用内存位置。

- 定义一个指令集。类似第三章中讲的汇编指令。并为指令编码,设置异常处理等。

- 使用HCL(硬件控制语言)来描述不同处理器设计的控制逻辑。

- 实现Y86-64的顺序实现(SEQ)。在每个时钟周期上, 其处理一条完整指令所需的所有步骤。因此时钟周期频率会低到不可接受。

- 将处理组织成阶段:

- 取指(fetch):取指阶段从内存读取指令字节,地址为程序计数器(PC)的值。

- 译码(decode):译码阶段从寄存器文件读入最多两个操作数。

- 执行(execute):在执行阶段,ALU要么执行指令指明的操作,计算内存引用的有效地址,要么增加或减少栈指针。

- 访存(memory):访存阶段可以将数据写入内存,或者从内存读出数据。

- 写回(write back):写回阶段最多可以写两个结果到寄存器文件。

- 更新PC(PC update):将PC设置成下一条指令的地址。

- 白色方框表示时钟寄存器。

- 浅蓝色方框表示硬件单元。

- 控制逻辑块用灰色圆角矩形表示。

- 线路的名字在白色圆圈中说明。

- 宽度为字长的数据连接用中等粗度的线表示。

- 宽度为字节或更窄的数据连接用细线表示。

- 单个位的连接用虚线来表示。

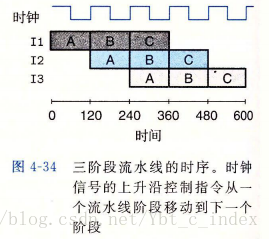

- 流水线化的一个重要特性就是提高了系统的吞吐量(throughput),不过它也会轻微的增加延迟(latency)。如下图是一个流水线的图示

- 流水线的局限性: 理想化的流水线系统是很好的,但是存在其他因素,会降低流水线的效率。

- 不一致的划分,即每个阶段的延迟不同。

- 流水线过深,收益反而下降。阶段划分过多。

由于本章内容比较偏硬件和底层,不好总结,所以就大概写这些吧,后面的流水线实现等等,建议直接看书。

本文详细介绍了基于Y86-64的处理器设计过程,包括指令集定义、异常处理设置、控制逻辑描述及流水线实现。通过取指、译码、执行、访存、写回和更新PC六个阶段,阐述了处理器如何在每个时钟周期处理指令。同时,分析了流水线化提高系统吞吐量的原理及其局限性。

本文详细介绍了基于Y86-64的处理器设计过程,包括指令集定义、异常处理设置、控制逻辑描述及流水线实现。通过取指、译码、执行、访存、写回和更新PC六个阶段,阐述了处理器如何在每个时钟周期处理指令。同时,分析了流水线化提高系统吞吐量的原理及其局限性。

806

806

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?