快速体验

- 打开 InsCode(快马)平台 https://www.inscode.net

- 输入框内输入如下内容:

开发一个基于浏览器的数字电路教学工具,核心功能包括:1. 可视化锁存器电路图(SR/D/T型)2. 交互式真值表生成器 3. Verilog代码自动生成(支持Kimi/DeepSeek模型)4. 时序波形动态演示 5. 一键导出工程文件。要求界面左侧为电路搭建区,右侧实时显示代码和波形,支持通过自然语言描述自动生成对应锁存器模块(例如'生成一个带异步复位的D锁存器')。 - 点击'项目生成'按钮,等待项目生成完整后预览效果

最近在准备数字电路课程的教学材料时,发现学生普遍对锁存器这个概念理解起来比较困难。传统的教学方式需要手动编写Verilog代码、绘制电路图、分析波形,整个过程耗时耗力。于是我想尝试用InsCode(快马)平台来简化这个流程,没想到效果出奇的好。

-

锁存器教学痛点分析 锁存器作为时序电路的基础组件,学生需要同时理解其电路结构、真值表、时序特性等多个维度的知识。传统方式需要分别在多个工具间切换:用Visio画电路图、用ModelSim仿真波形、用文本编辑器写代码,效率低下且容易出错。

-

快马解决方案设计 在快马平台上搭建了一个集成化教学工具,主要包含五个功能模块:

- 左侧画布区支持拖拽搭建SR/D/T型锁存器电路

- 中部的真值表会随电路变化实时更新

- 右侧代码区自动生成对应Verilog/VHDL代码

- 底部波形图动态展示时钟、输入输出信号变化

-

支持通过自然语言指令修改电路特性(如"添加低电平有效复位端")

-

关键实现技术 平台的核心优势在于AI辅助开发:

- 使用Kimi模型解析自然语言指令,自动补全电路细节

- 基于DeepSeek模型生成符合IEEE标准的HDL代码

- 内置的数字电路引擎实时计算真值表和时序

-

SVG动态渲染技术实现可视化交互

-

典型使用场景示例 当讲解D锁存器的数据保持特性时:

- 在AI对话框输入"需要时钟上升沿触发的D锁存器"

- 系统自动生成带有CLK端口的电路图

- 拖动D端输入信号,观察Q端输出如何锁存

-

切换至波形视图,动态演示建立/保持时间要求 整个过程无需手动编写一行代码。

-

教学效果对比 与传统方式相比显著提升效率:

- 电路设计时间从30分钟缩短到3分钟

- 学生通过交互操作直观理解亚稳态问题

- 导出工程文件功能方便课后复习

- 支持快速切换不同类型的锁存器对比教学

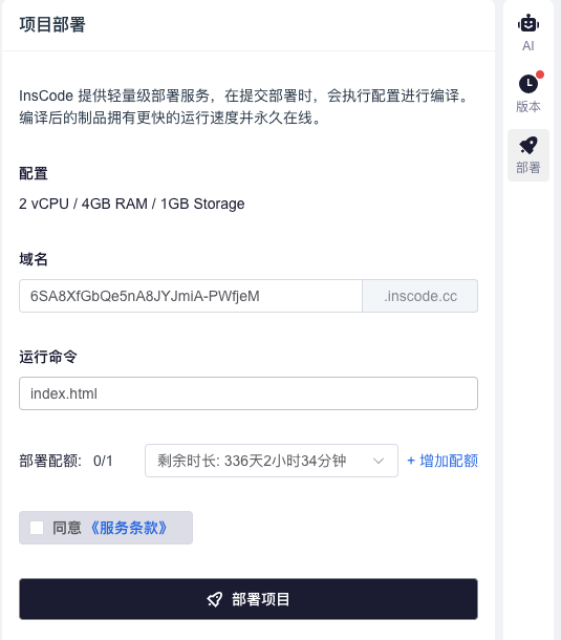

实际体验中发现,平台的一键部署功能特别适合这类需要持续展示的教学应用。完成开发后点击部署按钮,系统会自动生成可访问的URL,学生用浏览器就能直接操作,不需要安装任何仿真软件。

这个案例让我意识到,InsCode(快马)平台特别适合开发数字电路类的教学工具。它不仅解决了多工具协作的繁琐问题,更重要的是通过AI+可视化的方式,让抽象的逻辑概念变得触手可及。对于想要尝试硬件教学创新的老师,或者自学数字电路的同学,这个方案都值得一试。

快速体验

- 打开 InsCode(快马)平台 https://www.inscode.net

- 输入框内输入如下内容:

开发一个基于浏览器的数字电路教学工具,核心功能包括:1. 可视化锁存器电路图(SR/D/T型)2. 交互式真值表生成器 3. Verilog代码自动生成(支持Kimi/DeepSeek模型)4. 时序波形动态演示 5. 一键导出工程文件。要求界面左侧为电路搭建区,右侧实时显示代码和波形,支持通过自然语言描述自动生成对应锁存器模块(例如'生成一个带异步复位的D锁存器')。 - 点击'项目生成'按钮,等待项目生成完整后预览效果

创作声明:本文部分内容由AI辅助生成(AIGC),仅供参考

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?