最近需要学习SystemVerilog,入门是SV_LAB。因此在EETOP搜集了一些学习资料。

相关资料 SV_LAB、SV_TestbenchGuider、SV_LABGuider,是可以在EETOP搜索。

快捷跳转如下:

(1)2016最新Synopsys 官方Lab http://bbs.eetop.cn/thread-614054-1-1.html

(2)SystemVerilog Testbench Student Guide & Lab Guide http://bbs.eetop.cn/forum.php?mod=viewthread&tid=357937

篇中所说的绿皮书,指的是《SystemVerilog验证 测试平台编写指南》的中文版,张春...译的那本;

这里只是学习笔记,方便自己查看,写有不周,望理解。

目录

二、测试平台顶层代码

一、DUT

1.1 DUT端口

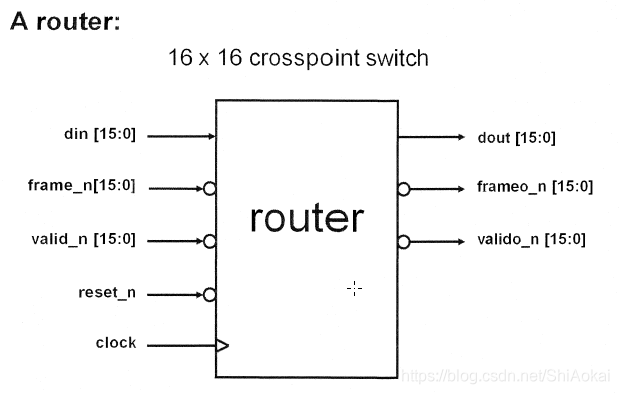

由于第一个LAB比较简单,这里先介绍一下DUT;

DUT是一个16进16出的路由器,你看din、frame_n、valid_n都是16位,din一位就表示一个路由的输入口,dout同理。

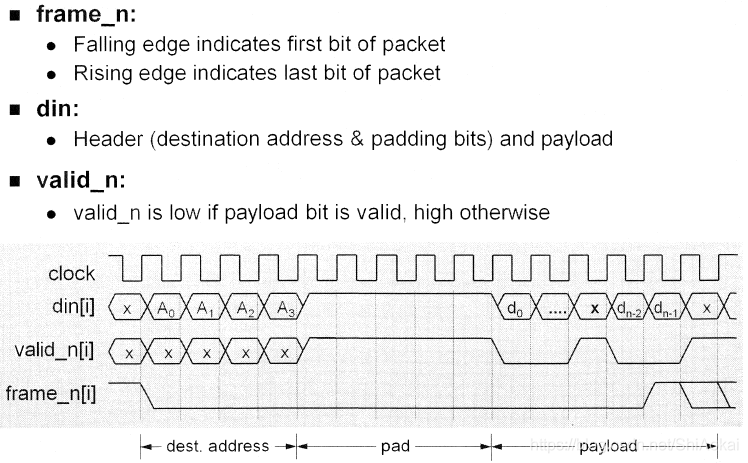

1.2 DUT输入时序

输入时序中,从frame_n拉低开始,在frame_n拉高结束,注意最后一个数据时frame_n是为高的。

输入时序中,din分为三个部分:(1)addr 占4个周期,(2)pad 占5个周期,(3)data 长度不定。

输入时序中,valid_n在(1)输入addr阶段时不关注,在(2)输入pad阶段为高,在(3)输入数据阶段指示数据是否有效。

其中地址4位,范围0~15,表示数据要从哪个dout转发出去。

1.3 DUT输出时序

输出时序,相对简单一些,使用frameo_n下降沿表示开始,frameo_n上升沿表示结束。

然后,转发时序中只包含data阶段,在传输过程中valid_n用来指示数据线是否有效。

这篇博客介绍了SystemVerilog的学习资源和SV_LAB的第一个实验,详细解析了DUT(Design Under Test)的端口、输入时序、输出时序和接口代码,以及测试平台的顶层代码定义、时钟生成、接口连接和驱动代码。内容涵盖了数字电路测试平台的搭建和时序控制。

这篇博客介绍了SystemVerilog的学习资源和SV_LAB的第一个实验,详细解析了DUT(Design Under Test)的端口、输入时序、输出时序和接口代码,以及测试平台的顶层代码定义、时钟生成、接口连接和驱动代码。内容涵盖了数字电路测试平台的搭建和时序控制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1518

1518