快速体验

- 打开 InsCode(快马)平台 https://www.inscode.net

- 输入框输入如下内容

帮我设计一个同相迟滞比较器电路,用于消除信号噪声导致的输出抖动。系统交互细节:1.设置高低阈值电压VL=1.3V和VH=1.7V 2.计算反馈电阻网络参数 3.验证输出翻转逻辑。注意事项:需考虑电阻容差和比较器输入失调电压的影响。 - 点击'项目生成'按钮,等待项目生成完整后预览效果

迟滞比较器是电子电路中常用的一种抗干扰设计,通过设置高低两个阈值电压来避免信号在临界点附近抖动。这里我们就来详细分析同相迟滞比较器的设计要点和实现过程。

-

设计原理分析 迟滞比较器的核心在于正反馈网络的设计。当输入信号超过上限阈值VH时输出翻转为高电平,只有当信号低于下限阈值VL时才会重新翻转为低电平。这种特性特别适合处理带有噪声的缓慢变化信号。

-

关键参数确定 首先需要明确设计要求中的阈值电压值。在本例中设定VL=1.3V,VH=1.7V。这两个值决定了电路的迟滞窗口大小,窗口越大抗干扰能力越强,但也会降低电路的灵敏度。

-

电阻网络计算 电阻选择需要考虑功耗和精度两方面因素。通常选用兆欧级电阻来降低功耗,但要注意高阻值会放大失调电压的影响。通过建立输入高低电平时的等效电路,可以推导出电阻比例关系式。

-

器件选型要点 选择比较器时要特别注意其输入失调电压参数,这个误差会直接影响阈值精度。对于本例中的TLV7041器件,还需注意其漏极开路输出特性,需要外接上拉电阻。

-

仿真验证方法 完成设计后需要通过仿真验证翻转点是否正确。建议先用直流扫描观察传输特性曲线,再输入带有噪声的信号测试实际抗干扰效果。

-

实际应用优化 在实际PCB布局时,反馈电阻应尽量靠近比较器放置以减少寄生效应。对于高精度应用,建议使用0.1%精度的电阻并考虑温度系数影响。

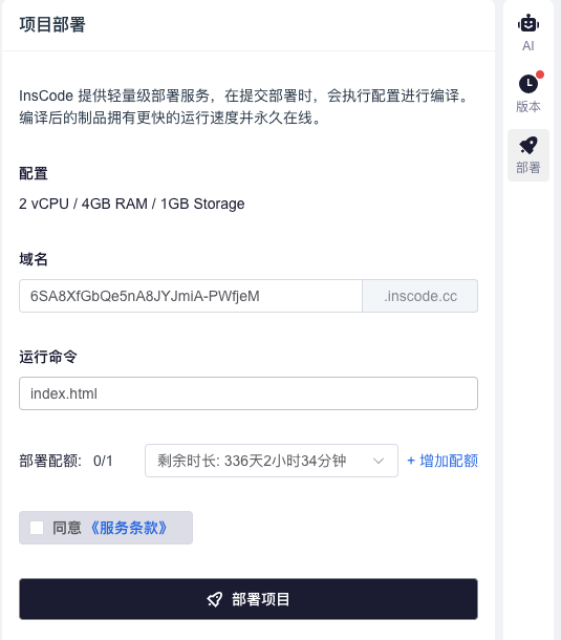

在InsCode(快马)平台上,我们可以快速搭建这个电路的设计环境,一键部署仿真验证非常方便。平台内置的元件库和仿真工具让电路设计变得简单直观,即使是初学者也能轻松上手。我在实际操作中发现,从设计到验证的完整流程只需要几分钟就能完成,大大提高了学习效率。

1278

1278

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?