文章目录

代码

代码一

组合逻辑链过长 可能导致 setup violation。

module test(

input clk,

input [7:0] a, b, c,

output reg [15:0] y

);

reg [15:0] tmp;

always @(posedge clk) begin

// 一大串组合逻辑,级联太长

tmp <= (((((((a+b)+c)+a)+b)+c)+a)+b)+c +a;

y <= tmp;

end

endmodule

- 在时序收敛分析时,触发器的建立时间(setuptime)是在时钟信号到来之前数据需要保持稳定的时间。但是,在上例的RTL中可以看到,寄存器前有很长的组合逻辑电路,这可能(若时钟频率较高)导致时钟到来时组合逻辑还没有计算完成,而导致setup violation。

代码二

- 通过 流水线寄存器 来优化。打断长链,流水线化:

module test(

input clk,

input [7:0] a, b, c,

output reg [15:0] y

);

reg [15:0] tmp1, tmp2;

always @(posedge clk) begin

// 第一段逻辑

tmp1 <= (((a+b)+c)+a)+b;

// 第二段逻辑

tmp2 <= ((c+a)+b)+c+a;

// 输出

y <= tmp1 + tmp2;

end

endmodule

效果对比

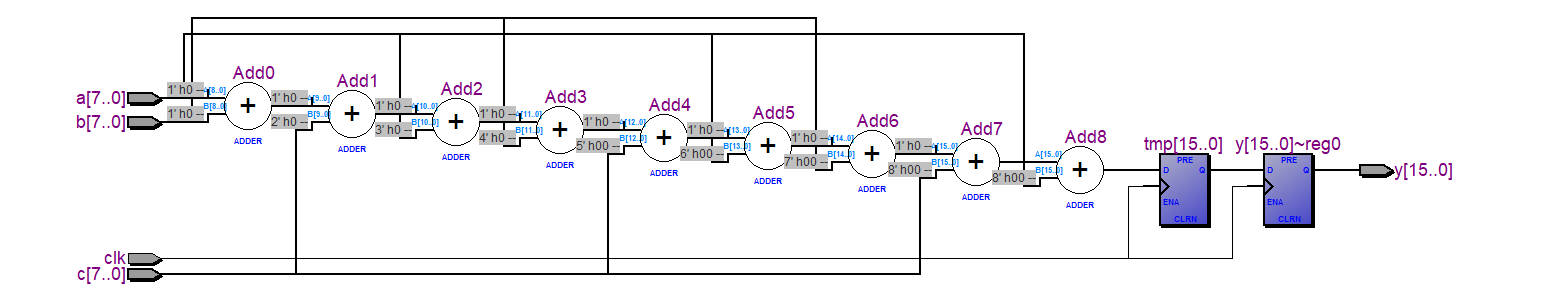

Quaruts

- 下面是在Quaruts上优化前后能跑到的最高频率(基于某款十几年前的芯片):

多角时序分析(Multicorner Timing Analysis)结果

-

对比上表,可以看到,在最坏情况时序裕量(Worst-case Slack)的Minimum Pulse Width 有所提高

-

对比上表,可以看到,在最坏情况时序裕量(Worst-case Slack)的Setup时间也有所提高

-

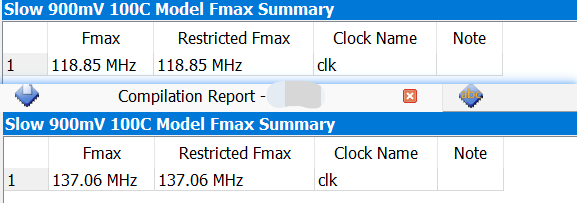

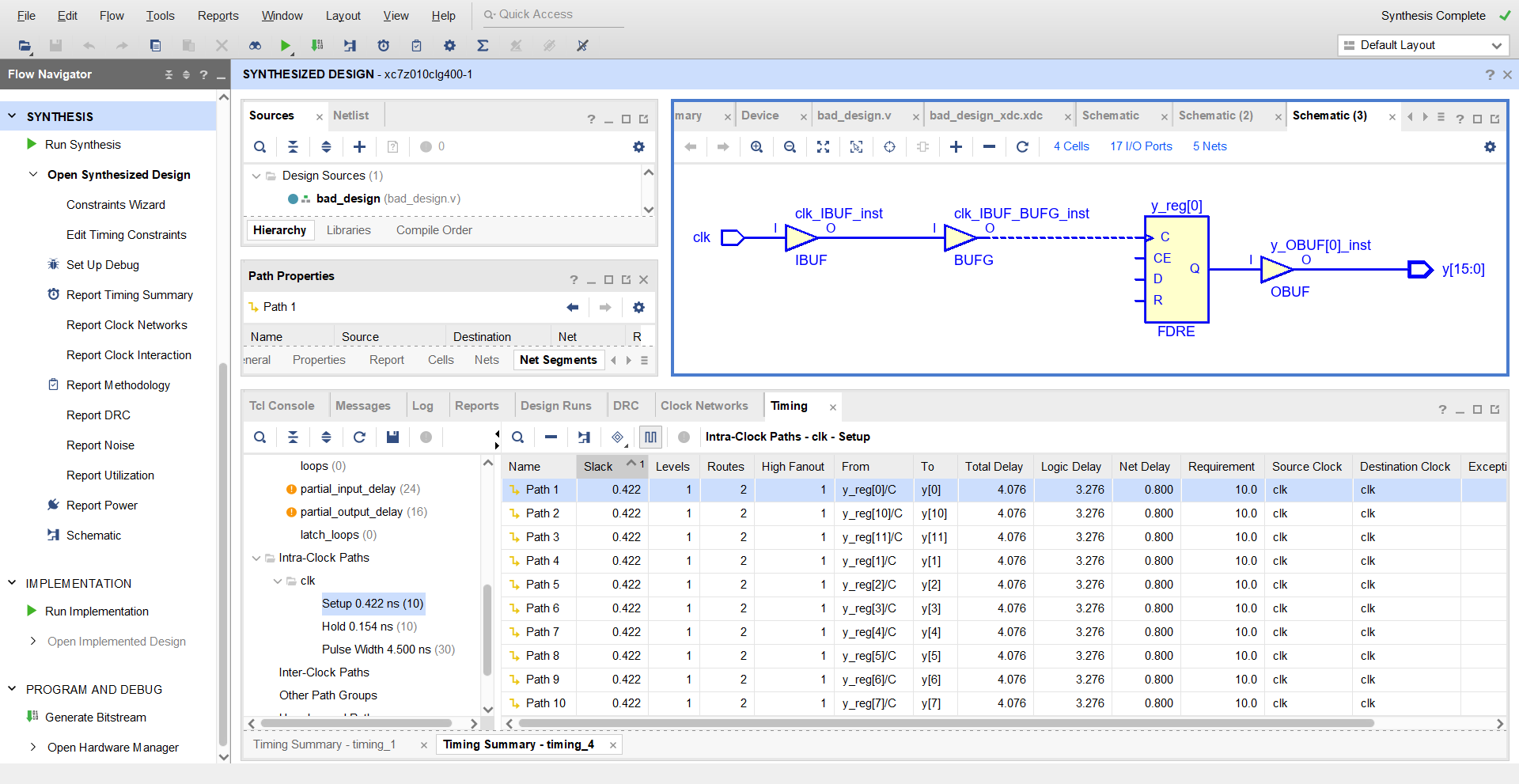

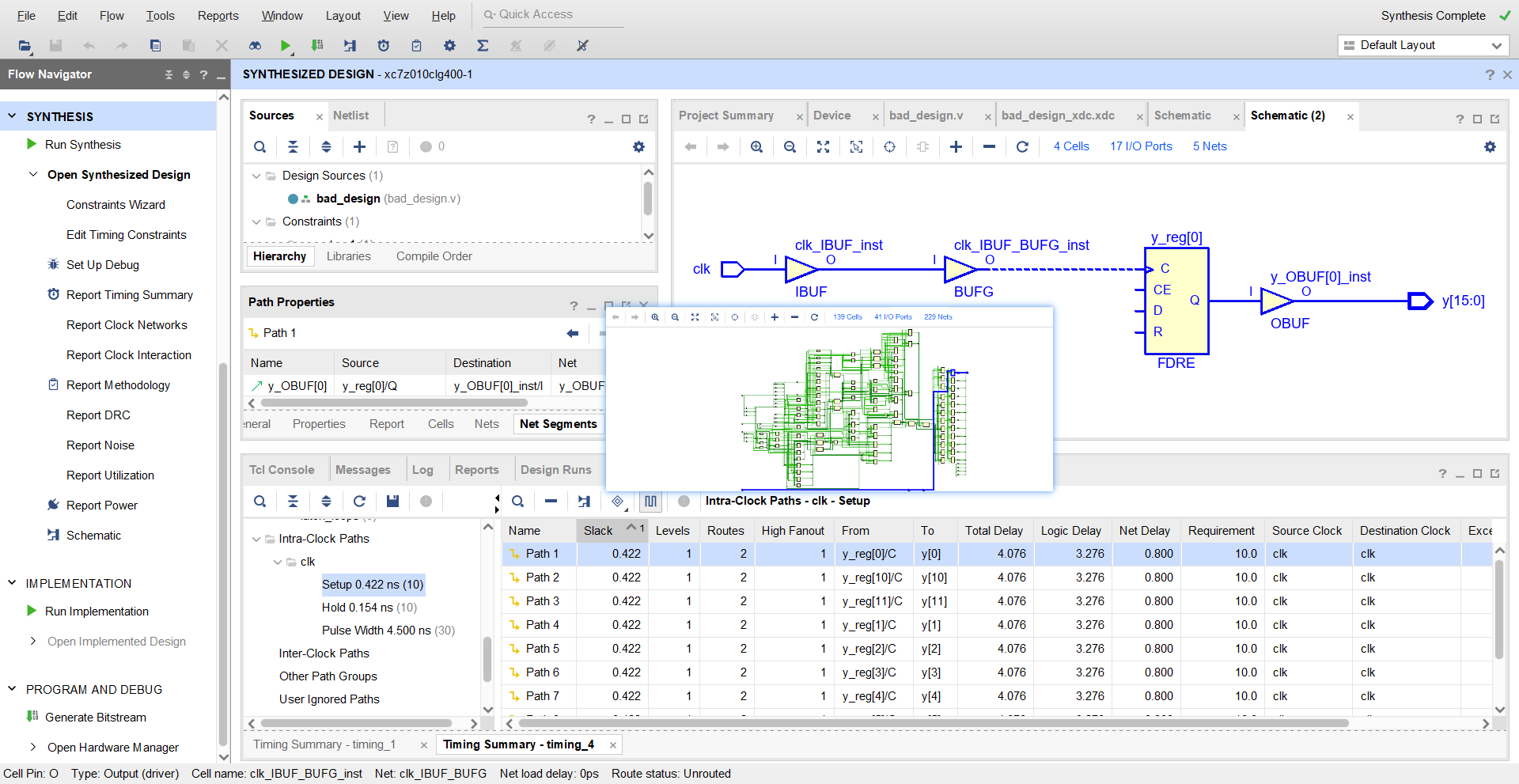

Slack(adj.松弛的;萧条的;n.(绳索的)松弛部分;闲置部分;煤屑) 指在某条时序路径上,实际可用时间 与 所需时间 之间的差值。( T c 2 q T_{c2q} Tc2q: 时钟到输出延迟(寄存器)、 T l o g i c T_{logic} Tlogic: 组合逻辑延迟、 T s e t u p T_{setup} Tsetup: 目标寄存器的建立时间、 T s k e w T_{skew} Tskew: 时钟偏移(可正可负))

- S l a c k = 可用时间 − 所需时间 S l a c k S e t u p = ( T c l o c k + T s k e w ) − ( T c 2 q + T l o g i c + T s e t u p ) Slack = 可用时间 - 所需时间\\ Slack_{Setup} = (T_{clock} + T_{skew}) - (T_{c2q} + T_{logic} + T_{setup}) Slack=可用时间−所需时间SlackSetup=(Tclock+Tskew)−(Tc2q+Tlogic+Tsetup)

-

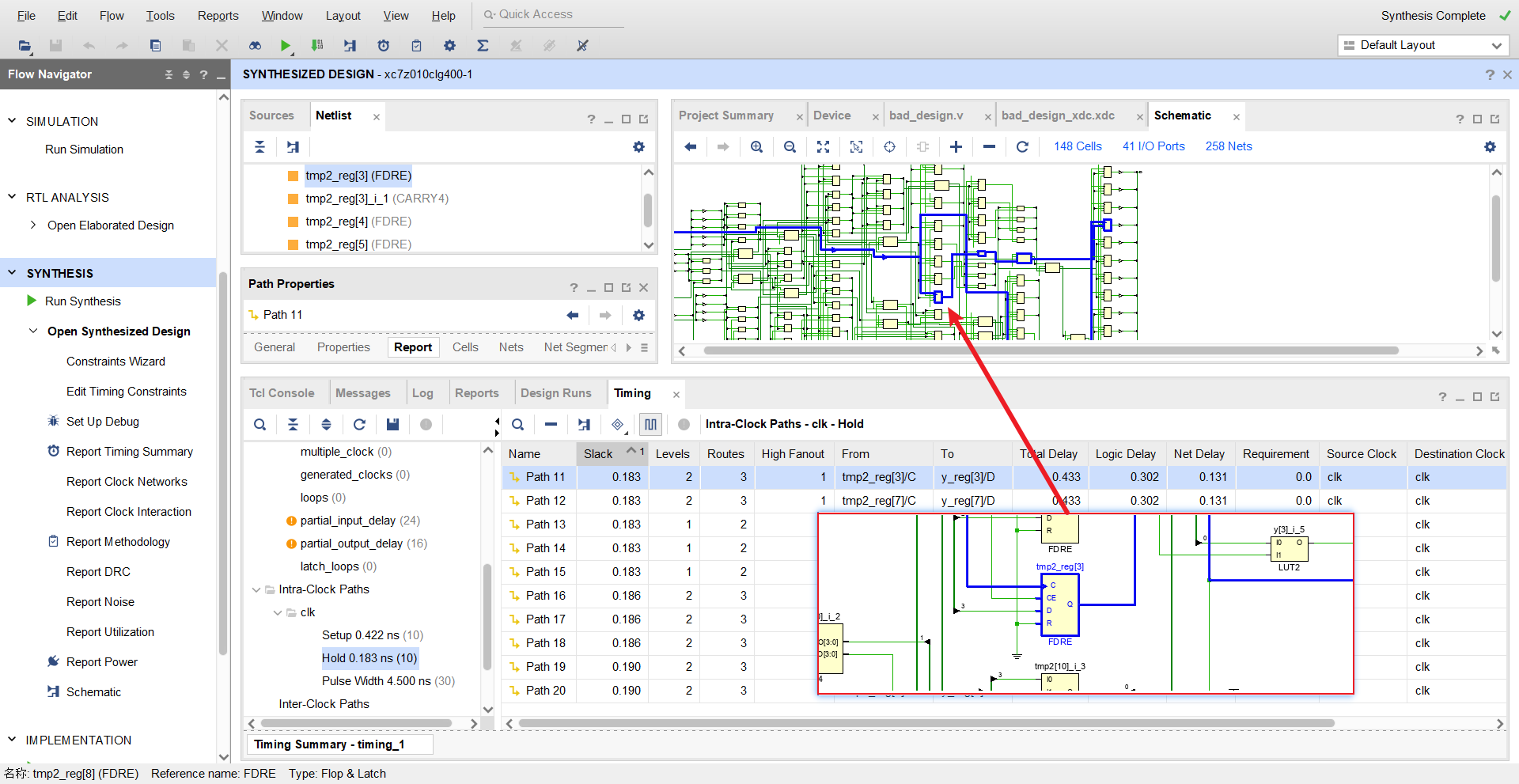

vivado

- 代码一

- 代码二

FPGA长组合链优化与流水线设计

FPGA长组合链优化与流水线设计

4683

4683

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?