题目

描述

在数字芯片设计中,经常把实现特定功能的模块编写成函数,在需要的时候再在主模块中调用,以提高代码的复用性和提高设计的层次,分别后续的修改。

请用函数实现一个4bit数据大小端转换的功能。实现对两个不同的输入分别转换并输出。

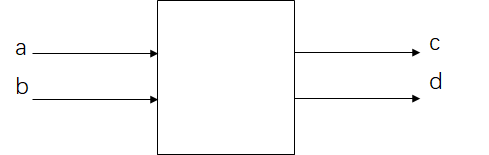

程序的接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

clk:系统时钟

rst_n:异步复位信号,低电平有效

a,b:4bit位宽的无符号数

输出描述:

c,d:8bit位宽的无符号数

题解

大小端理论

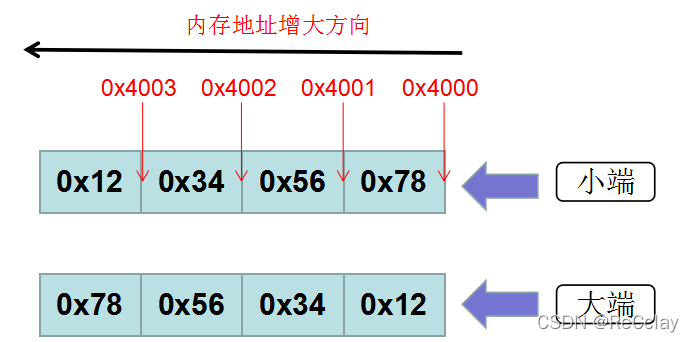

大端是高字节存放到内存的低地址;小端是高字节存放到内存的高地址。

假如现有一32位int型数0x12345678,大小端存放方式如下:

本文介绍了如何使用Verilog HDL编写函数来实现4bit数据的大小端转换。通过理解大端和小端的概念,以及利用Verilog的函数特性,实现了将输入的4bit数据转换为8bit数据的逻辑。文中提供了详细的函数声明和调用方法,并给出了完整的Verilog代码示例。

本文介绍了如何使用Verilog HDL编写函数来实现4bit数据的大小端转换。通过理解大端和小端的概念,以及利用Verilog的函数特性,实现了将输入的4bit数据转换为8bit数据的逻辑。文中提供了详细的函数声明和调用方法,并给出了完整的Verilog代码示例。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?