题目

描述

在数字芯片设计中,通常把完成特定功能且相对独立的代码编写成子模块,在需要的时候再在主模块中例化使用,以提高代码的可复用性和设计的层次性,方便后续的修改。

请编写一个子模块,将输入两个8bit位宽的变量data_a,data_b,并输出data_a,data_b之中较小的数。并在主模块中例化,实现输出三个8bit输入信号的最小值的功能。

子模块的信号接口图如下:

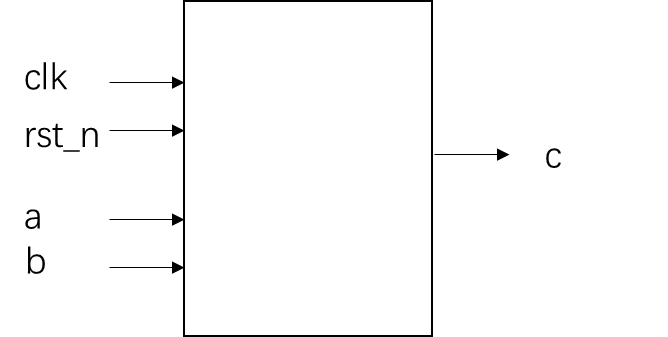

主模块的信号接口图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

clk:系统时钟

rst_n:异步复位信号,低电平有效

a,b,c:8bit位宽的无符号数

输出描述:

d:8bit位宽的无符号数,表示a,b,c中的最小值

题解

易错总结:这里很多习惯于软件思维的人写代码会只例化2次子模块,是将a,b比较之后的结果min_

该博客介绍了数字IC设计中如何使用Verilog HDL编写子模块来实现三输入数的大小比较。强调了在设计时序逻辑电路时,要避免软件思维,理解电路模型和时序逻辑的区别。通过一个具体的例子,解释了错误的做法以及正确的实现方式,并提供了testbench验证。

该博客介绍了数字IC设计中如何使用Verilog HDL编写子模块来实现三输入数的大小比较。强调了在设计时序逻辑电路时,要避免软件思维,理解电路模型和时序逻辑的区别。通过一个具体的例子,解释了错误的做法以及正确的实现方式,并提供了testbench验证。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?