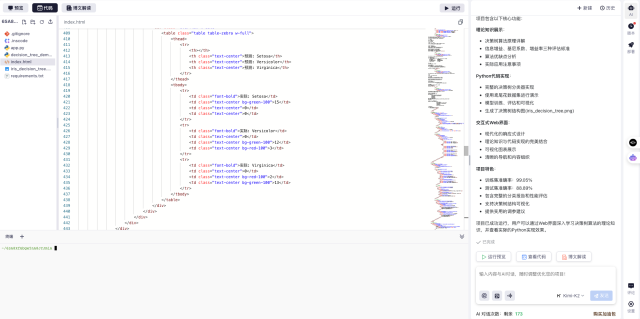

快速体验

- 打开 InsCode(快马)平台 https://www.inscode.net

- 输入框输入如下内容

帮我开发一个布尔函数转换演示工具,用于电子工程专业学生理解标准型转换原理。系统交互细节:1.提供真值表输入区域 2.自动生成最小项/最大项表达式 3.可视化门电路延迟模型 注意事项:需支持与或/或与两种标准型切换 - 点击'项目生成'按钮,等待项目生成完整后预览效果

课程要点解析

-

布尔函数标准型核心概念

最小项之和(SOP)与最大项之积(POS)是两种标准表达形式。通过真值表中输出为1的最小项相加,或输出为0的最大项相乘,可以建立逻辑函数的规范化表达式。实际应用中常需要根据电路设计需求选择更适合的形式。 -

卡诺图化简技巧

使用2^n方格图进行可视化化简时,要注意相邻单元格的格雷码排列规律。组圈时应遵循:圈越大越好、圈数越少越好、允许重叠但必须包含新最小项三大原则。教学中发现学生容易忽略"不能遗漏任意一个1"的基本要求。 -

门电路延迟模型

传输延迟(tpd)和污染延迟(tcd)直接影响电路稳定性。通过建立时间-振幅坐标图,可以直观展示信号跳变时的竞争冒险现象。建议用不同颜色标注各路径延迟,便于分析关键路径。 -

课堂测验常见题型

- 给定真值表求标准型表达式

- 对比SOP/POS形式的门电路实现复杂度

- 根据延迟参数计算建立/保持时间余量

-

判断给定电路是否存在静态/动态冒险

-

课后作业难点突破

综合题通常要求完成从真值表→标准型→门电路→延迟分析的全流程设计。建议先手工推导再使用仿真工具验证,特别注意: - 多输出函数要分别处理每个输出

- 或非/与非实现的代数变换技巧

- 竞争冒险的消除方案选择

学习工具推荐

通过InsCode(快马)平台可以快速创建交互式学习demo,比如输入真值表自动生成门电路图。平台内置的实时预览功能特别适合验证布尔代数变换的正确性,无需本地安装任何软件就能完成电路特性分析。

对于需要展示动态过程的延迟模型,平台的一键部署能力可以直接生成可交互的网页应用,方便用滑动条调节参数观察波形变化。实际测试中,这种可视化方式比静态公式更利于理解时间参数对电路的影响。

795

795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?