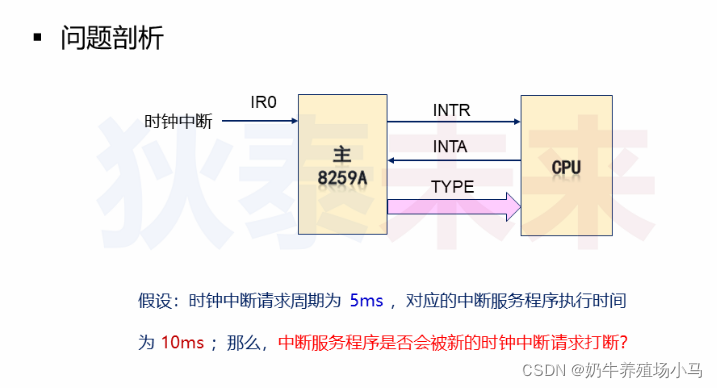

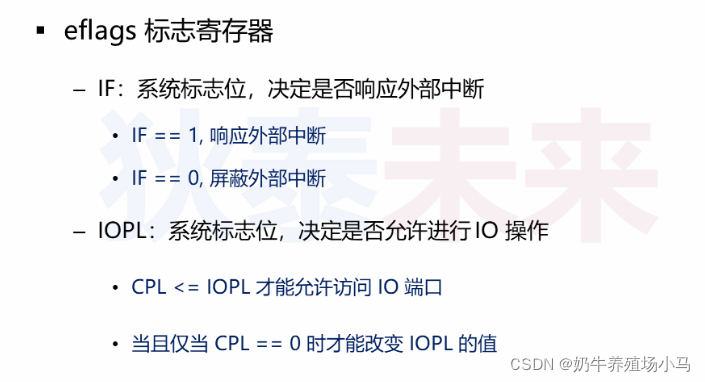

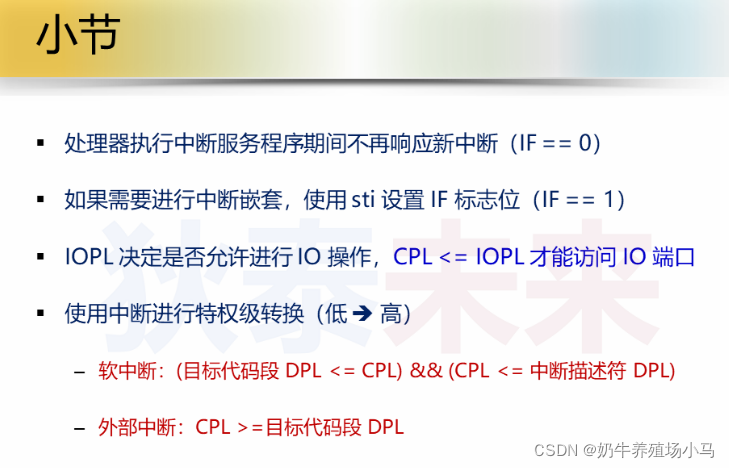

不会,中断整体是由 处理器 与 8259A中断控制器 共同管理的,虽然8259A可以不停的将中断请求发送给处理器,但是处理器有屏蔽中断的开关,只要当前中断处理还没有完成,就可以将IF置0 即不接受其他中断请求。

处理器没有中断优先级的概念,它只有响应与不响应的概念,当在执行中断处理时,屏蔽外部中断请求时 不响应8259A发来的中断请求。相反 当中断服务程序完成时,重新开始响应8259A的中断请求。

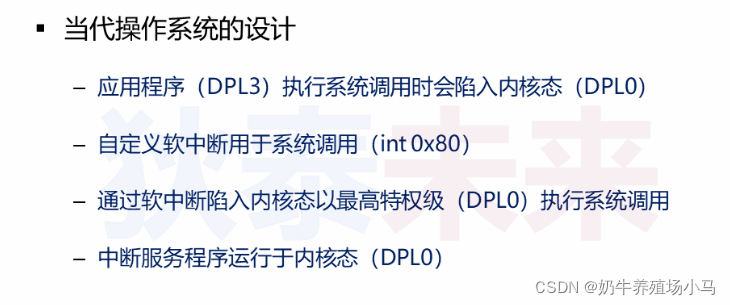

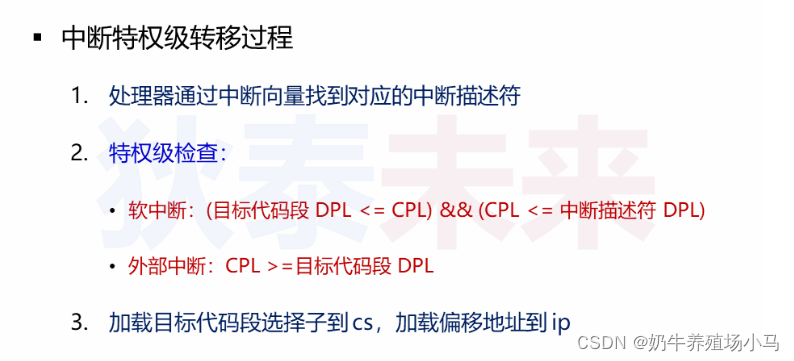

处理器拿到中断向量之后,就会到中断描述符表中查找对应的中断向量,进而找到一个中断描述符,然后继续特权级检查,最后将目标代码段的选择子加载到 cs寄存器,将中断服务程序的偏移地址加载的 ip寄存器,之后就可以执行 中断服务程序了。

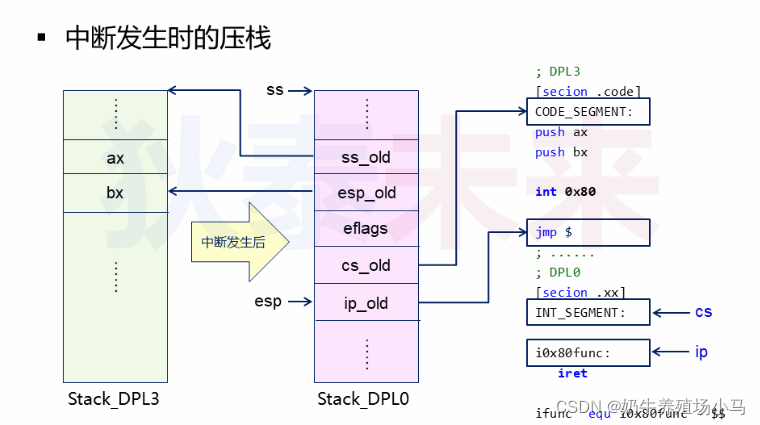

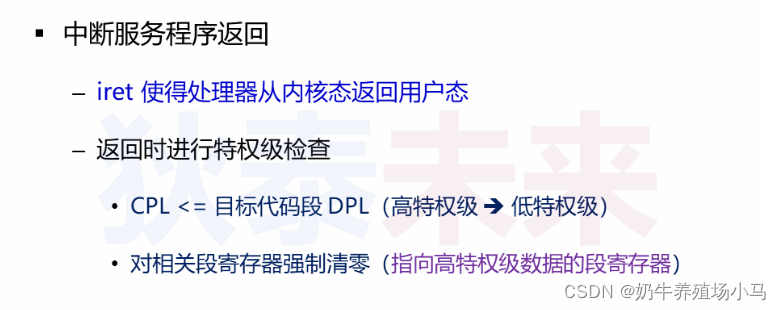

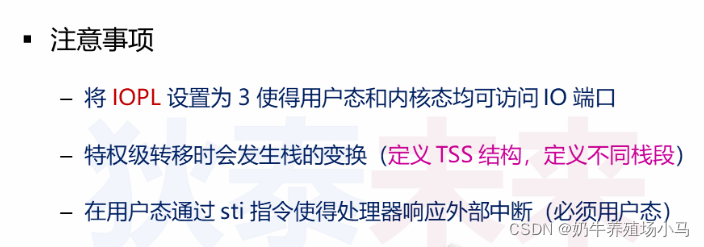

低特权级用户态代码段 执行软中断,此时就会发生特权级转移,转移到高特权级内核态代码段执行,此时 栈就会发生变化,既然特权级要转移到高特权级,那么栈就要使用高特权级的栈,于是相关的寄存器就要入栈,包括ss寄存器(栈基地址) esp寄存器(栈顶指针) 这两个寄存器信息 就是指向了 低特权级的栈,将这些寄存器值 压入高特权级栈中,标志寄存器的值也要入栈(eflags),然后返回地址也要入栈,即 cs寄存器的值 以及ip寄存器的值 也要入栈。至此 就可以取执行中断服务程序了,此时 cs寄存器指向了 内核态代码段, ip寄存器指向了 中断服务程序偏移地址,组合就是中断服务程序的入口地址,然后开始执行中断服务程序,执行到遇到 iret指令后 返回。所以 iret指令执行后 使处理器从内核态 返回到 用户态 ,即从高特权级代码段 切换到 低特权级代码段。

inc.asm

; PIC-8259A Ports

MASTER_ICW1_PORT equ 0x20

MASTER_ICW2_PORT equ 0x21

MASTER_ICW3_PORT equ 0x21

MASTER_ICW4_PORT equ 0x21

MASTER_OCW1_PORT equ 0x21

MASTER_OCW2_PORT equ 0x20

MASTER_OCW3_PORT equ 0x20

SLAVE_ICW1_PORT equ 0xA0

SLAVE_ICW2_PORT

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

654

654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?