集成电路输出开关速度提高以及PCB板密度增加,信号完整性(Signal Integrity) 成为高速数字PCB设计必须关心的主要问题,元器件和PCB板的参数、元器件在PCB板上的布局、高速信号线的布线等因素,都会引起信号完整性的问题,对于PCB布局来说,信号完整性需要提供不影响信号时序或电压的电路板布局,而对电路布线来说,信号完整性则要求提供端接元件、布局策略和布线信息。PCB上信号速度高、端接元件的布局不正确或高速信号的错误布线都会引起信号完整性问题,从而可能使系统输出不正确的数据、电路工作不正常甚至完全不工作,如何在PCB板的设计过程中充分考虑信号完整性的因素,并采取有效的控制措施,已经成为PCB设计的关键性问题。

- 信号完整性问题

良好的信号完整性,是指信号在需要的时候能以正确的时序和电压电平数值做出响应。反之,当信号不能正常响应时,就出现了信号完整性问题。信号完整性问题能导致或直接带来信号失真、定时错误、不正确数据、地址和控制线以及系统误工作,甚至系统崩溃,信号完整性问题不是某单一因素导致的,而是板级设计中多种因素共同引起的。IC的开关速度,端接元件的布局不正确或高速信号的错误布线都会引起信号完整性问题。主要的信号完整性问题包括:延迟、反射、同步切换噪声、振荡、地弹、串扰等。

- 信号完整性的定义

信号完整性是指信号在电路中能以正确的时序和电压做出响应的能力,是信号未受到损伤的一种状态,它表示信号在信号线上的质量。

2.1 延迟(Delay)

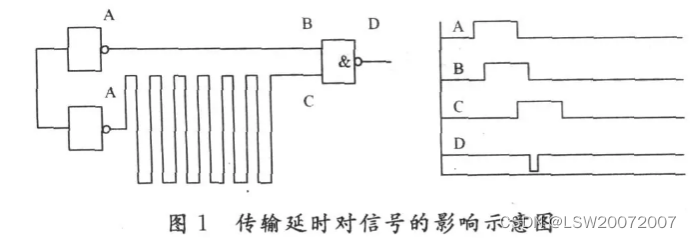

延迟是指信号在PCB板的导线上以有限的速度传输,信号从发送端发出到达接收端,其间存在一个传输延迟。信号的延迟会对系统的时序产生影响,传输延迟主要取决于导线的长度和导线周围介质的介电常数。在高速数字系统中,信号传输线长度是影响时钟脉冲相位差的最直接因素,时钟脉冲相位差是指同时产生的两个时钟信号,到达接收端的时间不同步。时钟脉冲相位差降低了信号沿到达的可预测性,如果时钟脉冲相位差太大,会在接收端产生错误的信号,如图1所示,传输线时延已经成为时钟脉冲周期中的重要部分。

2.2 反射(Reflection)

反射就是子传输线上的回波。当信号延迟时间(Delay)远大于信号跳变时间(Transition Time)时,信号线必须当作传输线。当传输线的特性阻抗与负载阻抗不匹配时,信号功率(电压或电流)的一部分传输到线上并到达负载处,但是有一部分被反射了。若负载阻抗小于原阻抗,反射为负;反之,反射为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面不连续等因素的变化均会导致此类反射。

2.3 同步切换噪声(SSN)

当PCB板上的众多数字信号同步进行切换时(如CPU的数据总线、地址总线等),由于电源线和地线上存在阻抗,会产生同步切换噪声,在地线上还会出现地平面反弹噪声(地弹)。SSN和地弹的强度也取决于集成电路的I/O特性、PCB板电源层和平面层的阻抗以及高速器件在PCB板上的布局和布线方式。

2.4 串扰(Crosstalk)

串扰是两条信号线之间的耦合,信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。串扰噪声源于信号线网之间、信号系统和电源分布系统之间、过孔之间的电磁耦合。串绕有可能引起假时钟,间歇性数据错误等,对邻近信号的传输质量造成影响。实际上,我们并不需要完全消除串绕,只要将其控制在系统所能承受的范围之内就达到目的。PCB板层的参数、信号线间距、驱动端和接收端的电气特性、基线端接方式对串扰都有一定的影响。

2.5 过冲(Overshoot)和下冲(Undershoot)

过冲就是第一个峰值或谷值超过设定电压,对于上升沿,是指最高电压,对于下降沿是指最低电压。下冲是指下一个谷值或峰值超过设定电压。过分的过冲能够引起保护二极管工作,导致其过早的失效。过分的下冲能够引起假的时钟或数据错误(误操作)。

2.6 振荡(Ringing)和环绕振荡(Rounding)

振荡现象是反复出现过冲和下冲。信号的振荡即由线上过渡的电感和电容引起的振荡,属于欠阻尼状态,而环绕振荡,属于过阻尼状态。振荡和环绕振荡同反射一样也是由多种因素引起的,振荡可以通过适当的端接予以减小,但是不可能完全消除。

2.7 地电平反弹噪声和回流噪声

在电路中有较大的电流涌动时会引起地平面反弹噪声,如大量芯片的输出同时开启时,将有一个较大的瞬态电流在芯片与板的电源平面流过,芯片封装与电源平面的电感和电阻会引发电源噪声,这样会在真正的地平面(OV)上产生电压的波动和变化,这个噪声会影响其他元件的动作。负载电容的增大、负载电阻的减小、地电感的增大、同时开关器件数目的增加均会导致地弹的增大。

由于地电平面(包括电源和地)分割,例如地层被分割为数字地、模拟地、屏蔽地等,当数字信号走到模拟地线区域时,就会生成地平面回流噪声。同样,电源层也可能会被分割为2.5V,3.3V,5V等。所以在多电压PCB设计中,对地电平面的反弹噪声和回流噪声需要特别注意。

1475

1475