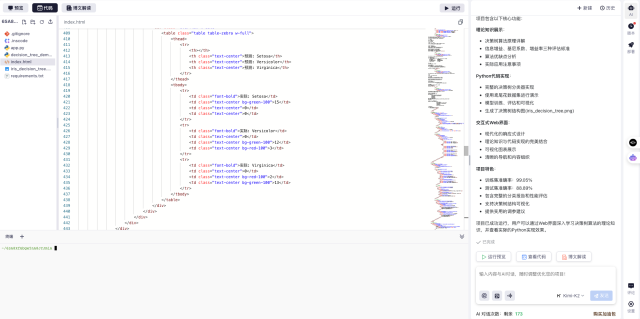

快速体验

- 打开 InsCode(快马)平台 https://www.inscode.net

- 输入框输入如下内容

帮我开发一个数字电路模拟系统,用于展示一位全减器的三种实现方式(异或门组合、74LS138译码器、74LS153选择器)。系统交互细节:1.可切换不同实现方案 2.显示真值表对比 3.提供输入测试功能。注意事项:需标注各芯片引脚连接关系 - 点击'项目生成'按钮,等待项目生成完整后预览效果

设计原理与实现方案

-

基础概念 一位全减器需要处理三个输入(被减数A、减数B、低位借位Ci),输出差值D和新的借位Co。其核心逻辑关系可以表示为:D=A⊕B⊕Ci,Co=A'B + A'Ci + BCi。

-

异或门与非门方案

- 使用两个异或门实现三重异或运算

- 四个与非门组合生成借位信号

- 需注意信号传递延迟对输出稳定性的影响

-

典型连接方式:第一异或门处理A⊕B,第二异或门将结果与Ci异或

-

74LS138译码器方案

- 利用3-8译码器的使能端控制

- 通过或门组合特定输出引脚(Y1/Y2/Y4/Y7)

- 需注意译码器输出为低电平有效

-

优势在于扩展性强,便于构建多位减法器

-

74LS153选择器方案

- 双4选1数据选择器的灵活应用

- 将Ci作为选择控制信号

- 数据输入端按真值表配置高低电平

- 布线时需注意使能端的接地处理

实现要点分析

-

信号处理差异 异或门方案最直观但门电路数量多,译码器方案需要附加逻辑门,选择器方案则更依赖正确的数据输入配置。

-

延迟对比 门电路级联会产生累积延迟,而芯片方案内部延迟更稳定。对于高频应用,建议测量实际传播延迟时间。

-

扩展性考虑 构建多位减法器时,译码器方案可通过级联实现,而异或门方案需要重复单元设计。

-

常见问题

- 芯片引脚接反导致功能异常

- 未使用的输入端未做妥善处理(应接高/低电平)

- 电源去耦电容缺失引发信号抖动

平台实践体验

在InsCode(快马)平台上可以直接生成交互式电路仿真项目,无需安装Proteus等专业软件。我尝试上传设计后,系统自动生成了可视化的门电路连接图,还能实时修改输入值观察输出变化。

特别方便的是可以直接分享项目链接给同学协作,而且所有芯片资料都内置在平台里,不用反复查手册。对于数字电路课程设计来说,这种即开即用的体验确实能节省不少环境配置时间。

创作声明:本文部分内容由AI辅助生成(AIGC),仅供参考

6259

6259

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?