0 开始之前

从这篇博客起,记录一些DDR5 中涉及的特性和调试经验。

1 背景

本文提到DDR5 中的1N/2N 模式,这种模式似乎是为了 CA总线的时序问题。正如JESD79-5所述,2N 模式为DDR5 DRAM的CA总线提供更多时序裕量

JESD79-5B, chapter 4.34

2 配置方式

DDR5在上电时的初始配置为2N,通过修改MR2:OP[2]进行更改,修改的方式是使用2N的时序,发送MPC命令。

3 SPEC时序

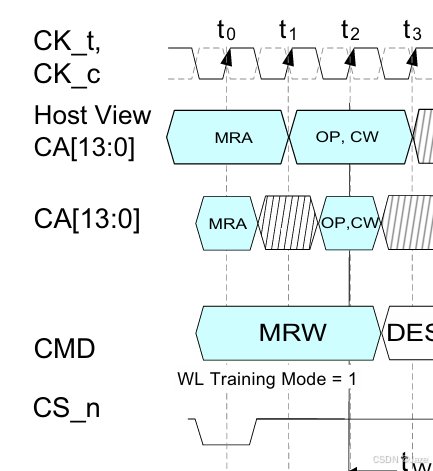

1N模式的传输:

JESD79-5B, Figure 101

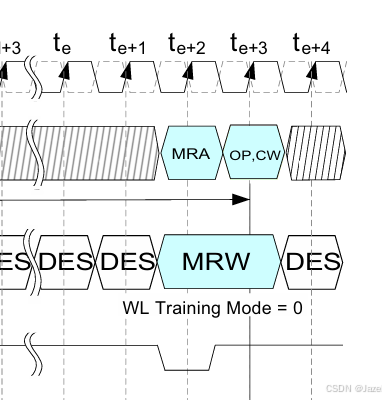

2N 模式的传输:

JESD79-5B, Figure 102

4 应用

设计DRAM Memory Controller时,

上电初始化时,使用CS/CA发送命令,应当是1个时钟的CS使能,搭配2个时钟的CA 数据。

JESD79-5B, JESD79-5C, JEDEC Standard of DDR5 SDRAM

695

695

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?