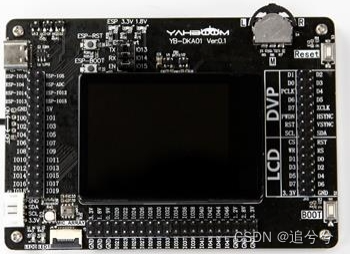

开发板

K210开发板

实验目的

本次测试主要学习 K210 芯片中快速傅立叶变换加速器的功能。

实验准备

实验元件

K210 芯片中的快速傅立叶变换加速器

元件特性

K210 内置快速傅立叶变换加速器 FFT Accelerater。FFT 加速器是用硬件的方式来实现 FFT 的基 2 时分运算。

- 支持多种运算长度,即支持 64 点、128 点、256 点以及 512 点运算

- 支持两种运算模式,即 FFT 以及 IFFT 运算

- 支持可配的输入数据位宽,即支持 32 位及 64 位输入

- 支持可配的输入数据排列方式,即支持虚部、实部交替,纯实部以及实部、虚部分离三种数据排列方式

- 支持 DMA 传输

SDK 中对应 API 功能

以头文件 aes.h为例

实验原理

目前该模块可以支持 64 点、128 点、256 点以及 512 点的 FFT 以及 IFFT。在 FFT 内部有两块大小为 512*32bit 的 SRAM,在配置完成后 FFT 会向 DMA 发送TX 请求,将 DMA 送来的送据放到其中的一块 SRAM 中去,直到满足当前 FFT 运算所需要的数据量并开始 FFT 运算,蝶形运算单元从包含有有效数据的 SRAM 中读出数据,运算结束后将数据写到另外一块 SRAM 中去,下次蝶形运算再从刚写入的 SRAM 中读出数据,运算结束后并写入另外一块 SRAM,如此反复交替进行直到完成整个 FFT 运算。

实验过程

- 首先通过三角函数取得一组复数。

K210开发板快速傅立叶变换加速器测试

K210开发板快速傅立叶变换加速器测试

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4283

4283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?